Order

Now

#### SBAS978-JUNE 2019

# ADS7028 Small, 8-Channel, 12-Bit ADC With SPI Interface, GPIOs, and CRC

Technical

Documents

### 1 Features

- Small package size:

- WQFN 3 mm × 3 mm

- 8 channels configurable as any combination of:

- Up to 8 analog inputs, digital inputs, or digital outputs

- GPIOs for I/O expansion:

- Open-drain, push-pull digital outputs

- Analog watchdog:

- Programmable thresholds per channel

- Event counter for transient rejection

- Wide operating ranges:

- AVDD: 2.35 V to 5.5 V

- DVDD: 1.65 V to 5.5 V

- -40°C to +85°C temperature range

- Enhanced-SPI digital interface:

- High-speed, 60-MHz interface

- Achieve full throughput with >13.5-MHz SPI

- CRC for read/write operation:

- CRC on data read/write

- CRC on power-up configuration

- Programmable averaging filters

- Root-mean-square module:

- 16-bit true RMS output

- Programmable RMS time window

- Zero-crossing-detect module:

- ZCD output corresponding to analog input

- Built-in transient rejection and hysteresis

- Digitally adjustable detection threshold

## 2 Applications

Tools &

Software

- Supervisory functions

- Portable instrumentation

- Appliances

- Telecommunication infrastructure

- Power-supply monitoring

## 3 Description

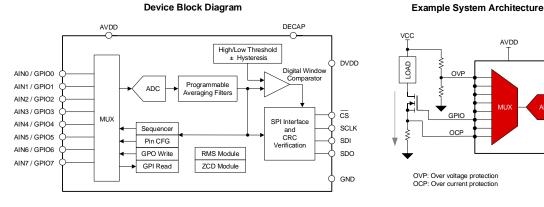

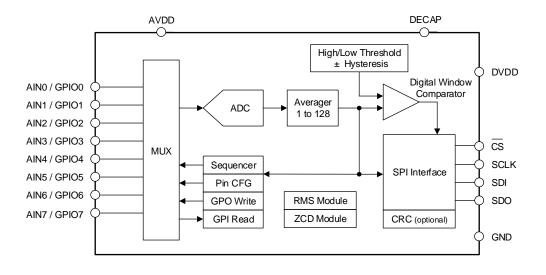

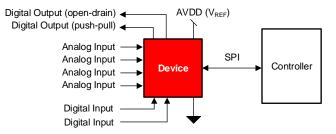

The ADS7028 is an easy-to-use, 8-channel, 12-bit. multiplexed, 1-MSPS. successive approximation register analog-to-digital converter (SAR ADC). The eight channels can be independently configured as either analog inputs, digital inputs, or digital outputs. The device has an internal oscillator for the ADC conversion process.

Support &

Community

2.0

The ADS7028 communicates via an SPI-compatible interface and operates in either autonomous or single-shot conversion mode. The ADS7028 implements the analog watchdog function by eventtriggered interrupts per channel using a digital window comparator with programmable high and low thresholds, hysteresis, and an event counter. The ADS7028 has a built-in cyclic redundancy check (CRC) for data read/write operations and the powerup configuration. The ADS7028 features a root-meansquare (RMS) module that computes a 16-bit true RMS result for any analog input channel. The integrated zero-crossing-detect (ZCD) module allows for transient rejection and hysteresis near the configurable threshold crossings.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| ADS7028     | WQFN (16) | 3.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

## ADS7028 Block Diagram and Applications

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. ADVANCE INFORMATION for pre-production products; subject to change without notice.

Texas Instruments

www.ti.com

## **Table of Contents**

| 1 | Features 1 |                                  |   |  |  |  |

|---|------------|----------------------------------|---|--|--|--|

| 2 | Арр        | Applications 1                   |   |  |  |  |

| 3 | Des        | cription                         | 1 |  |  |  |

| 4 | Rev        | ision History                    | 2 |  |  |  |

| 5 | Dev        | ice Comparison Table             | 3 |  |  |  |

| 6 | Pin        | Configuration and Functions      | 4 |  |  |  |

| 7 | Spe        | cifications                      | 5 |  |  |  |

|   | 7.1        | Absolute Maximum Ratings         | 5 |  |  |  |

|   | 7.2        | ESD Ratings                      | 5 |  |  |  |

|   | 7.3        | Recommended Operating Conditions | 5 |  |  |  |

|   | 7.4        | Thermal Information              | 5 |  |  |  |

|   | 7.5        | Electrical Characteristics       | 6 |  |  |  |

|   | 7.6        | Timing Requirements              | 6 |  |  |  |

|   | 7.7        | Switching Characteristics        | 7 |  |  |  |

| 8 | Deta       | ailed Description                | 9 |  |  |  |

|   | 8.1        | Overview                         | 9 |  |  |  |

|   | 8.2        | Functional Block Diagram         | 9 |  |  |  |

|   | 8.3        | Feature Description 1            | 0 |  |  |  |

|   |            |                                  |   |  |  |  |

|    | 8.4  | Device Functional Modes                         | 21 |

|----|------|-------------------------------------------------|----|

|    | 8.5  | ADS7028 Registers                               | 25 |

| 9  | App  | lication and Implementation                     | 69 |

|    | 9.1  | Application Information                         | 69 |

|    | 9.2  | Typical Applications                            | 69 |

| 10 | Pow  | ver Supply Recommendations                      | 71 |

|    | 10.1 | AVDD and DVDD Supply Recommendations            | 71 |

| 11 | Lay  | out                                             | 72 |

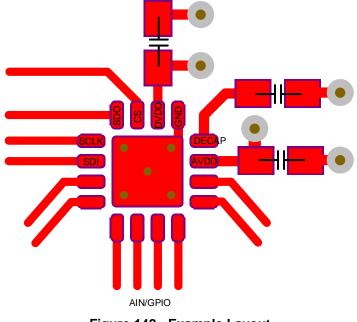

|    | 11.1 | Layout Guidelines                               | 72 |

|    | 11.2 | Layout Example                                  | 72 |

| 12 | Dev  | ice and Documentation Support                   | 73 |

|    | 12.1 | Receiving Notification of Documentation Updates | 73 |

|    | 12.2 | Community Resources                             | 73 |

|    | 12.3 | Trademarks                                      | 73 |

|    | 12.4 | Electrostatic Discharge Caution                 | 73 |

|    | 12.5 | Glossary                                        | 73 |

| 13 | Мес  | hanical, Packaging, and Orderable               |    |

|    | Info | rmation                                         | 73 |

|    |      |                                                 |    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE      | REVISION | NOTES            |

|-----------|----------|------------------|

| June 2019 | *        | Initial release. |

# 5 Device Comparison Table

| PART<br>NUMBER | DESCRIPTION                                           | CRC MODULE | ZERO-CROSSING-DETECT<br>(ZCD) MODULE | ROOT-MEAN-SQUARE<br>(RMS) MODULE |

|----------------|-------------------------------------------------------|------------|--------------------------------------|----------------------------------|

| ADS7028        | 8-channel, 12-bit ADC with SPI<br>interface and GPIOs | Yes        | Yes                                  | Yes                              |

| ADS7038        |                                                       | Yes        | No                                   | No                               |

| ADS7038-Q1     |                                                       | Yes        | No                                   | No                               |

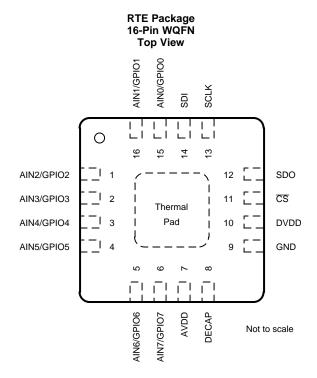

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN        |    | FUNCTION <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                        |  |  |  |  |

|------------|----|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME NO.   |    | FUNCTION                | DESCRIPTION                                                                                                                                                                                                                                        |  |  |  |  |

| AIN0/GPIO0 | 15 | AI, DI, DO              | Channel 0; can be configured as either an analog input (default), digital input, or digital output.                                                                                                                                                |  |  |  |  |

| AIN1/GPIO1 | 16 | AI, DI, DO              | Channel 1; can be configured as either an analog input (default), digital input, or digital output.                                                                                                                                                |  |  |  |  |

| AIN2/GPIO2 | 1  | AI, DI, DO              | Channel 2; can be configured as either an analog input (default), digital input, or digital output.                                                                                                                                                |  |  |  |  |

| AIN3/GPIO3 | 2  | AI, DI, DO              | Channel 3; can be configured as either an analog input (default), digital input, or digital output.                                                                                                                                                |  |  |  |  |

| AIN4/GPIO4 | 3  | AI, DI, DO              | Channel 4; can be configured as either an analog input (default), digital input, or digital output.                                                                                                                                                |  |  |  |  |

| AIN5/GPIO5 | 4  | AI, DI, DO              | Channel 5; can be configured as either an analog input (default), digital input, or digital output.                                                                                                                                                |  |  |  |  |

| AIN6/GPIO6 | 5  | AI, DI, DO              | Channel 6; can be configured as either an analog input (default), digital input, or digital outp                                                                                                                                                   |  |  |  |  |

| AIN7/GPIO7 | 6  | AI, DI, DO              | Channel 7; can be configured as either an analog input (default), digital input, or digital output                                                                                                                                                 |  |  |  |  |

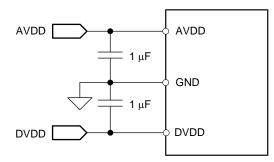

| AVDD       | 7  | Supply                  | Analog supply input, also used as the reference voltage to the ADC; connect a $1-\mu F$ decoupling capacitor to GND.                                                                                                                               |  |  |  |  |

| CS         | 11 | DI                      | Chip-select input pin; active low. The device takes control of the data bus when $\overline{CS}$ is low. The device starts converting the active input channel on the rising edge of $\overline{CS}$ . SDO goes hi-Z when $\overline{CS}$ is high. |  |  |  |  |

| DECAP      | 8  | Supply                  | Connect a decoupling capacitor to this pin for the internal power supply.                                                                                                                                                                          |  |  |  |  |

| DVDD       | 10 | Supply                  | Digital I/O supply voltage; connect a 1-µF decoupling capacitor to GND.                                                                                                                                                                            |  |  |  |  |

| GND        | 9  | Supply                  | Ground for the power supply; all analog and digital signals are referred to this pin voltage.                                                                                                                                                      |  |  |  |  |

| SCLK       | 13 | DI                      | Serial clock for the SPI interface.                                                                                                                                                                                                                |  |  |  |  |

| SDI        | 14 | DI                      | Serial data in for the device.                                                                                                                                                                                                                     |  |  |  |  |

| SDO        | 12 | DO                      | Serial data out for the device.                                                                                                                                                                                                                    |  |  |  |  |

(1) AI = analog input, DI = digital input, and DO = digital output.

#### ADS7028 SBAS978 – JUNE 2019

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                           | MIN       | MAX        | UNIT |

|-----------------------------------------------------------|-----------|------------|------|

| DVDD to GND                                               | -0.3      | 5.5        | V    |

| AVDD to GND                                               | -0.3      | 5.5        | V    |

| AINx / GPOx <sup>(2)</sup> to GND                         | GND – 0.3 | AVDD + 0.3 | V    |

| Digital input to GND                                      | GND – 0.3 | 5.5        | V    |

| Current through any pin except supply pins <sup>(3)</sup> | -10       | 10         | mA   |

| Junction temperature, T <sub>J</sub>                      | -40       | 125        | °C   |

| Storage temperature, T <sub>stg</sub>                     | -60       | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) AINx / GPIOx refers to pins 1, 2, 3, 4, 5, 6, 15, and 16.

(3) Pin current must be limited to 10mA or less.

## 7.2 ESD Ratings

|                    |                         |                                                                                          | VALUE         | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|---------------|------|

|                    | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000<br>±500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> |               | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                 | PARAMETER              | TEST CONDITIONS        | MIN  | TYP | MAX        | UNIT |

|-----------------|------------------------|------------------------|------|-----|------------|------|

| POWER SUPPLY    |                        |                        |      |     |            |      |

| AVDD            | Analog supply voltage  |                        | 2.35 | 3.3 | 5.5        | V    |

| DVDD            | Digital supply voltage |                        | 1.65 | 3.3 | 5.5        | V    |

| ANALO           | GINPUTS                |                        |      |     |            |      |

| FSR             | Full-scale input range | AIN <sub>X</sub> - GND | 0    |     | AVDD       | V    |

| V <sub>IN</sub> | Absolute input voltage | AIN <sub>X</sub> - GND | -0.1 |     | AVDD + 0.1 | V    |

| TEMPE           | RATURE RANGE           |                        |      |     |            |      |

| T <sub>A</sub>  | Ambient temperature    |                        | -40  | 25  | 85         | °C   |

(1) AINx refers to AIN0, AIN1, AIN2, AIN3, AIN4, AIN5, AIN6, and AIN7.

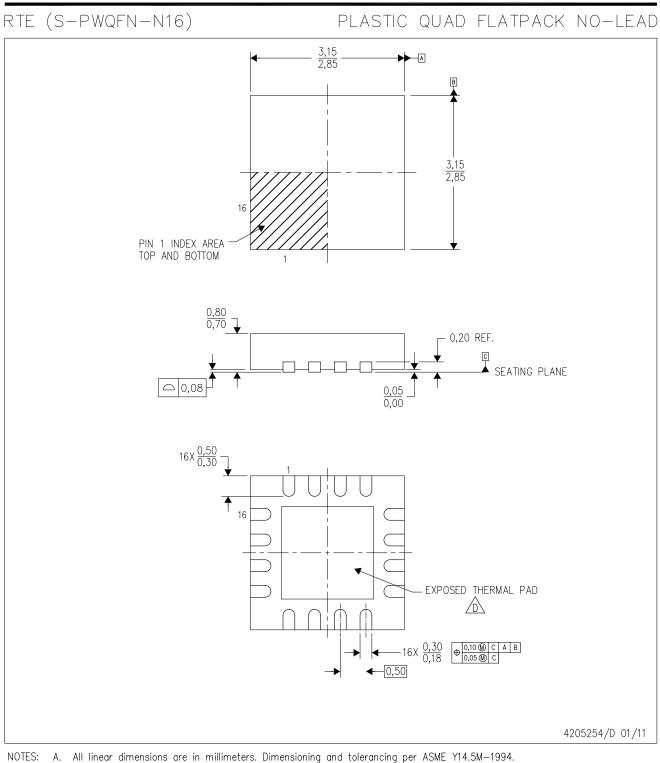

#### 7.4 Thermal Information

|                               |                                              | ADS7028    |      |

|-------------------------------|----------------------------------------------|------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | RTE (WQFN) | UNIT |

|                               |                                              | 16 PINS    |      |

| $R_{	hetaJA}$                 | Junction-to-ambient thermal resistance       | 49.7       | °C/W |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 53.4       | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 24.7       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 1.3        | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 24.7       | °C/W |

| R <sub>0JC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 9.3        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

EXAS

### 7.5 Electrical Characteristics

at AVDD = 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to +85°C; typical values at  $T_A = 25^{\circ}$ C

|                   | PARAMETER                          | TEST CONDITIONS                                     | MIN        | TYP   | MAX        | UNIT   |

|-------------------|------------------------------------|-----------------------------------------------------|------------|-------|------------|--------|

| ANALO             | G INPUTS                           |                                                     |            |       |            |        |

| C <sub>SH</sub>   | Sampling capacitance               |                                                     |            | 12    |            | pF     |

| DC PEF            | FORMANCE                           |                                                     | u.         |       |            |        |

|                   | Resolution                         | No missing codes                                    |            | 12    |            | bits   |

| DNL               | Differential nonlinearity          |                                                     | -0.9       | ±0.2  | 0.9        | LSB    |

| INL               | Integral nonlinearity              |                                                     | -2         | ±0.5  | 2          | LSB    |

| V <sub>(OS)</sub> | Input offset error                 | Post offset calibration                             | -2         | ±0.3  | 2          | LSB    |

|                   | Input offset thermal drift         | Post offset calibration                             |            | ±5    |            | ppm/°C |

| G <sub>E</sub>    | Gain error                         |                                                     | -0.1       | ±0.05 | 0.1        | %FSR   |

|                   | Gain error thermal drift           |                                                     |            | ±5    |            | ppm/°C |

| AC PER            | FORMANCE                           |                                                     |            |       |            |        |

| SINAD             | Signal to point a distortion ratio | $AVDD = 5 V, f_{IN} = 2 kHz$                        | 68.5       | 71.5  |            | dD     |

| SINAD             | Signal-to-noise + distortion ratio | $AVDD = 3 V, f_{IN} = 2 kHz$                        | 67.5       | 70.5  |            | dB     |

| SNR               | Signal-to-noise ratio              | $AVDD = 5 V, f_{IN} = 2 kHz$                        | 69         | 72    |            | dB     |

| SINK              |                                    | $AVDD = 3 V, f_{IN} = 2 kHz$                        | 68         | 71    |            | uБ     |

|                   | Isolation crosstalk                | f <sub>IN</sub> = 100 kHz                           |            | -100  |            | dB     |

| DECAP             | Pin                                |                                                     |            |       |            |        |

|                   | Decoupling capacitor on DECAP      |                                                     | 0.1        | 1     |            | μF     |

|                   | pin                                |                                                     |            |       |            | P      |

|                   | ERFACE (CS, SCLK, SDI, SDO)        |                                                     |            |       |            |        |

| V <sub>IH</sub>   | Input high logic level             |                                                     | 0.7 x DVDD |       | 5.5        | V      |

| V <sub>IL</sub>   | Input low logic level              |                                                     | -0.3       |       | 0.3 x DVDD | V      |

| V <sub>OH</sub>   | Output high logic level            | Source current = 2 mA,<br>DVDD > 2 V                | 0.8 x DVDD |       | DVDD       | v      |

| VОН               |                                    | Source current = 2 mA,<br>DVDD $\leq$ 2 V           | 0.7 x DVDD |       | DVDD       | v      |

| V                 |                                    | Sink current = 2 mA, DVDD > 2 V                     | 0          |       | 0.4        | v      |

| V <sub>OL</sub>   | Output low logic level             | Sink current = 2 mA, DVDD $\leq$ 2 V                | 0          |       | 0.2 x DVDD | v      |

| GPIOs             |                                    |                                                     |            |       |            |        |

| VIH               | Input high logic level             |                                                     | 0.7 x AVDD |       | AVDD + 0.3 | V      |

| V <sub>IL</sub>   | Input low logic level              |                                                     | -0.3       |       | 0.3 x AVDD | V      |

|                   | Input leakge current               | GPIO configured as input                            |            | 10    | 100        | nA     |

| V <sub>OH</sub>   | Output high logic level            | $GPO_DRIVE_CFG = push-pull,$<br>$I_{SOURCE} = 2 mA$ | 0.8 x AVDD |       | AVDD       | V      |

| V <sub>OL</sub>   | Output low logic level             | I <sub>SINK</sub> = 2 mA                            | 0          |       | 0.2 x AVDD | V      |

| I <sub>OH</sub>   | Output high source current         | V <sub>OH</sub> > 0.7 x AVDD                        |            |       | 5          | mA     |

| I <sub>OL</sub>   | Output low sink current            | V <sub>OL</sub> < 0.3 x AVDD                        |            |       | 5          | mA     |

|                   | R-SUPPLY CURRENTS                  |                                                     | ·          |       |            |        |

|                   |                                    | Full throughput, AVDD = 5 V                         |            |       | 2.66       |        |

| I <sub>AVDD</sub> | Analog supply current              | Full throughput, AVDD = 3 V                         |            |       | 1.56       | mA     |

|                   |                                    | No conversion, AVDD = 5 V                           |            | 0.03  | 0.05       | 1      |

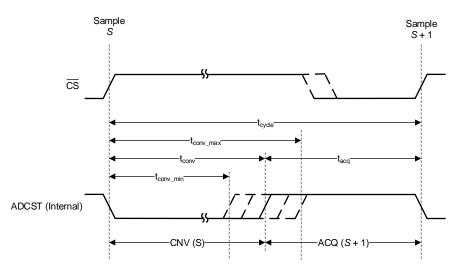

### 7.6 Timing Requirements

at AVDD = 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to +85°C; typical values at  $T_A = 25^{\circ}$ C

|                  | MIN | MAX | UNIT |

|------------------|-----|-----|------|

| CONVERSION CYCLE |     |     |      |

6 Submit Documentation Feedback

#### **Timing Requirements (continued)**

at AVDD = 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to +85°C; typical values at  $T_A = 25^{\circ}$ C

|                       |                                                         | MIN                    | MAX  | UNIT             |

|-----------------------|---------------------------------------------------------|------------------------|------|------------------|

| f <sub>CYCLE</sub>    | Sampling frequency                                      |                        | 1000 | kSPS             |

| t <sub>CYCLE</sub>    | ADC cycle-time period                                   | 1 / f <sub>CYCLE</sub> |      | S                |

| t <sub>ACQ</sub>      | Acquisition time                                        | 300                    |      | ns               |

| t <sub>QT_ACQ</sub>   | Quiet acquisition time                                  | 10                     |      | ns               |

| t <sub>D_CNVCAP</sub> | Quiet conversion time                                   | 10                     |      | ns               |

| t <sub>WH_CSZ</sub>   | Pulse duration: CS high                                 | 10                     |      | ns               |

| t <sub>WL_CSZ</sub>   | Pulse duration: CS low                                  | 10                     |      | ns               |

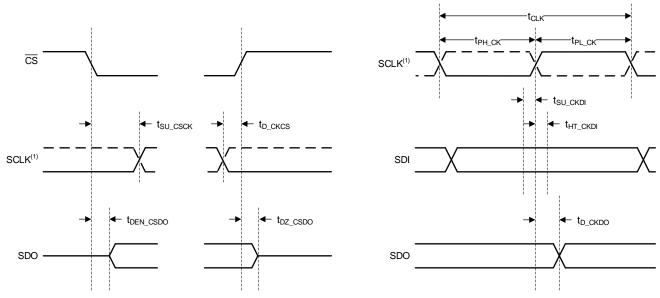

| SPI INTERF            | ACE TIMINGS                                             |                        |      |                  |

| f <sub>CLK</sub>      | Maximum SCLK frequency                                  |                        | 60   | MHz              |

| t <sub>CLK</sub>      | Minimum SCLK time period                                | 16.67                  |      | ns               |

| t <sub>PH_CK</sub>    | SCLK high time                                          | 0.45                   | 0.55 | t <sub>CLK</sub> |

| t <sub>PL_CK</sub>    | SCLK low time                                           | 0.45                   | 0.55 | t <sub>CLK</sub> |

| t <sub>SU_CSCK</sub>  | Setup time: CS falling to the first SCLK capture edge   | 5                      |      | ns               |

| t <sub>SU_CKDI</sub>  | Setup time: SDI data valid to the SCLK capture edge     | 1.2                    |      | ns               |

| t <sub>HT_CKDI</sub>  | Hold time: SCLK capture edge to data valid on SDI       | 0.65                   |      | ns               |

| t <sub>D_CKCS</sub>   | Delay time: last SCLK falling to $\overline{CS}$ rising | 5                      |      | ns               |

### 7.7 Switching Characteristics

at AVDD = 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to +85°C; typical values at  $T_A = 25^{\circ}$ C

|                       | PARAMETER                                                  | Test Conditions                                 | MIN MAX | UNIT |

|-----------------------|------------------------------------------------------------|-------------------------------------------------|---------|------|

| CONVERSIO             | ON CYCLE                                                   |                                                 |         |      |

| t <sub>CONV</sub>     | ADC conversion time                                        |                                                 | 600     | ns   |

| t <sub>ACQ</sub>      | Acquisition time                                           |                                                 | 400     | ns   |

| <b>RESET</b> and      | ALERT                                                      | · · ·                                           |         |      |

| t <sub>PU</sub>       | Power-up time for device                                   | AVDD $\ge 2.35$ V,<br>C <sub>DECAP</sub> = 1 µF | 5       | ms   |

| t <sub>RST</sub>      | Delay time; RST bit = 1b to device reset complete $^{(1)}$ |                                                 | 5       | ms   |

| t <sub>ALERT_HI</sub> | ALERT high period                                          | ALERT_LOGIC[1:0]<br>= 1x                        | 85 105  | ns   |

| t <sub>ALERT_LO</sub> | ALERT low period                                           | ALERT_LOGIC[1:0]<br>= 1x                        | 85 105  | ns   |

| SPI INTERF            | ACE TIMINGS                                                | · · ·                                           |         |      |

| t <sub>DEN_CSDO</sub> | Delay time: $\overline{CS}$ falling to data enable         |                                                 | 15      | ns   |

| t <sub>DZ_CSDO</sub>  | Delay time: CS rising to SDO going Hi-Z                    |                                                 | 15      | ns   |

| t <sub>D_CKDO</sub>   | Delay time: SCLK launch edge to (next) data valid on SDO   |                                                 | 15      | ns   |

(1) RST bit is automatically reset to 0b after  $t_{\mbox{\scriptsize RST}}.$

(1) The SCLK polarity, launch edge, and capture edge depend on the SPI protocol selected.

#### Detailed Description 8

#### Overview 8.1

The ADS7028 is a small, eight-channel, multiplexed, 12-bit, 1-MSPS, analog-to-digital converter (ADC) with an enhanced-SPI serial interface. The eight channels of the ADS7028 can be individually configured as either analog inputs, digital inputs, or digital outputs. The device includes a digital comparator which can be used to interrupt the host when a programmed high or low threshold is crossed on any input channel. The device uses an internal oscillator for conversion. The ADC can be used in manual mode for reading ADC data over the SPI interface or in autonomous mode for monitoring the analog inputs without an active SPI interface.

The device features a programmable averaging filter that outputs a 16-bit result for enhanced resolution. The root-mean-square (RMS) module computes a 16-bit true RMS result of any analog input channel over a configurable time window. The zero-crossing-detect (ZCD) module can be used to generate a digital output corresponding to the programmable threshold crossings of any analog input channel.

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Multiplexer and ADC

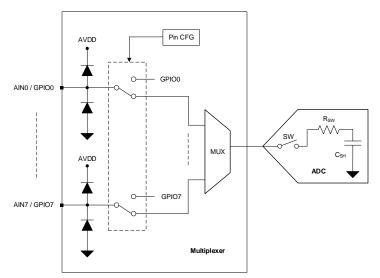

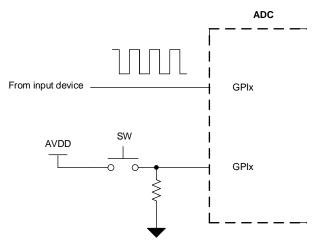

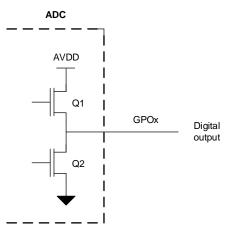

The eight channels of the multiplexer can be independently configured as ADC inputs or general-purpose inputs/outputs (GPIOs). Figure 3 shows that each input pin has ESD protection diodes to AVDD and GND. On power-up or after device reset, all eight multiplexer channels are configured as analog inputs.

Figure 3 shows an equivalent circuit for pins configured as analog inputs. The ADC sampling switch is represented by ideal switch (SW) in series with the resistor  $R_{SW}$  (typically 150  $\Omega$ ) and the sampling capacitor,  $C_{SH}$  (typically 12 pF).

Figure 3. Analog Inputs, GPIOs, and ADC Connections

During acquisition, the SW switch is closed to allow the signal on the selected analog input channel to charge the internal sampling capacitor. During conversion, the SW switch is opened to disconnect the analog input channel from the sampling capacitor.

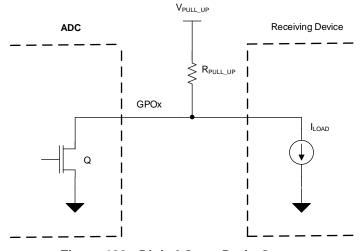

The multiplexer channels can be configured as GPIOs in the PIN\_CFG register. The direction of a GPIO (either as an input or an output) can be set in the GPIO\_CFG register. The logic level on the channels configured as digital inputs can be read from the GPI\_VALUE register. The digital outputs can be accessed by writing to the GPO\_OUTPUT\_VALUE register. The digital outputs can be configured as either open-drain or push-pull in the GPO\_DRIVE\_CFG register.

#### 8.3.2 Reference

The device uses the analog supply voltage (AVDD) as a reference for the analog-to-digital conversion process. TI recommends connecting a  $1-\mu F$ , low-equivalent series resistance (ESR) ceramic decoupling capacitor between the AVDD and GND pins.

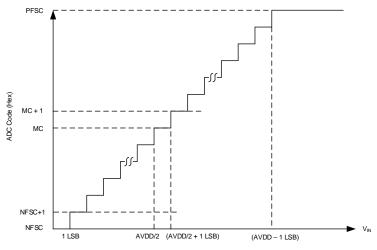

#### 8.3.3 ADC Transfer Function

The ADC output is in straight binary format. Equation 1 computes the ADC resolution:

$$1 \text{ LSB} = \text{V}_{\text{REF}} / 2^{\text{N}}$$

where:

- V<sub>REF</sub> = AVDD

- N = 12

(1)

#### Feature Description (continued)

Figure 4 and Table 1 detail the transfer characteristics for the device.

Figure 4. Ideal Transfer Characteristics

| Table 1. | Transfer | Characteristics |

|----------|----------|-----------------|

|          | manorer  | onaraotoristios |

| INPUT VOLTAGE FOR SINGLE-ENDED INPUT     | CODE     | DESCRIPTION              | IDEAL OUTPUT<br>CODE |

|------------------------------------------|----------|--------------------------|----------------------|

| ≤1 LSB                                   | NFSC     | Negative full-scale code | 000                  |

| 1 LSB to 2 LSBs                          | NFSC + 1 | _                        | 001                  |

| (AVDD / 2) to (AVDD / 2) + 1 LSB         | MC       | Mid code                 | 800                  |

| (AVDD / 2) + 1 LSB to (AVDD / 2) + 2 LSB | MC + 1   | _                        | 801                  |

| ≥ AVDD – 1 LSB                           | PFSC     | Positive full-scale code | FFF                  |

### 8.3.4 ADC Offset Calibration

The variation in ADC offset error resulting from changes in temperature or AVDD can be calibrated by setting the CAL bit in the GENERAL\_CFG register. The CAL bit is reset to 0 after calibration. The host can poll the CAL bit to check the ADC offset calibration completion status.

(2)

INSTRUMENTS

**EXAS**

#### 8.3.5 Programmable Averaging Filter

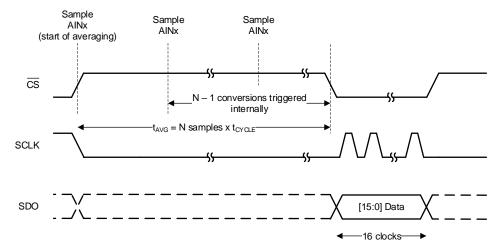

The ADS7028 features a built-in oversampling (OSR) function that can be used to average several samples. The averaging filter can be enabled by programming the OSR[2:0] bits in the OSR\_CFG register. The averaging filter configuration is common to all analog input channels. Figure 5 shows that the averaging filter module output is 16 bits long. In manual conversion mode and auto-sequence mode, only the first conversion for the selected analog input channel must be initiated by the host; see the *Manual Mode* and *Auto-Sequence Mode* sections. As shown in Figure 5, any remaining conversions for the selected averaging factor are generated internally. The time required to complete the averaging operation is determined by the sampling speed and number of samples to be averaged. As shown in Figure 5, the 16-bit result can be read out after the averaging operation completes.

Figure 5. Averaging Example

In autonomous mode of operation, samples from analog input channels that are enabled in the AUTO\_SEQ\_CH\_SEL register are averaged sequentially. The digital window comparator compares the top 12 bits of the 16-bit average result with the thresholds.

Equation 2 provides the LSB value of the 16-bit average result.

$$1 LSB = \frac{AVDD}{2^{16}}$$

#### 8.3.6 CRC on Data Interface

The ADS7028 features a cyclic redundancy check (CRC) module for checking the integrity of the data bits exchanged over the SPI interface. The CRC module is bidirectional, which appends an 8-bit CRC to every byte read from the device and also evaluates the CRC of every incoming byte over the SPI interface. The CRC module uses the CRC-8-CCITT polynomial ( $x^8 + x^2 + x + 1$ ) for CRC computation.

To enable the CRC module, set the CRC\_EN bit in the GENERAL\_CFG register. Table 2 shows the different ways that a CRC error that occurs when configuring the ADS7028 can be detected.

| CRC ERROR NOTIFICATION | CONFIGURATION       | DESCRIPTION                                                                                                       |

|------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------|

| ALERT                  | $ALERT_CRCIN = 1b$  | ALERT (internal signal) is asserted if a CRC error is detected                                                    |

| Status flags           | APPEND_STATUS = 10b | 4-bit status flags are appended to the ADC data. See the <i>Output Data</i><br><i>Format</i> section for details. |

| Register read          | _                   | Read the CRCERR_IN bit to check if a CRC error was detected.                                                      |

When the ADS7028 detects a CRC error on the SPI interface, the erroneous data are ignored and the CRCERR\_IN bit is set. Additional notifications can be enabled as described in Table 2. Further register writes are disabled until the CRCERR\_IN bit is cleared by writing 1b to this bit. When using autonomous conversion mode, further conversions can be disabled on a CRC error on the SPI interface by setting CONV\_ON\_ERR = 1b.

#### 8.3.7 General-Purpose I/Os

The eight channels of the ADS7028 can be independently configured as analog inputs, digital inputs, or digital outputs. Table 3 shows how the PIN\_CFG and GPIO\_CFG registers can be used to configure the device channels.

| PIN_CFG[7:0] | GPIO_CFG[7:0] | GPO_DRIVE_CFG[7:0] | CHANNEL CONFIGURATION             |

|--------------|---------------|--------------------|-----------------------------------|

| 0            | х             | x                  | Analog input (default)            |

| 1            | 0             | x                  | Digital input                     |

| 1            | 1             | 0                  | Digital output; open-drain driver |

| 1            | 1             | 1                  | Digital output; push-pull driver  |

#### Table 3. Configuring Channels as Analog Inputs or GPIOs

Digital outputs can be configured to logic 1 or 0 by writing to the GPO\_OUTPUT\_VALUE register. Reading the GPI\_VALUE register returns the logic level for all channels configured as digital inputs or digital outputs. The GPI\_VALUE register can be read to detect a failure in external components, such as a floating pullup resistor or a low-impedance pulldown resistor, that prevents digital outputs being set to the desired logic level.

#### 8.3.8 Oscillator and Timing Control

The device uses an internal oscillator for conversion. When using the averaging module, the host initiates the first conversion and subsequent conversions are generated internally by the device. Also, in autonomous mode of operation, the start of the conversion signal is generated by the device. Table 4 describes how the sampling rate can be controlled by the OSC\_SEL and CLK\_DIV[3:0] register fields when the device generates the start of the conversion.

|              | OSC_SEL = 0                                      |                                        | OSC_SEL :                                        | = 1                                    |

|--------------|--------------------------------------------------|----------------------------------------|--------------------------------------------------|----------------------------------------|

| CLK_DIV[3:0] | SAMPLING FREQUENCY, f <sub>CYCLE</sub><br>(kSPS) | CYCLE TIME,<br>t <sub>CYCLE</sub> (µs) | SAMPLING FREQUENCY,<br>f <sub>CYCLE</sub> (kSPS) | CYCLE TIME, t <sub>CYCLE</sub><br>(µs) |

| 0000b        | 1000                                             | 1                                      | 31.25                                            | 32                                     |

| 0001b        | 666.7                                            | 1.5                                    | 20.83                                            | 48                                     |

| 0010b        | 500                                              | 2                                      | 15.63                                            | 64                                     |

| 0011b        | 333.3                                            | 3                                      | 10.42                                            | 96                                     |

| 0100b        | 250                                              | 4                                      | 7.81                                             | 128                                    |

| 0101b        | 166.7                                            | 6                                      | 5.21                                             | 192                                    |

| 0110b        | 125                                              | 8                                      | 3.91                                             | 256                                    |

| 0111b        | 83                                               | 12                                     | 2.60                                             | 384                                    |

| 1000b        | 62.5                                             | 16                                     | 1.95                                             | 512                                    |

| 1001b        | 41.7                                             | 24                                     | 1.3                                              | 768                                    |

| 1010b        | 31.3                                             | 32                                     | 0.98                                             | 1024                                   |

| 1011b        | 20.8                                             | 48                                     | 0.65                                             | 1536                                   |

| 1100b        | 15.6                                             | 64                                     | 0.49                                             | 2048                                   |

| 1101b        | 10.4                                             | 96                                     | 0.33                                             | 3072                                   |

#### Table 4. Configuring Sampling Rate for Internal Conversion Start Control

The conversion time of the device, given by t<sub>CONV</sub> in the *Switching Characteristics* table, is independent of the OSC\_SEL and CLK\_DIV[3:0] configuration.

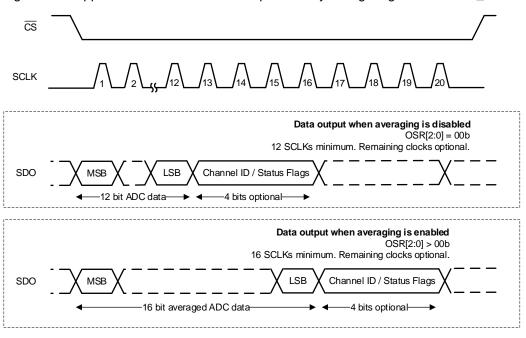

#### 8.3.9 Output Data Format

Figure 6 shows various SPI frames for reading data. The data output is MSB aligned. If averaging is enabled the output data from the ADC are 16 bits long, otherwise the output data are 12 bits long. Optionally, a 4-bit channel ID or status flags can be appended at the end of the output data by configuring the APPEND STATUS[1:0] field.

Figure 6. SPI Frames for Reading Data

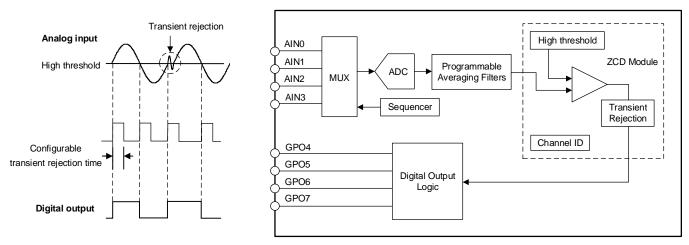

#### 8.3.10 Zero-Crossing-Detect Module

The zero-crossing-detect (ZCD) module generates a digital output corresponding to the designated analog input signal crossing a configured threshold. Figure 7 shows the digital output corresponding to the threshold crossings of an analog input. In order to detect the threshold crossings on a particular analog input, configure the 4-bit channel ID in the ZCD\_CHID register. The threshold crossing to be detected can be configured in the corresponding HIGH\_TH register. The output of the ZCD module can be connected to any digital output by configuring the ZCD\_TRIG\_EN and GPO\_VALUE\_ZCD registers.

The ADC conversion result of the selected analog input channel is compared with the digital threshold that then sets the digital output accordingly. Transients near zero crossings can be rejected, as calculated in Equation 3, by configuring the ZCD\_BLANKING register.

transient rejection time = MULT\_EN × ZCD\_BLANKING[6:0] ×  $\frac{1}{\text{sampling rate for ZCD channel}}$  seconds (3)

#### 8.3.11 Digital Window Comparator

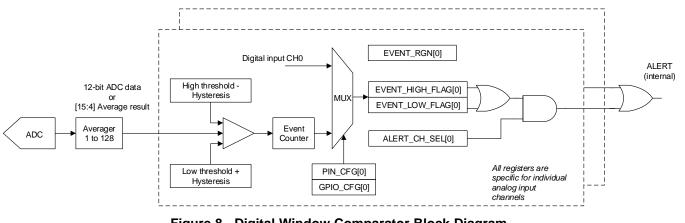

The internal digital window comparator (DWC) is available in both conversion modes (manual and autonomous). The DWC outputs an internal ALERT signal. The internal ALERT signal can be output on any one of the digital output channels by configuring the ALERT\_PIN register. Figure 8 provides a block diagram for the digital window comparator.

Figure 8. Digital Window Comparator Block Diagram

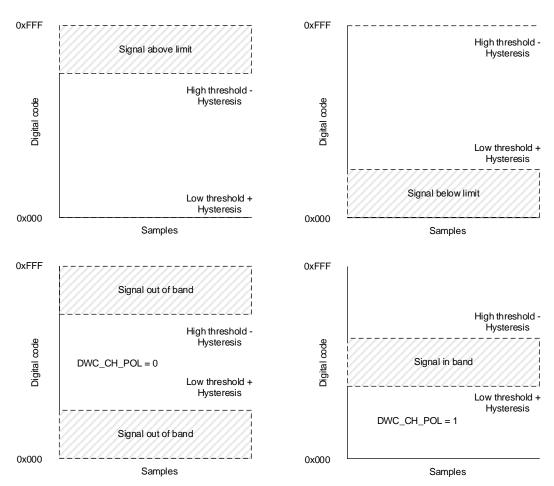

The low-side threshold, high-side threshold, event counter, and hysteresis parameters are independently programmable for each input channel. Figure 9 illustrates that the window comparator can monitor events for every analog input channel.

Texas Instruments

www.ti.com

Figure 9. Event Monitoring With the Window Comparator

To enable the digital window comparator, set the DWC\_EN bit in the GENERAL\_CFG register. By default, hysteresis = 0, high threshold = 0xFFF, and low threshold = 0x000. For detecting when a signal is in-band, the EVENT\_RGN register must be configured. In each of the cases shown in Figure 9, either or both ALERT\_HIGH\_FLAG and ALERT\_LOW\_FLAG can be set. The programmable event counter counts consecutive threshold violations before alert flags are set. The event count can be set to a higher value to avoid transients in the input signal setting the alert flags.

In order to assert the ALERT signal (internal) when the alert flag is set for a particular analog input channel, set the corresponding bit in the DWC\_CH\_SEL register. Alert flags are set, irrespective of the DWC\_CH\_SEL configuration, if DWC\_EN = 1 and high or low thresholds are exceeded.

#### 8.3.11.1 Interrupts From Digital Inputs

Table 5 shows that rising edge or falling edge events can be detected on channels configured as digital inputs.

| PIN_CFG[7:0] | GPIO_CFG[7:0] | EVENT_RGN[7:0] | EVENT DESCRIPTION                                                         |

|--------------|---------------|----------------|---------------------------------------------------------------------------|

| 1            | 0             | 0              | ALERT_HIGH_FLAG is set on the rising edge on the digital input<br>channel |

| 1            | 0             | 1              | ALERT_LOW_FLAG is set on the falling edge on the digital input<br>channel |

**Table 5. Configuring Interrupts From Digital Inputs**

ADVANCE INFORMATION

#### 8.3.11.2 Triggering Digital Outputs With Alert and ZCD

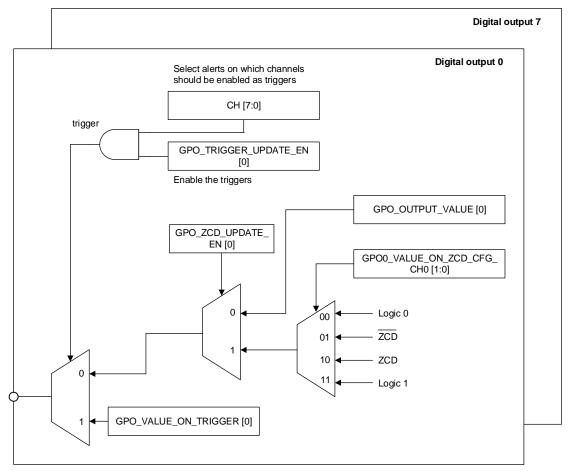

Figure 10 shows that digital outputs can be updated in response to alerts from individual channels or synchronous to the zero-crossing-detect signal.

Figure 10. Block Diagram of the Digital Output Logic

#### 8.3.11.2.1 Triggering Digital Outputs on Alerts

Any given digital output can be updated in response to an alert condition on one or more analog inputs and digital inputs. To update the digital output in response to alert conditions, configure the trigger and the value to be launched when the trigger occurs.

#### 8.3.11.2.1.1 Trigger

The following events can act as triggers for updating the value on the digital output:

- An alert on one or more analog input channels. The digital window comparator must be enabled for these channels.

- An alert on one or more digital input channels. The digital window comparator must be enabled for these channels.

Configure the GPOx\_TRIG\_EVENT\_SEL register to select which channels, analog inputs, or digital inputs can trigger an update on the digital output pin. After configuring the triggers for updating a digital output, the logic can be enabled by configuring the corresponding bit in the GPO\_TRIGGER\_UPDATE\_EN register.

#### 8.3.11.2.1.2 Output Value

The digital outputs can be set to logic 1 or logic 0 in response to triggers. The value to be updated on the digital output when a trigger event occurs can be configured in the GPO\_VALUE\_ON\_TRIGGER register.

Copyright © 2019, Texas Instruments Incorporated

(5)

#### 8.3.11.2.2 Changing Digital Outputs Synchronous to ZCD

Individual digital outputs can be set to either logic 0, logic 1, ZCD, or ZCD synchronous to the zero-crossingdetect signal. This function can be enabled for individual digital outputs by configuring the GPO\_VALUE\_ON\_ZCD\_CFG\_CHx field and setting the corresponding bit in the GPO\_ZCD\_UPDATE\_EN [7:0] register. See the *Zero-Crossing-Detect Module* section for details about the operation of ZCD module and Figure 10 for a block diagram detailing controlling the digital outputs with the ZCD signal.

#### 8.3.12 Root-Mean-Square Module

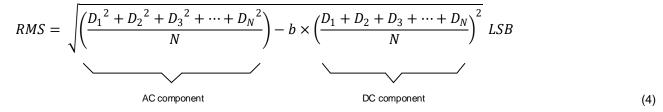

In the ADS7028, any one analog input channel can be selected for computing the RMS result. The RMS result is computed over a block of samples from the selected channel and result can be read from the RMS\_RESULT\_LSB and RMS\_RESULT\_MSB registers. As shown in Equation 4, compute the RMS result with the 16-bit square root mean of the accumulated result of the squares of the ADC conversion data.

In Equation 4, D is the data corresponding to the analog input channel selected for RMS measurement and N is the number of samples over which RMS is computed. The DC offset must be subtracted from the AC component because the analog input signal to the ADC is unipolar. DC subtraction can be enabled or disabled, given by b in Equation 4, by configuring the DC\_SUB field. The size of a 1-LSB RMS result is given in Equation 5 and the RMS result is 16 bits long.

1 LSB = AVDD / 2<sup>16</sup>

The procedure for using the RMS module is outlined in the steps below:

- 1. Select the channel for RMS computation using the RMS\_CHID field in the RMS\_CFG register.

- 2. Define the time over which RMS is to be computed by configuring the RMS\_SAMPLES field.

- 3. Start RMS computation by setting RMS\_EN = 1 in the GENERAL\_CFG register.

- 4. The RMS result is ready when the sample size defined by RMS\_SAMPLES has been converted on the analog input channel selected for RMS computation.

- To monitor for completion of the RMS computation, poll the RMS\_DONE bit in the SYSTEM\_STATUS register. The ALERT pin can also be used for requesting an interrupt by configuring the ALERT\_RMS bit in the ALERT\_MAP register.

- 6. For starting a new RMS measurement, write 1 to the RMS\_EN bit in the GENERAL\_CFG register.

#### 8.3.13 Minimum, Maximum, and Latest Data Registers

The ADS7028 can record the minimum, maximum, and latest code (statistics registers) for every analog input channel. To enable or re-enable recording statistics, set the STATS\_EN bit in the GENERAL\_CFG register. Writing 1 to the STATS\_EN bit reinitializes the statistics module. Afterwards, results from new conversions are recorded in the statistics registers.. Previous values can be read from the statistics registers until a new conversion result is available. Before reading the statistics registers, set STATS\_EN = 0 to prevent any updates to this block of registers.

#### 8.3.14 Device Programming

#### 8.3.14.1 Enhanced-SPI Interface

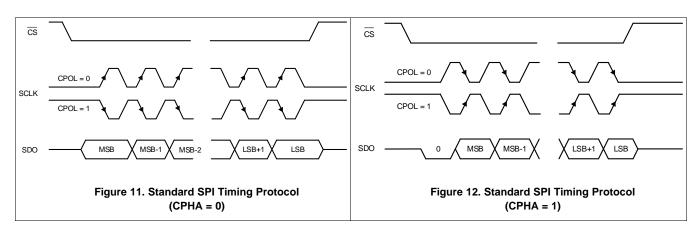

The device features an enhanced-SPI interface that allows the host controller to operate at slower SCLK speeds and still achieve full throughput. As described in Table 6, the host controller can use any of the four SPI-compatible protocols (SPI-00, SPI-01, SPI-10, or SPI-11) to access the device.

| PROTOCOL | SCLK POLARITY<br>(At the CS Falling Edge) | SCLK PHASE<br>(Capture Edge) | CPOL_CPHA[1:0] | DIAGRAM   |

|----------|-------------------------------------------|------------------------------|----------------|-----------|

| SPI-00   | Low                                       | Rising                       | 00b            | Figure 11 |

| SPI-01   | Low                                       | Falling                      | 01b            | Figure 12 |

| SPI-10   | High                                      | Falling                      | 10b            | Figure 11 |

| SPI-11   | High                                      | Rising                       | 11b            | Figure 12 |

#### Table 6. SPI Protocols for Configuring the Device

On power-up or after coming out of any asynchronous reset, the device supports the SPI-00 protocol for data read and data write operations. To select a different SPI-compatible protocol, program the CPOL\_CPHA[1:0] field. This first write operation must adhere to the SPI-00 protocol. Any subsequent data transfer frames must adhere to the newly-selected protocol.

#### 8.3.14.2 Register Read/Write Operation

The device supports the commands listed in Table 7 to access the internal configuration registers.

#### Table 7. Opcodes for Commands

| OPCODE     | COMMAND DESCRIPTION   |  |

|------------|-----------------------|--|

| 0000 0000b | No operation          |  |

| 0001 0000b | Single register read  |  |

| 0000 1000b | Single register write |  |

| 0001 1000b | Set bit               |  |

| 0010 0000b | Clear bit             |  |

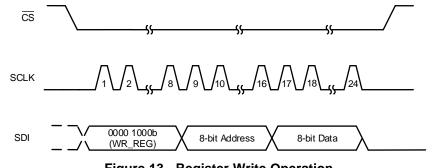

#### 8.3.14.2.1 Register Write

A 24-bit SPI frame is required for writing data to configuration registers. The 24-bit data on SDI, as shown in Figure 13. consists of an 8-bit write command (0000 1000b), an 8-bit register address, and 8-bit data. The write command is decoded on the CS rising edge and the specified register is updated with the 8-bit data specified during the register write operation.

Figure 13. Register Write Operation

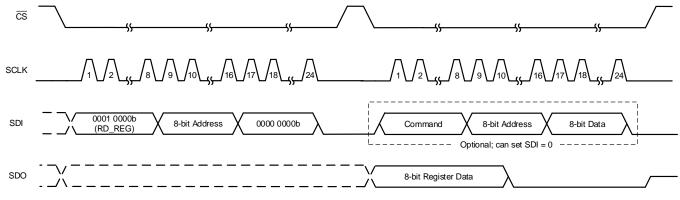

#### 8.3.14.2.2 Register Read

Register read operation consists of two SPI frames: the first SPI frame initiates a register read and the second SPI frame reads data from the register address provided in the first frame. As shown in Figure 14, the 8-bit register address and the 8-bit dummy data are sent over the SDI pin during the first 24-bit frame with the read command (0001 0000b). On the rising edge of  $\overline{CS}$ , the read command is decoded and the requested register data are available for reading during the next frame. During the second frame, the first eight bits on SDO correspond to the requested register read. During the second frame, SDI can be used to initiate another operation or can be set to 0.

Figure 14. Register Read Operation

#### 8.4 Device Functional Modes

Table 8 lists the functional modes supported by the ADS7028.

| FUNCTIONAL<br>MODE | CONVERSION CONTROL     | MUX CONTROL                                         | CONV_MODE[1:0] | SEQ_MODE[1:0] |

|--------------------|------------------------|-----------------------------------------------------|----------------|---------------|

| Manual             | CS rising edge         | Register write to MANUAL_CHID                       | 00b            | 00b           |

| On-the-fly         | CS rising edge         | First 5 bits after the $\overline{CS}$ falling edge | 00b            | 10b           |

| Auto-sequence      | CS rising edge         | Channel sequencer                                   | 00b            | 01b           |

| Autonomous         | Internal to the device | Channel sequencer                                   | 01b            | 01b           |

| Table 8. Functional Mode |

|--------------------------|

|--------------------------|

The device powers up in manual mode and can be configured into either of these modes by writing the configuration registers for the desired mode.

#### 8.4.1 Device Power-Up and Reset

On power-up, the BOR bit is set indicating a power-cycle or reset event. The device can be reset by setting the RST bit or by recycling the power on the AVDD pin.

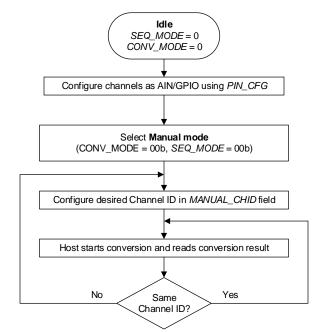

#### 8.4.2 Manual Mode

Manual mode allows the external host processor to directly select the analog input channel. Figure 15 shows the steps for operating the device in manual mode.

Figure 15. Device Operation in Manual Mode

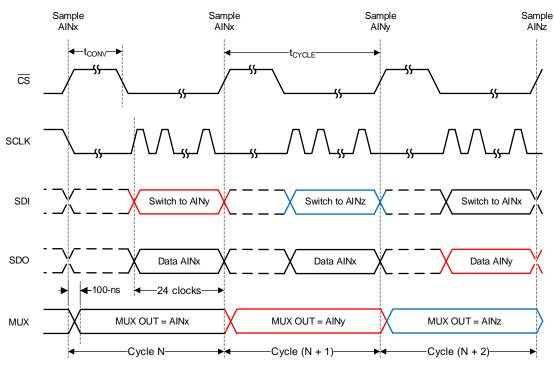

In manual mode, the command to switch to a new channel (indicated by cycle N in Figure 16) is decoded by the device on the CS rising edge. The CS rising edge is also the start of the conversion signal, and therefore the device samples the previously selected MUX channel in cycle N+1. The newly selected analog input channel data are available in cycle N+2. For switching the analog input channel, a register write to the MANUAL\_CHID field requires 24 clocks; see the *Register Write* section for more details. After a channel is selected, the number of clocks required for reading the output data depends on the device output data frame size; see the *Output Data Format* section for more details.

ADS7028 SBAS978 – JUNE 2019

INSTRUMENTS

Texas

Figure 16. Starting Conversions and Reading Data in Manual Mode

### 8.4.3 On-the-Fly Mode

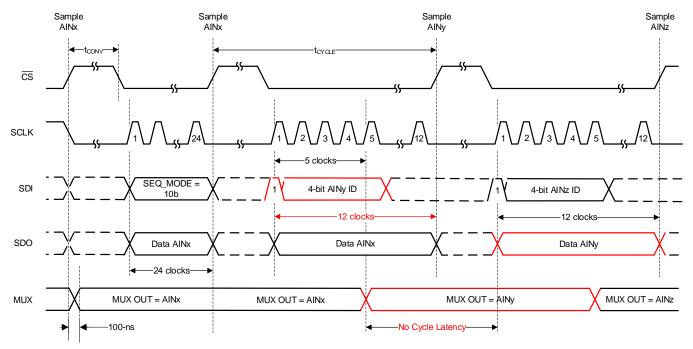

In the on-the-fly mode of operation, the analog input channel is selected, as shown in Figure 17, using the first five bits on SDI without waiting for the CS rising edge. Thus, the ADC samples the newly selected channel on the CS edge and there is no latency between the channel selection and the ADC output data.

The number of clocks required for reading the output data depends on the device output data frame size; see the *Output Data Format* section for more details.

#### 8.4.4 Auto-Sequence Mode

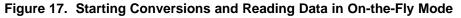

In auto-sequence mode, the internal channel sequencer switches the multiplexer to the next analog input channel after every conversion. The desired analog input channels can be configured for sequencing in the AUTO\_SEQ\_CHSEL register. To enable the channel sequencer, set SEQ\_START = 1b. After every conversion, the channel sequencer switches the multiplexer to the next analog input in ascending order. To stop the channel sequencer from selecting channels, set SEQ\_START = 0b.

In the example shown in Figure 18, AIN2 and AIN6 are enabled for sequencing in AUTO\_SEQ\_CHSEL. The channel sequencer loops through AIN2 and AIN6 and repeats until SEQ\_START is set to 0b. The number of clocks required for reading the output data depends on the device output data frame size; see the *Output Data Format* section for more details.

Figure 18. Starting Conversions and Reading Data in Auto-Sequence Mode

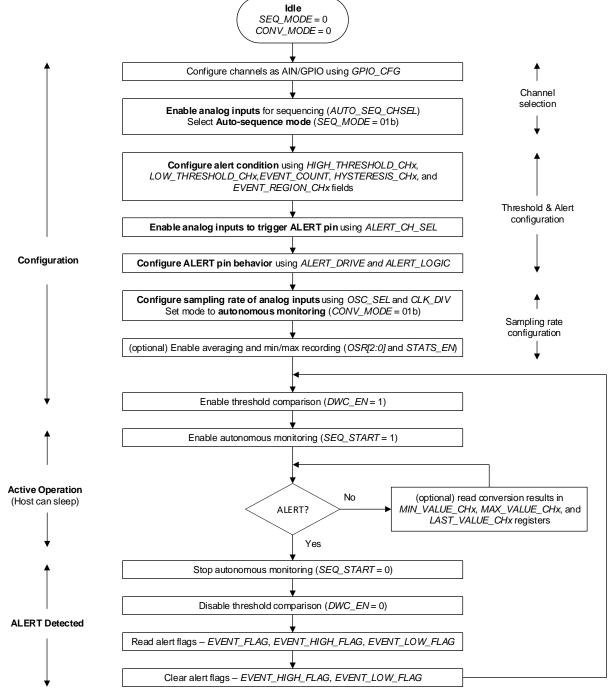

#### 8.4.5 Autonomous Mode

In autonomous mode, the device can be programmed to monitor the voltage applied on the analog input pins of the device and generate an ALERT signal internal to the device when the programmable high or low threshold values are crossed. The internal ALERT signal can be mapped to any one digital output channel by configuring the channel ID in the ALERT\_PIN[3:0] register field. In autonomous mode, the device generates the start of conversion using the internal oscillator. The first start of conversion must be provided by the host and the device generates the subsequent start of conversions.

Figure 19 shows the steps for configuring the functional mode to autonomous mode. Abort the on-going sequence by setting the SEQ\_START to 0b before changing the functional mode or configuration of device.

Figure 19. Configuring the Device in Autonomous Mode

### 8.5 ADS7028 Registers

Table 9 lists the ADS7028 registers. All register offset addresses not listed in Table 9 should be considered as reserved locations and the register contents should not be modified.

| Address | Acronym          | Register Section<br>Name                                |

|---------|------------------|---------------------------------------------------------|

| 0x0     | SYSTEM_STATUS    | SYSTEM_STATUS Register (Address = 0x0) [reset = 0x81]   |

| 0x1     | GENERAL_CFG      | GENERAL_CFG Register (Address = 0x1) [reset = 0x0]      |

| 0x2     | DATA_CFG         | DATA_CFG Register (Address = 0x2) [reset = 0x0]         |

| 0x3     | OSR_CFG          | OSR_CFG Register (Address = 0x3) [reset = 0x0]          |

| 0x4     | OPMODE_CFG       | OPMODE_CFG Register (Address = 0x4) [reset = 0x0]       |

| 0x5     | PIN_CFG          | PIN_CFG Register (Address = 0x5) [reset = 0x0]          |

| 0x7     | GPIO_CFG         | GPIO_CFG Register (Address = 0x7) [reset = 0x0]         |

| 0x9     | GPO_DRIVE_CFG    | GPO_DRIVE_CFG Register (Address = 0x9) [reset = 0x0]    |

| 0xB     | GPO_OUTPUT_VALUE | GPO_OUTPUT_VALUE Register (Address = 0xB) [reset = 0x0] |

| 0xD     | GPI_VALUE        | GPI_VALUE Register (Address = 0xD) [reset = 0x0]        |

| 0xF     | ZCD_BLANKING_CFG | ZCD_BLANKING_CFG Register (Address = 0xF) [reset = 0x0] |

| 0x10    | SEQUENCE_CFG     | SEQUENCE_CFG Register (Address = 0x10) [reset = 0x0]    |

| 0x11    | CHANNEL_SEL      | CHANNEL_SEL Register (Address = 0x11) [reset = 0x0]     |

| 0x12    | AUTO_SEQ_CH_SEL  | AUTO_SEQ_CH_SEL Register (Address = 0x12) [reset = 0x0] |

| 0x14    | ALERT_CH_SEL     | ALERT_CH_SEL Register (Address = 0x14) [reset = 0x0]    |

| 0x16    | ALERT_MAP        | ALERT_MAP Register (Address = 0x16) [reset = 0x0]       |

| 0x17    | ALERT_PIN_CFG    | ALERT_PIN_CFG Register (Address = 0x17) [reset = 0x0]   |

| 0x18    | EVENT_FLAG       | EVENT_FLAG Register (Address = 0x18) [reset = 0x0]      |

| 0x1A    | EVENT_HIGH_FLAG  | EVENT_HIGH_FLAG Register (Address = 0x1A) [reset = 0x0] |

| 0x1C    | EVENT_LOW_FLAG   | EVENT_LOW_FLAG Register (Address = 0x1C) [reset = 0x0]  |

| 0x1E    | EVENT_RGN        | EVENT_RGN Register (Address = 0x1E) [reset = 0x0]       |

| 0x20    | HYSTERESIS_CH0   | HYSTERESIS_CH0 Register (Address = 0x20) [reset = 0xF0] |

| 0x21    | HIGH_TH_CH0      | HIGH_TH_CH0 Register (Address = 0x21) [reset = 0xFF]    |

| 0x22    | EVENT_COUNT_CH0  | EVENT_COUNT_CH0 Register (Address = 0x22) [reset = 0x0] |

| 0x23    | LOW_TH_CH0       | LOW_TH_CH0 Register (Address = 0x23) [reset = 0x0]      |

| 0x24    | HYSTERESIS_CH1   | HYSTERESIS_CH1 Register (Address = 0x24) [reset = 0xF0] |

| 0x25    | HIGH_TH_CH1      | HIGH_TH_CH1 Register (Address = 0x25) [reset = 0xFF]    |

| 0x26    | EVENT_COUNT_CH1  | EVENT_COUNT_CH1 Register (Address = 0x26) [reset = 0x0] |

| 0x27    | LOW_TH_CH1       | LOW_TH_CH1 Register (Address = 0x27) [reset = 0x0]      |

| 0x28    | HYSTERESIS_CH2   | HYSTERESIS_CH2 Register (Address = 0x28) [reset = 0xF0] |

| 0x29    | HIGH_TH_CH2      | HIGH_TH_CH2 Register (Address = 0x29) [reset = 0xFF]    |

| 0x2A    | EVENT_COUNT_CH2  | EVENT_COUNT_CH2 Register (Address = 0x2A) [reset = 0x0] |

| 0x2B    | LOW_TH_CH2       | LOW_TH_CH2 Register (Address = 0x2B) [reset = 0x0]      |

| 0x2C    | HYSTERESIS_CH3   | HYSTERESIS_CH3 Register (Address = 0x2C) [reset = 0xF0] |

| 0x2D    | HIGH_TH_CH3      | HIGH_TH_CH3 Register (Address = 0x2D) [reset = 0xFF]    |

| 0x2E    | EVENT_COUNT_CH3  | EVENT_COUNT_CH3 Register (Address = 0x2E) [reset = 0x0] |

| 0x2F    | LOW_TH_CH3       | LOW_TH_CH3 Register (Address = 0x2F) [reset = 0x0]      |

| 0x30    | HYSTERESIS_CH4   | HYSTERESIS_CH4 Register (Address = 0x30) [reset = 0xF0] |

| 0x31    | HIGH_TH_CH4      | HIGH_TH_CH4 Register (Address = 0x31) [reset = 0xFF]    |

| 0x32    | EVENT_COUNT_CH4  | EVENT_COUNT_CH4 Register (Address = 0x32) [reset = 0x0] |

| 0x33    | LOW_TH_CH4       | LOW_TH_CH4 Register (Address = 0x33) [reset = 0x0]      |

| 0x34    | HYSTERESIS_CH5   | HYSTERESIS_CH5 Register (Address = 0x34) [reset = 0xF0] |

| 0x35    | HIGH_TH_CH5      | HIGH_TH_CH5 Register (Address = 0x35) [reset = 0xFF]    |

### Table 9. ADS7028 Registers

**ADS7028**

SBAS978-JUNE 2019

Copyright © 2019, Texas Instruments Incorporated

ÈXAS NSTRUMENTS

## Table 9. ADS7028 Registers (continued)

|         |                 | Table 9. ADS/026 Registers (continued)                  |

|---------|-----------------|---------------------------------------------------------|

| Address | Acronym         | Register Section Name                                   |

| 0x36    | EVENT_COUNT_CH5 | EVENT_COUNT_CH5 Register (Address = 0x36) [reset = 0x0] |

| 0x37    | LOW_TH_CH5      | LOW_TH_CH5 Register (Address = 0x37) [reset = 0x0]      |

| 0x38    | HYSTERESIS_CH6  | HYSTERESIS_CH6 Register (Address = 0x38) [reset = 0xF0] |

| 0x39    | HIGH_TH_CH6     | HIGH_TH_CH6 Register (Address = 0x39) [reset = 0xFF]    |

| 0x3A    | EVENT_COUNT_CH6 | EVENT_COUNT_CH6 Register (Address = 0x3A) [reset = 0x0] |

| 0x3B    | LOW_TH_CH6      | LOW_TH_CH6 Register (Address = 0x3B) [reset = 0x0]      |

| 0x3C    | HYSTERESIS_CH7  | HYSTERESIS_CH7 Register (Address = 0x3C) [reset = 0xF0] |

| 0x3D    | HIGH_TH_CH7     | HIGH_TH_CH7 Register (Address = 0x3D) [reset = 0xFF]    |

| 0x3E    | EVENT_COUNT_CH7 | EVENT_COUNT_CH7 Register (Address = 0x3E) [reset = 0x0] |

| 0x3F    | LOW_TH_CH7      | LOW_TH_CH7 Register (Address = 0x3F) [reset = 0x0]      |

| 0x60    | MAX_CH0_LSB     | MAX_CH0_LSB Register (Address = 0x60) [reset = 0x0]     |

| 0x61    | MAX_CH0_MSB     | MAX_CH0_MSB Register (Address = 0x61) [reset = 0x0]     |

| 0x62    | MAX_CH1_LSB     | MAX_CH1_LSB Register (Address = 0x62) [reset = 0x0]     |

| 0x63    | MAX_CH1_MSB     | MAX_CH1_MSB Register (Address = 0x63) [reset = 0x0]     |

| 0x64    | MAX_CH2_LSB     | MAX_CH2_LSB Register (Address = 0x64) [reset = 0x0]     |

| 0x65    | MAX_CH2_MSB     | MAX_CH2_MSB Register (Address = 0x65) [reset = 0x0]     |

| 0x66    | MAX_CH3_LSB     | MAX_CH3_LSB Register (Address = 0x66) [reset = 0x0]     |

| 0x67    | MAX_CH3_MSB     | MAX_CH3_MSB Register (Address = 0x67) [reset = 0x0]     |

| 0x68    | MAX_CH4_LSB     | MAX_CH4_LSB Register (Address = 0x68) [reset = 0x0]     |

| 0x69    | MAX_CH4_MSB     | MAX_CH4_MSB Register (Address = 0x69) [reset = 0x0]     |

| 0x6A    | MAX_CH5_LSB     | MAX_CH5_LSB Register (Address = 0x6A) [reset = 0x0]     |

| 0x6B    | MAX_CH5_MSB     | MAX_CH5_MSB Register (Address = 0x6B) [reset = 0x0]     |

| 0x6C    | MAX_CH6_LSB     | MAX_CH6_LSB Register (Address = 0x6C) [reset = 0x0]     |

| 0x6D    | MAX_CH6_MSB     | MAX_CH6_MSB Register (Address = 0x6D) [reset = 0x0]     |

| 0x6E    | MAX_CH7_LSB     | MAX_CH7_LSB Register (Address = 0x6E) [reset = 0x0]     |

| 0x6F    | MAX_CH7_MSB     | MAX_CH7_MSB Register (Address = 0x6F) [reset = 0x0]     |

| 0x80    | MIN_CH0_LSB     | MIN_CH0_LSB Register (Address = 0x80) [reset = 0xFF]    |

| 0x81    | MIN_CH0_MSB     | MIN_CH0_MSB Register (Address = 0x81) [reset = 0xFF]    |

| 0x82    | MIN_CH1_LSB     | MIN_CH1_LSB Register (Address = 0x82) [reset = 0xFF]    |

| 0x83    | MIN_CH1_MSB     | MIN_CH1_MSB Register (Address = 0x83) [reset = 0xFF]    |

| 0x84    | MIN_CH2_LSB     | MIN_CH2_LSB Register (Address = 0x84) [reset = 0xFF]    |

| 0x85    | MIN_CH2_MSB     | MIN_CH2_MSB Register (Address = 0x85) [reset = 0xFF]    |

| 0x86    | MIN_CH3_LSB     | MIN_CH3_LSB Register (Address = 0x86) [reset = 0xFF]    |

| 0x87    | MIN_CH3_MSB     | MIN_CH3_MSB Register (Address = 0x87) [reset = 0xFF]    |

| 0x88    | MIN_CH4_LSB     | MIN_CH4_LSB Register (Address = 0x88) [reset = 0xFF]    |

| 0x89    | MIN_CH4_MSB     | MIN_CH4_MSB Register (Address = 0x89) [reset = 0xFF]    |

| 0x8A    | MIN_CH5_LSB     | MIN_CH5_LSB Register (Address = 0x8A) [reset = 0xFF]    |

| 0x8B    | MIN_CH5_MSB     | MIN_CH5_MSB Register (Address = 0x8B) [reset = 0xFF]    |

| 0x8C    | MIN_CH6_LSB     | MIN_CH6_LSB Register (Address = 0x8C) [reset = 0xFF]    |

| 0x8D    | MIN_CH6_MSB     | MIN_CH6_MSB Register (Address = 0x8D) [reset = 0xFF]    |

| 0x8E    | MIN_CH7_LSB     | MIN_CH7_LSB Register (Address = 0x8E) [reset = 0xFF]    |

| 0x8F    | MIN_CH7_MSB     | MIN_CH7_MSB Register (Address = 0x8F) [reset = 0xFF]    |

| 0xA0    | RECENT_CH0_LSB  | RECENT_CH0_LSB Register (Address = 0xA0) [reset = 0x0]  |

| 0xA1    | RECENT_CH0_MSB  | RECENT_CH0_MSB Register (Address = 0xA1) [reset = 0x0]  |

| 0xA2    | RECENT_CH1_LSB  | RECENT_CH1_LSB Register (Address = 0xA2) [reset = 0x0]  |

| 0xA3    | RECENT_CH1_MSB  | RECENT_CH1_MSB Register (Address = 0xA3) [reset = 0x0]  |

| 0xA4    | RECENT_CH2_LSB  | RECENT_CH2_LSB Register (Address = 0xA4) [reset = 0x0]  |

26 Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

#### TEXAS INSTRUMENTS

#### ADS7028 SBAS978 – JUNE 2019

#### Table 9. ADS7028 Registers (continued)

| Address | Acronym                   | Register Section<br>Name                                             |

|---------|---------------------------|----------------------------------------------------------------------|

| 0xA5    | RECENT_CH2_MSB            | RECENT_CH2_MSB Register (Address = 0xA5) [reset = 0x0]               |

| 0xA6    | RECENT_CH3_LSB            | RECENT_CH3_LSB Register (Address = 0xA6) [reset = 0x0]               |

| 0xA7    | RECENT_CH3_MSB            | RECENT_CH3_MSB Register (Address = 0xA7) [reset = 0x0]               |

| 0xA8    | RECENT_CH4_LSB            | RECENT_CH4_LSB Register (Address = 0xA8) [reset = 0x0]               |

| 0xA9    | RECENT_CH4_MSB            | RECENT_CH4_MSB Register (Address = 0xA9) [reset = 0x0]               |

| 0xAA    | RECENT_CH5_LSB            | RECENT_CH5_LSB Register (Address = 0xAA) [reset = 0x0]               |

| 0xAB    | RECENT_CH5_MSB            | RECENT_CH5_MSB Register (Address = 0xAB) [reset = 0x0]               |

| 0xAC    | RECENT_CH6_LSB            | RECENT_CH6_LSB Register (Address = 0xAC) [reset = 0x0]               |

| 0xAD    | RECENT_CH6_MSB            | RECENT_CH6_MSB Register (Address = 0xAD) [reset = 0x0]               |

| 0xAE    | RECENT_CH7_LSB            | RECENT_CH7_LSB Register (Address = 0xAE) [reset = 0x0]               |

| 0xAF    | RECENT_CH7_MSB            | RECENT_CH7_MSB Register (Address = 0xAF) [reset = 0x0]               |

| 0xC0    | RMS_CFG                   | RMS_CFG Register (Address = 0xC0) [reset = 0x0]                      |

| 0xC1    | RMS_LSB                   | RMS_LSB Register (Address = 0xC1) [reset = 0x0]                      |

| 0xC2    | RMS_MSB                   | RMS_MSB Register (Address = 0xC2) [reset = 0x0]                      |

| 0xC3    | GPO0_TRIG_EVENT_SEL       | GPO0_TRIG_EVENT_SEL Register (Address = 0xC3) [reset = 0x2]          |

| 0xC5    | GPO1_TRIG_EVENT_SEL       | GPO1_TRIG_EVENT_SEL Register (Address = 0xC5) [reset = 0x1]          |

| 0xC7    | GPO2_TRIG_EVENT_SEL       | GPO2_TRIG_EVENT_SEL Register (Address = 0xC7) [reset = 0x8]          |

| 0xC9    | GPO3_TRIG_EVENT_SEL       | GPO3_TRIG_EVENT_SEL Register (Address = 0xC9) [reset = 0x4]          |

| 0xCB    | GPO4_TRIG_EVENT_SEL       | GPO4_TRIG_EVENT_SEL Register (Address = 0xCB) [reset = 0x20]         |

| 0xCD    | GPO5_TRIG_EVENT_SEL       | GPO5_TRIG_EVENT_SEL Register (Address = 0xCD) [reset = 0x10]         |

| 0xCF    | GPO6_TRIG_EVENT_SEL       | GPO6_TRIG_EVENT_SEL Register (Address = 0xCF) [reset = 0x80]         |

| 0xD1    | GPO7_TRIG_EVENT_SEL       | GPO7_TRIG_EVENT_SEL Register (Address = 0xD1) [reset = 0x40]         |

| 0xE3    | GPO_VALUE_ZCD_CFG_CH0_CH3 | GPO_VALUE_ZCD_CFG_CH0_CH3 Register (Address = 0xE3)<br>[reset = 0x0] |

| 0xE4    | GPO_VALUE_ZCD_CFG_CH4_CH7 | GPO_VALUE_ZCD_CFG_CH4_CH7 Register (Address = 0xE4)<br>[reset = 0x0] |

| 0xE7    | GPO_ZCD_UPDATE_EN         | GPO_ZCD_UPDATE_EN Register (Address = 0xE7) [reset = 0x0]            |

| 0xE9    | GPO_TRIGGER_CFG           | GPO_TRIGGER_CFG Register (Address = 0xE9) [reset = 0x0]              |

| 0xEB    | GPO_VALUE_TRIG            | GPO_VALUE_TRIG Register (Address = 0xEB) [reset = 0x0]               |

Complex bit access types are encoded to fit into small table cells. Table 10 shows the codes that are used for access types in this section.

| Access Type                               | Code | Description |  |  |  |  |

|-------------------------------------------|------|-------------|--|--|--|--|

| Read Type                                 |      |             |  |  |  |  |

| R                                         | R    | Read        |  |  |  |  |

| Write Type                                |      |             |  |  |  |  |

| W W Write                                 |      |             |  |  |  |  |

| Reset or Default Value                    |      |             |  |  |  |  |

| -n Value after reset or the default value |      |             |  |  |  |  |

| Register Array Variables                  |      |             |  |  |  |  |

| -  |                               |

|----|-------------------------------|

| 28 | Submit Documentation Feedback |

| Access Type | Code | Description                                                                                                                                                                                                                                                                                                  |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i,j,k,l,m,n |      | When these variables are used in<br>a register name, an offset, or an<br>address, they refer to the value of<br>a register array where the register<br>is part of a group of repeating<br>registers. The register groups form<br>a hierarchical structure and the<br>array is represented with a<br>formula. |

| У           |      | When this variable is used in a register name, an offset, or an address it refers to the value of a register array.                                                                                                                                                                                          |

## 8.5.1 SYSTEM\_STATUS Register (Address = 0x0) [reset = 0x81]

SYSTEM\_STATUS is shown in Figure 20 and described in Table 11.

Return to the Summary Table.

### Figure 20. SYSTEM\_STATUS Register

| 7    | 6          | 5        | 4        | 3        | 2                | 1          | 0      |

|------|------------|----------|----------|----------|------------------|------------|--------|

| RSVD | SEQ_STATUS | RESERVED | RMS_DONE | OSR_DONE | CRC_ERR_FU<br>SE | CRC_ERR_IN | BOR    |

| R-1b | R-0b       | R-0b     | R/W-0b   | R/W-0b   | R-0b             | R/W-0b     | R/W-1b |

#### Table 11. SYSTEM\_STATUS Register Field Descriptions

| Bit | Field        | Туре | Reset | Description                                                                                                                                 |  |  |

|-----|--------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | RSVD         | R    | 1b    | Reads return 1b.                                                                                                                            |  |  |

| 6   | SEQ_STATUS   | R    | 0b    | Status of the channel sequencer.                                                                                                            |  |  |

|     |              |      |       | 0b = Sequence stopped.                                                                                                                      |  |  |

|     |              |      |       | 1b = Sequence in progress.                                                                                                                  |  |  |

| 5   | RESERVED     | R    | 0b    | Reserved. Reads return 0.                                                                                                                   |  |  |

| 4   | RMS_DONE     | R/W  | 0b    | RMS computation status. Clear this bit by writing 1b to this bit.                                                                           |  |  |

|     |              |      |       | 0b = RMS operation in progress or not started; RMS result not ready.                                                                        |  |  |

|     |              |      |       | 1b = RMS computation complete; RMS result ready.                                                                                            |  |  |

| 3   | OSR_DONE     | R/W  | 0b    | Averaging status. Clear this bit by writing 1b to this bit.                                                                                 |  |  |

|     |              |      |       | 0b = Averaging in progress or not started; average result is not ready.                                                                     |  |  |

|     |              |      |       | 1b = Averaging complete; average result is ready.                                                                                           |  |  |

| 2   | CRC_ERR_FUSE | R    | 0b    | Device power-up configuration CRC check status. To re-evaluate this bit, software reset the device or power cycle AVDD.                     |  |  |