# 3.0V TO TO 3.6V, 4.9GHz TO 5.85GHz 802.11a/n/ac FRONT END MODULE

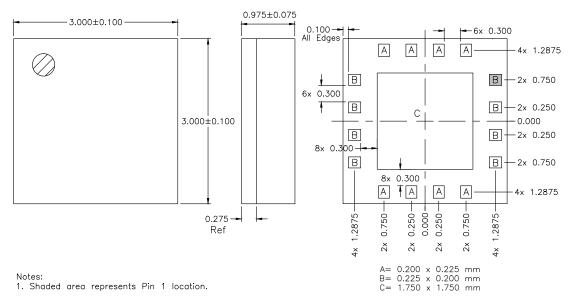

Package: Laminate, 16-pin, 3.0mm x 3.0mm x 1.05mm

### **Features**

- Integrated 4.9GHz to 5.85GHz Amplifier, SPDT Tx/Rx Switch, LNA with Bypass, and Power Detector Coupler

- P<sub>OUT</sub> = 17dBm, 11a/n, 3.3V 2.5% Dynamic EVM

- P<sub>OUT</sub> = 16dBm, 11ac HT80 MCS9, 1.8% Dynamic EVM

### **Applications**

- IEEE802.11a/n/ac WiFi Applications

- 4.9GHz to 5.85GHz ISM Band Applications

- Portable Battery-Powered Equipment

- WiFi Access Points, Gateways and Set Top Boxes

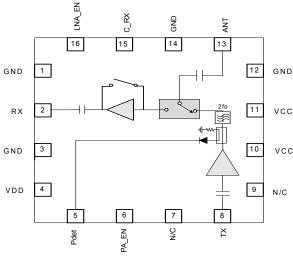

Functional Block Diagram

### **Product Description**

The RFFM4591 provides a complete integrated solution in a single front end module (FEM) for WiFi 802.11a/n/ac systems. The ultra-small form factor and integrated matching minimizes the layout area in the customer's application and greatly reduces the number of external components. This simplifies the total front end solution by reducing the bill of materials, system footprint, and manufacturability cost. The RFFM4591 integrates a power amplifier (PA), single pole double throw switch (SPDT), LNA with bypass, and a power detector coupler for improved accuracy. The device is provided in a 3mm x 3mm x 1.05mm, 16-pin laminate package. This module meets or exceeds the RF front end needs of IEEE 802.11a/n/ac WiFi RF systems.

#### **Ordering Information**

RFFM4591PCK-410 RFFM4591 Eval Board with 5-piece bag RFFM4591SB 5-Piece bag RFFM4591TR7 2500-Piece reel

RFFM4591TR7 2500-Piece re RFFM4591SQ 25-Piece bag

### **Absolute Maximum Ratings**

| Parameter                                             | Rating      | Unit            |

|-------------------------------------------------------|-------------|-----------------|

| DC Supply Voltage (No RF)                             | 5.5         | V <sub>DC</sub> |

| DC Supply Voltage (With RF On)                        | 5           | V <sub>DC</sub> |

| Maximum Tx and Rx Input Power (No Damage)             | 12          | dBm             |

| Operating Ambient Temperature                         | -20 to +85  | °C              |

| Extended Temperature Range (with Reduced Performance) | -40 to -20  | °C              |

| Storage Temperature                                   | -40 to +150 | °C              |

| Moisture Sensitivity                                  | MSL3        |                 |

#### Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

RFMD Green: RoHS compliant per EU Directive 2011/65/EU, halogen free per IEC 61249-2-21, < 1000 ppm each of antimony trioxide in polymeric materials and red phosphorus as a flame retardant, and <2% antimony in solder.

| Parameter                         | Sp    | Specification |       |         | On a dikina                                                                                                                                                  |  |

|-----------------------------------|-------|---------------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                         | Min.  | Тур.          | Max.  | Unit    | Condition                                                                                                                                                    |  |

| Typical Conditions 3.3V           |       |               |       |         | Temperature = $-10^{\circ}$ C to $+70^{\circ}$ C, $V_{CC}$ = 3.3V, PA_EN = high, $P_{OUT}$ = 17dBm using a IEEE802.11n MCS7 waveform unless otherwise noted. |  |

| Tx Performance - 11a/n/ac         |       |               |       |         | Compliance with standard 802.11a/n/ac                                                                                                                        |  |

| Frequency                         | 5150  |               | 5850  | MHz     |                                                                                                                                                              |  |

| 802.11n Output Power              | 16.5  | 17            |       | dBm     | 802.11n HT20 and HT40 MCS7                                                                                                                                   |  |

| 11n Dynamic EVM                   |       | 2.5           | 3     | %       |                                                                                                                                                              |  |

|                                   |       | -32           | -30.5 | dB      |                                                                                                                                                              |  |

| 802.11ac Output Power             | 15    | 16            |       | dBm     | 802.11ac HT40 and HT80 MCS9                                                                                                                                  |  |

| 11ac Dynamic EVM                  |       |               | 1.8   | %       |                                                                                                                                                              |  |

|                                   |       |               | -35   | dB      |                                                                                                                                                              |  |

| Tx Performance - Spectral<br>Mask |       |               |       |         |                                                                                                                                                              |  |

| 802.11n Output Power              |       | 19            |       | dBm     | Meet IEEE HT40 MCS7 Spectral Mask                                                                                                                            |  |

| Frequency                         | 4900  |               | 5150  | MHz     |                                                                                                                                                              |  |

| 802.11n Output Power              | 16.5  | 17            |       | dBm     | 802.11n HT20 and HT40 MCS7                                                                                                                                   |  |

| 11n EVM                           |       | 2.5           | 3     | %       |                                                                                                                                                              |  |

|                                   |       | -32           | -30.5 | dB      |                                                                                                                                                              |  |

| Second Harmonic                   |       | -45           | -41   | dBm/MHz | 4.9GHz to 5.825GHz, P <sub>OUT</sub> = 18dBm, 6Mbps 802.11a                                                                                                  |  |

| Third Harmonic                    |       | -50           | -43   | dBm/MHz |                                                                                                                                                              |  |

| General Tx Performance            |       |               |       |         |                                                                                                                                                              |  |

| Gain                              | 24    | 26            | 30    | dB      | 5.15GHz to 5.35GHz                                                                                                                                           |  |

|                                   | 26    | 28            | 31    | dB      | 5.35GHz to 5.825GHz                                                                                                                                          |  |

| Gain variation over Temp          | -2    |               | 2     | dB      |                                                                                                                                                              |  |

| Power Detect Voltage              | 0.35  | 0.375         | 0.4   | V       | RF = off                                                                                                                                                     |  |

|                                   | 0.706 |               | 0.786 | V       | Frequency = 5825MHz, P <sub>OUT</sub> = 16.5dBm, T = 25°C                                                                                                    |  |

| Power Detect Accuracy             | -1.5  |               | 1.5   | dB      | Into 3:1 VSWR load, T = 25°C                                                                                                                                 |  |

| Input Return Loss - TX_IN pin     |       | -15           | -7    | dB      | In specified frequency band                                                                                                                                  |  |

| Output Return Loss at ANT pin     |       | -15           | -10   | dB      |                                                                                                                                                              |  |

| Dovernator                                                                         | Specification |      |                 | 11   | Condition                                                                                                                                          |  |

|------------------------------------------------------------------------------------|---------------|------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                                          | Min.          | Тур. | Max.            | Unit | Condition                                                                                                                                          |  |

| Typical Conditions 3.3V (continued)                                                |               |      |                 |      | Temperature = -10 °C to +70 °C, $V_{\rm CC}$ = 3.3V, PA_EN = high, $P_{\rm OUT}$ = 17dBm using a IEEE802.11n MCS7 waveform unless otherwise noted. |  |

| General Tx Performance                                                             |               |      |                 |      |                                                                                                                                                    |  |

| Operating Current                                                                  |               | 225  | 250             | mA   | P <sub>OUT</sub> = 17dBm                                                                                                                           |  |

|                                                                                    |               | 220  |                 | mA   | P <sub>OUT</sub> = 16dBm                                                                                                                           |  |

| Quiescent Current                                                                  |               | 175  | 190             | mA   | Nominal Conditions. No RF applied                                                                                                                  |  |

| Leakage Current                                                                    |               |      | 10              | μА   | V <sub>CC</sub> = 3.3V, LNA_EN = low, C_RX = low,<br>PA_EN = low, temperature = 25 ° C                                                             |  |

| V <sub>CONTROL</sub> High (PA_EN, C_RX, and<br>LNA_EN) for both TX and RX<br>modes | 2.8           | 2.9  | V <sub>CC</sub> | V    |                                                                                                                                                    |  |

| V <sub>CONTROL</sub> Low (PA_EN, C_RX, and<br>LNA_EN) for both TX and RX<br>modes  | 0             |      | 0.2             | V    |                                                                                                                                                    |  |

| Turn-on time from PA_EN edge                                                       |               |      | 500             | ns   | Output stable to within 90% of final gain                                                                                                          |  |

| Turn-off time from PA_EN edge                                                      |               |      | 500             | ns   |                                                                                                                                                    |  |

| Stability                                                                          | -25           |      | 24              | dBm  | No spurs above -47dBm into 4:1 VSWR                                                                                                                |  |

| CW P1dB                                                                            | 24            | 25   |                 | dBm  | Tx mode in 50% Duty Cycle                                                                                                                          |  |

| Rx Performance                                                                     |               |      |                 |      | Temperature = -10°C to +70°C, V <sub>DD</sub> = 3.3V,<br>C_RX = high, LNA_EN = high                                                                |  |

| Gain                                                                               | 11            | 12.5 | 13              | dB   | Temperature = 25°C                                                                                                                                 |  |

| Gain Over Operating Temperature<br>Range                                           | 9             | 12.5 | 14              | dBm  | Temperature = -10 °C to +70 °C                                                                                                                     |  |

| Gain - Extended                                                                    | 8             | 12.5 | 16              | dB   | Temperature = -40°C to +85°C                                                                                                                       |  |

| NF                                                                                 |               | 2.5  | 3.5             | dB   | In specified frequency band                                                                                                                        |  |

| Rx Port Return Loss                                                                |               |      | -7              | dB   |                                                                                                                                                    |  |

| ANT Port Return Loss                                                               |               | -10  | -5              | dB   |                                                                                                                                                    |  |

| Input IP3                                                                          | -3            | 0    |                 | dBm  |                                                                                                                                                    |  |

| Input P1dB                                                                         | -13           | -10  |                 | dBm  |                                                                                                                                                    |  |

| I <sub>DD</sub>                                                                    |               | 13   | 17              | mA   |                                                                                                                                                    |  |

| LNA_EN Control Current                                                             |               | 30   | 50              | μΑ   |                                                                                                                                                    |  |

| Rx Bypass Mode                                                                     |               |      |                 |      | Temperature = -10 ° C to +70 ° C, V <sub>DD</sub> = 3.3V,<br>C_RX = high, LNA_EN = low                                                             |  |

| Insertion Loss                                                                     | -10           | -8   | -6              | dB   |                                                                                                                                                    |  |

| Rx Port Return Loss                                                                |               |      | -7              | dB   |                                                                                                                                                    |  |

| ANT Port Return Loss                                                               |               | -6   |                 | dB   |                                                                                                                                                    |  |

| Input IP3                                                                          | 15            | 20   |                 | dBm  |                                                                                                                                                    |  |

| Input P1dB                                                                         | 5             | 10   |                 | dBm  |                                                                                                                                                    |  |

| Isolation                                                                          |               |      |                 |      |                                                                                                                                                    |  |

| ANT-TX; Rx Mode                                                                    | 20            |      |                 | dB   | C_RX = High, PA_EN = Low                                                                                                                           |  |

| ANT-RX; Tx Mode                                                                    | 25            |      |                 | dB   | PA_EN = High, C_RX = Low, LNA_EN = Low                                                                                                             |  |

| Doromotor                           | Specification |      |      | l lmit | On a disting                                                                                                                                             |  |

|-------------------------------------|---------------|------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                           | Min.          | Тур. | Max. | Unit   | Condition                                                                                                                                                |  |

| Typical Conditions 3.3V (continued) |               |      |      |        | Temperature = -10 °C to +70 °C, V <sub>CC</sub> = 3.3V, PA_EN = high, P <sub>OUT</sub> = 17dBm using a IEEE802.11n MCS7 waveform unless otherwise noted. |  |

| General Performance                 |               |      |      |        |                                                                                                                                                          |  |

| Control Current                     |               |      |      |        |                                                                                                                                                          |  |

| C_RX Current                        |               | 0.5  | 1    | μΑ     |                                                                                                                                                          |  |

| PA_EN Current                       |               | 30   | 50   | μΑ     |                                                                                                                                                          |  |

| Switch Control Speed                |               |      | 100  | ns     |                                                                                                                                                          |  |

| PA_EN Control Impedance             |               | 4.9  |      | MΩ     |                                                                                                                                                          |  |

| LNA_EN Control Impedance            |               | 6.5  |      | MΩ     |                                                                                                                                                          |  |

| C_RX Control Impedance              |               | 27   |      | MΩ     |                                                                                                                                                          |  |

| ESD                                 |               |      |      |        |                                                                                                                                                          |  |

| Human Body Model                    | 500           |      |      | V      | EIA/JESD22-114A RF pins                                                                                                                                  |  |

|                                     | 1000          |      |      | V      | EIA/JESD22-114A DC pins                                                                                                                                  |  |

| Charge Device Model                 | 1000          |      |      | V      | JESD22-C101C all pins                                                                                                                                    |  |

| Thermal Resistance                  |               |      |      |        |                                                                                                                                                          |  |

| R <sub>TH_I</sub>                   |               | 46   |      | °C/W   |                                                                                                                                                          |  |

| Maximum Input Power                 |               |      | 12   | dBm    | Into 50Ω, V <sub>CC</sub> = 3.3V, 25°C                                                                                                                   |  |

| Maximum Input Power                 |               |      | 12   | dBm    | 6:1 VSWR, V <sub>CC</sub> = 3.3V, 25°C                                                                                                                   |  |

| Maximum Input Power                 |               |      | 5    | dBm    | 10:1 VSWR, V <sub>CC</sub> = 3.3V, 25°C                                                                                                                  |  |

**Logic Control Table**

| Mode                      | PA EN | LNA EN | C RX |

|---------------------------|-------|--------|------|

| Standby                   | Low   | Low    | Low  |

| 802.11a/n/ac Tx           | High  | Low    | Low  |

| 802.11a/n/ac Rx Gain      | Low   | High   | High |

| 802.11a/n/ac Rx<br>Bypass | Low   | Low    | High |

Note: High = 2.8V to  $V_{CC}$ , Low = 0V to 0.2V

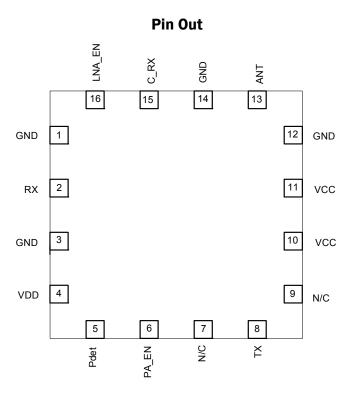

## **Pin Names and Descriptions**

| Pin         Name         Description           1         GND         Ground connection.           2         RX         RF output port for the 802.11a/n/ac LNA. Input is matched to 50Ω and DC block is provided internally.           3         GND         Ground connection.           4         VDD         Supply voltage for the LNA. See applications schematic for biasing and bypassing components.           5         PDET         Power detector voltage for Tx section. PDET voltage varies with output power. May need external capacitor for noise decoupling.           6         PA_EN         Control voltage for the PA and Tx switch. See truth table for proper settings.           7         NC         Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.           8         TX         RF input port for the 802.11a/n/ac PA. Input is matched to 50Ω and DC block is provided internally.           9         NC         Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.           10         VCC         Supply voltage for the PA. See applications schematic for biasing and bypassing components.           11         VCC         Supply voltage for the PA. See applications schematic for biasing and bypassing components.           12         GND         Ground connection.           13         ANT         RF bidirectional |          |        | i iii Naines and Descriptions                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--------------------------------------------------------------------------------------------------------------|

| 2 RX RF output port for the 802.11a/n/ac LNA. Input is matched to 50Ω and DC block is provided internally.  3 GND Ground connection.  4 VDD Supply voltage for the LNA. See applications schematic for biasing and bypassing components.  5 PDET Power detector voltage for Tx section. PDET voltage varies with output power. May need external capacitor for noise decoupling.  6 PA_EN Control voltage for the PA and Tx switch. See truth table for proper settings.  7 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  8 TX RF input port for the 802.11a/n/ac PA. Input is matched to 50Ω and DC block is provided internally.  9 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  10 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  11 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  12 GND Ground connection.  13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  GND Ground connection.  14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                        | Pin      | Name   | Description                                                                                                  |

| 3 GND Ground connection. 4 VDD Supply voltage for the LNA. See applications schematic for biasing and bypassing components. 5 PDET Power detector voltage for Tx section. PDET voltage varies with output power. May need external capacitor for noise decoupling. 6 PA_EN Control voltage for the PA and Tx switch. See truth table for proper settings. 7 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it. 8 TX RF input port for the 802.11a/n/ac PA. Input is matched to 50Ω and DC block is provided internally. 9 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it. 10 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components. 11 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components. 12 GND Ground connection. 13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally. 14 GND Ground connection. 15 C_RX Receive switch control pin. See switch truth table for proper level. 16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                      | 1        | GND    | Ground connection.                                                                                           |

| 4 VDD Supply voltage for the LNA. See applications schematic for biasing and bypassing components.  5 PDET Power detector voltage for Tx section. PDET voltage varies with output power. May need external capacitor for noise decoupling.  6 PA_EN Control voltage for the PA and Tx switch. See truth table for proper settings.  7 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  8 TX RF input port for the 802.11a/n/ac PA. Input is matched to 50Ω and DC block is provided internally.  9 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  10 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  11 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  12 GND Ground connection.  13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                   | 2        | RX     | RF output port for the 802.11a/n/ac LNA. Input is matched to $50\Omega$ and DC block is provided internally. |

| FORT Power detector voltage for Tx section. PDET voltage varies with output power. May need external capacitor for noise decoupling.  PA_EN Control voltage for the PA and Tx switch. See truth table for proper settings.  NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  RF input port for the 802.11a/n/ac PA. Input is matched to 50Ω and DC block is provided internally.  NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  GND Ground connection.  RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  GND Ground connection.  Receive switch control pin. See switch truth table for proper level.  LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                  | 3        | GND    | Ground connection.                                                                                           |

| for noise decoupling.  6 PA_EN Control voltage for the PA and Tx switch. See truth table for proper settings.  7 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  8 TX RF input port for the 802.11a/n/ac PA. Input is matched to 50Ω and DC block is provided internally.  9 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  10 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  11 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  12 GND Ground connection.  13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4        | VDD    | Supply voltage for the LNA. See applications schematic for biasing and bypassing components.                 |

| NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  RF input port for the 802.11a/n/ac PA. Input is matched to 50Ω and DC block is provided internally.  NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  GND Ground connection.  RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  GND Ground connection.  C_RX Receive switch control pin. See switch truth table for proper level.  LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5        | PDET   |                                                                                                              |

| 8 TX RF input port for the 802.11a/n/ac PA. Input is matched to 50Ω and DC block is provided internally. 9 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it. 10 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components. 11 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components. 12 GND Ground connection. 13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally. 14 GND Ground connection. 15 C_RX Receive switch control pin. See switch truth table for proper level. 16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6        | PA_EN  | Control voltage for the PA and Tx switch. See truth table for proper settings.                               |

| 9 NC Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  10 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  11 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  12 GND Ground connection.  13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7        | NC     | Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  |

| 10 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  11 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  12 GND Ground connection.  13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8        | TX     | RF input port for the 802.11a/n/ac PA. Input is matched to $50\Omega$ and DC block is provided internally.   |

| 11 VCC Supply voltage for the PA. See applications schematic for biasing and bypassing components.  12 GND Ground connection.  13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9        | NC     | Not Connected. This Pin is not internally connected so customer has the choice to leave it NC or ground it.  |

| 12 GND Ground connection.  13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10       | VCC    | Supply voltage for the PA. See applications schematic for biasing and bypassing components.                  |

| 13 ANT RF bidirectional antenna port matched to 50Ω and DC block is provided internally.  14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11       | VCC    | Supply voltage for the PA. See applications schematic for biasing and bypassing components.                  |

| 14 GND Ground connection.  15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12       | GND    | Ground connection.                                                                                           |

| 15 C_RX Receive switch control pin. See switch truth table for proper level.  16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13       | ANT    | RF bidirectional antenna port matched to $50\Omega$ and DC block is provided internally.                     |

| 16 LNA_EN Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14       | GND    | Ground connection.                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15       | C_RX   | Receive switch control pin. See switch truth table for proper level.                                         |

| Pkg Base GND Ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16       | LNA_EN | Control voltage for the LNA. When this pin is set to a LOW logic state, the bypass mode is enabled.          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pkg Base | GND    | Ground connection.                                                                                           |

## **Package Drawing**

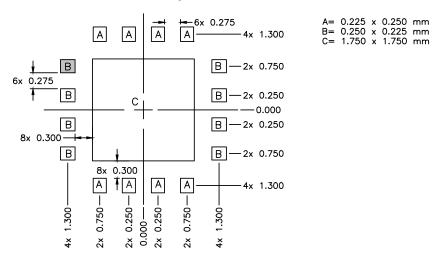

## **RFFM4591 PCB Footprint and Stencil Recommendations**

#### Notes

- 1. Shaded area represents Pin 1 location.

- 2. Example of the number and size of vias can be found on the RFMD evaluation board layout.

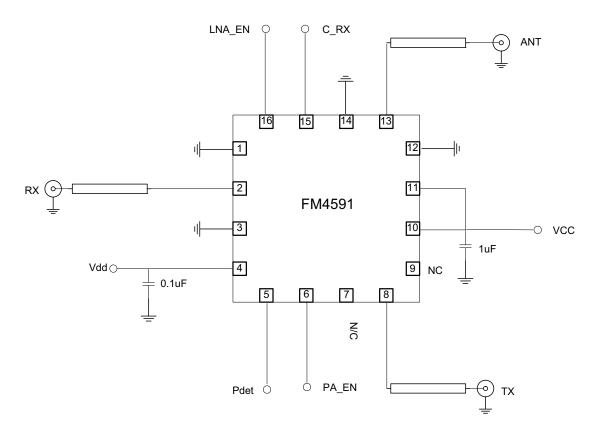

### **Evaluation Board Schematic**