**产品特性**

超低功耗、高性能收发器

频段

862 MHz至928 MHz

431 MHz至464 MHz

支持数据速率

1 kbps至300 kbps

2.2 V至3.6 V电源供电

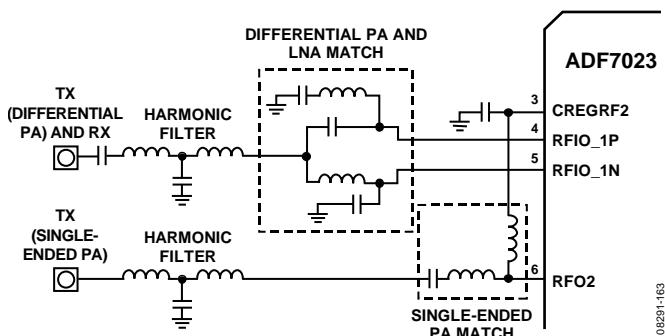

单端和差分PA

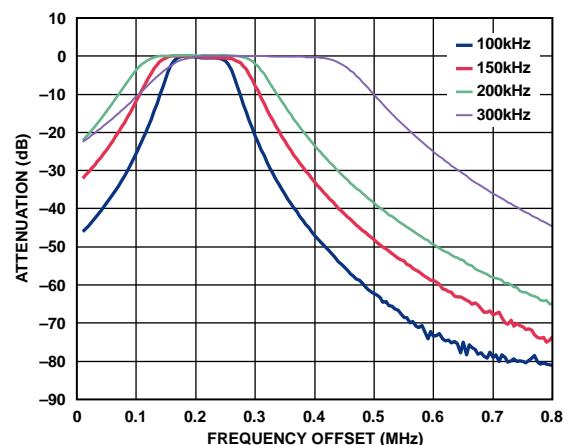

中频带宽可编程的低中频接收机

100 kHz、150 kHz、200 kHz、300 kHz

接收机灵敏度(BER)

-116 dBm(1.0 kbps、2FSK、GFSK)

-107.5 dBm(38.4 kbps、2FSK、GFSK)

-102.5 dBm(150 kbps、GFSK、GMSK)

-100 dBm(300 kbps、GFSK、GMSK)

-104 dBm(19.2 kbps、OOK)

极低功耗

12.8 mA(PHY\_RX模式, 最大前端增益)

24.1 mA(PHY\_TX模式, 10 dBm输出, 单端PA)

0.75 μA(PHY\_SLEEP模式, 32 kHz RC振荡器有效)

1.28 μA(PHY\_SLEEP模式, 32 kHz XTAL振荡器有效)

0.33 μA(PHY\_SLEEP模式, 深度休眠模式1)

RF输出功率范围: -20 dBm至+13.5 dBm(单端PA)

RF输出功率范围: -20 dBm至+10 dBm(差分PA)

已获专利的快速建立自动频率控制(AFC)

数字接收信号强度指示(RSSI)

集成PLL环路滤波器和Tx/Rx开关

快速自动VCO校准

自动频率合成器带宽优化

片内集成低功耗定制8位处理器

无线电控制

数据包管理

智能唤醒模式

数据包管理支持

高度灵活, 支持广泛的包格式

前同步码/同步字/CRC/地址的插入和检测

曼彻斯特和8b/10b数据编码与解码

数据白化

智能唤醒模式

的低功耗模式支持接收机自主唤醒、载波检测和包接收

可下载的固件模块

完全自动化的镜像抑制校准(正在申请专利)

采用硬件加速的128位AES加密/解密, 密钥大小: 128位、192位和256位

采用硬件加速的Reed Solomon误差校正

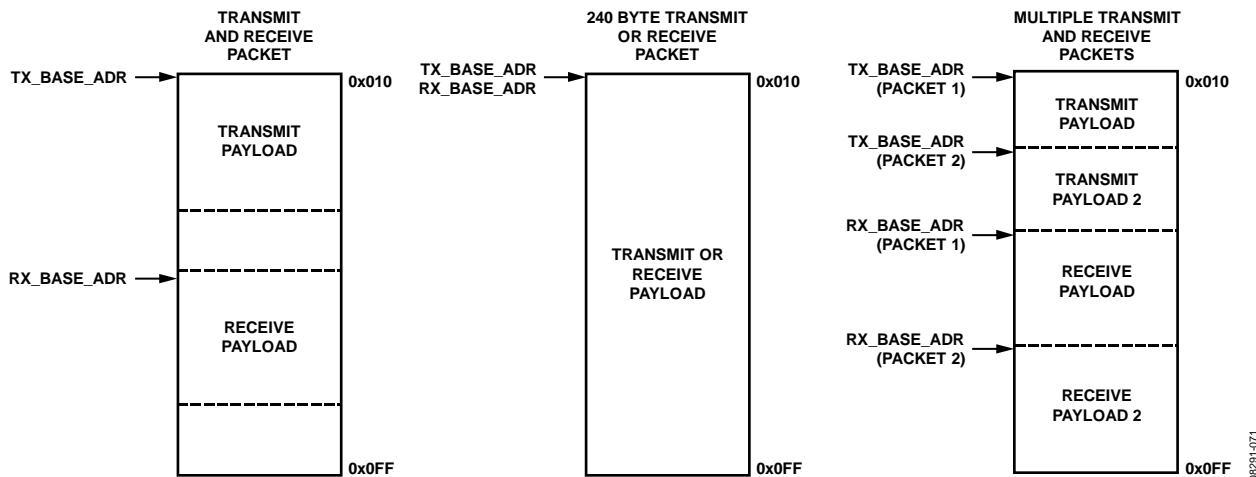

240字节包缓冲器用于缓冲TX/RX数据

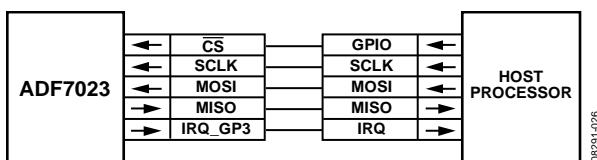

支持块读取/写入操作的高效SPI控制接口

集成电池报警和温度传感器

集成RC和32.768 kHz晶体振荡器

片内集成8位ADC

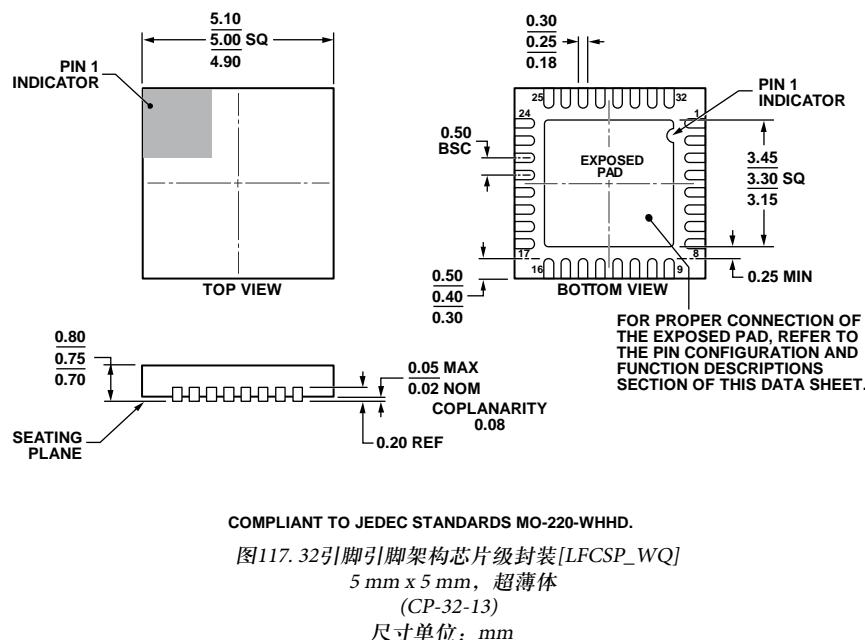

5 mm × 5 mm、32引脚LFCSP封装

**应用**

智能计量

IEEE 802.15.4g

无线MBUS

家庭自动化

过程和楼宇控制

无线传感器网络(WSN)

无线医疗保健

## Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

ADI中文版数据手册是英文版数据手册的译文, 敬请谅解翻译中可能存在的语言组织或翻译错误, ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性, 请参考ADI提供的最新英文版数据手册。

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 [www.analog.com](http://www.analog.com)

Fax: 781.461.3113 ©2010–2012 Analog Devices, Inc. All rights reserved.

## 目录

|                |    |                              |    |

|----------------|----|------------------------------|----|

| 特性             | 1  | SPORT模式下的中断                  | 53 |

| 应用             | 1  | ADF7023存储器映射                 | 54 |

| 修订历史           | 3  | BBRAM                        | 54 |

| 功能框图           | 4  | 调制解调器配置RAM (MCR)             | 54 |

| 概述             | 4  | 程序ROM                        | 54 |

| 技术规格           | 6  | 程序RAM                        | 54 |

| RF和频率合成器规格     | 6  | 包RAM                         | 55 |

| 发射机规格          | 7  | SPI接口                        | 56 |

| 接收机规格          | 9  | 通用特性                         | 56 |

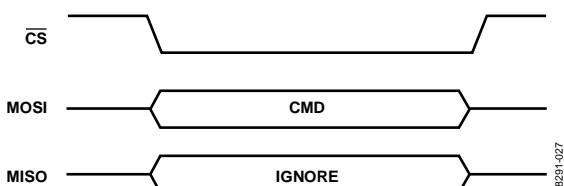

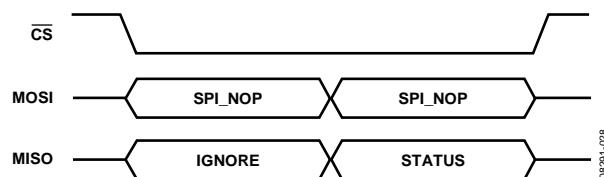

| 时序和数字规格        | 13 | 命令访问                         | 56 |

| 辅助模块技术规格       | 14 | 状态字                          | 56 |

| 通用规格           | 15 | 命令排队                         | 57 |

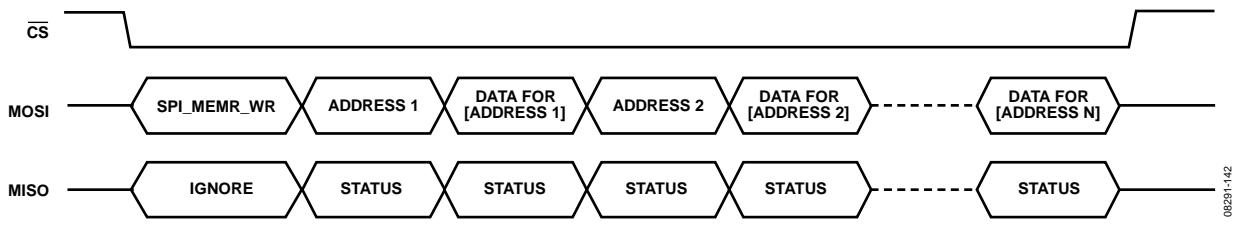

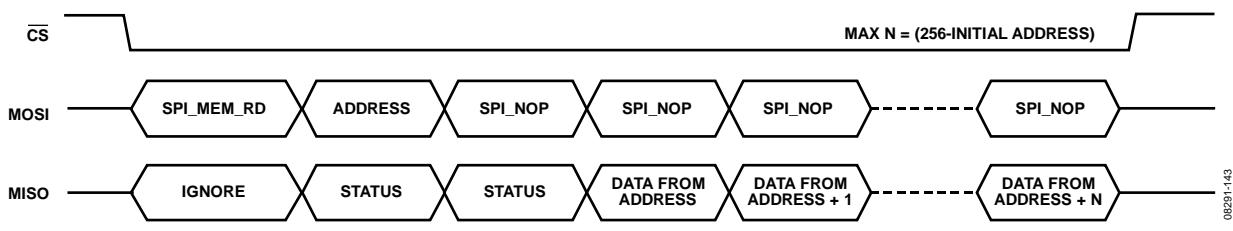

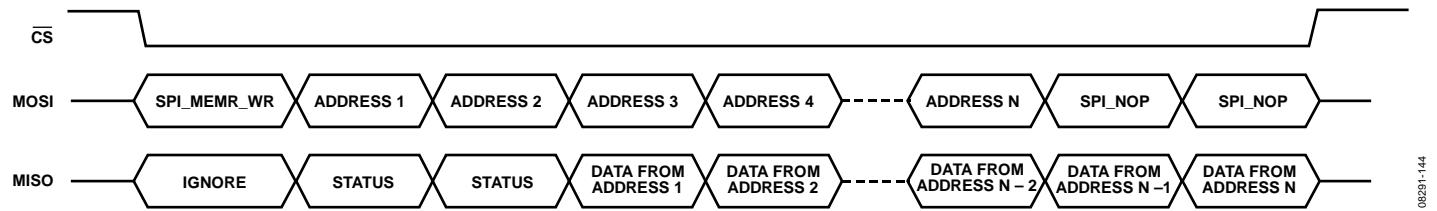

| 时序规格           | 16 | 存储器访问                        | 58 |

| 绝对最大额定值        | 17 | 低功耗模式                        | 61 |

| ESD警告          | 17 | 低功耗模式示例                      | 64 |

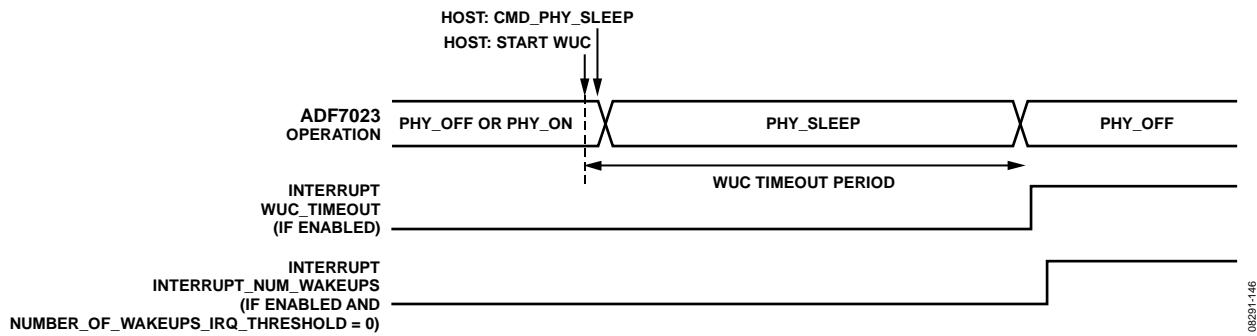

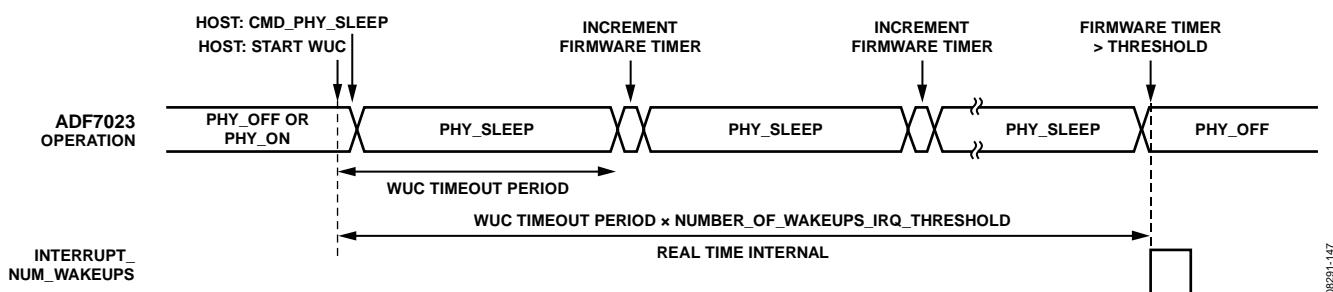

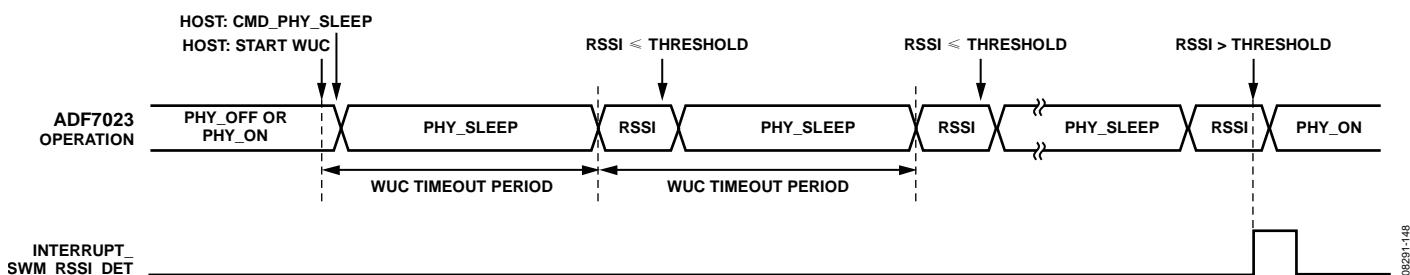

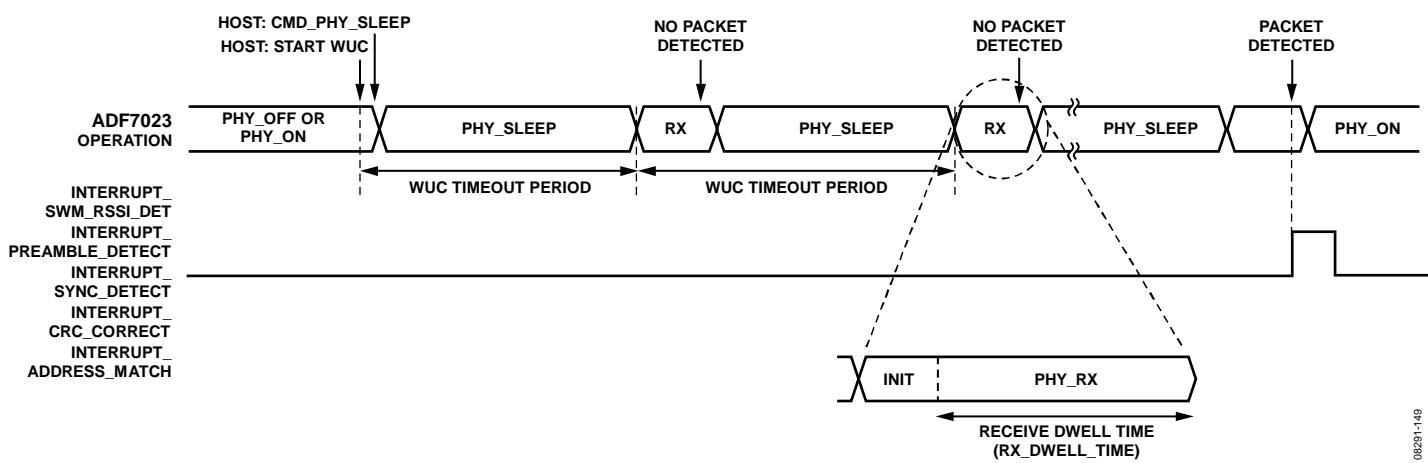

| 引脚配置和功能描述      | 18 | 低功耗模式时序图                     | 66 |

| 典型性能参数         | 20 | WUC设置                        | 67 |

| 术语             | 32 | 固件定时器设置                      | 69 |

| 无线电控制          | 33 | RC振荡器校准                      | 69 |

| 无线电状态          | 33 | 可下载固件模块                      | 71 |

| 初始化            | 35 | 向程序RAM写入模块                   | 71 |

| 命令             | 35 | 镜像抑制校准模块                     | 71 |

| 自动状态跃迁         | 37 | Reed Solomon编码模块             | 71 |

| 状态跃迁和命令时序      | 38 | AES加密和解密模块                   | 71 |

| 数据包模式          | 43 | 无线电模块                        | 73 |

| 前同步码           | 43 | 频率合成器                        | 73 |

| 同步字            | 44 | 晶振                           | 74 |

| 有效载荷           | 45 | 调制                           | 74 |

| CRC            | 46 | RF输出级                        | 74 |

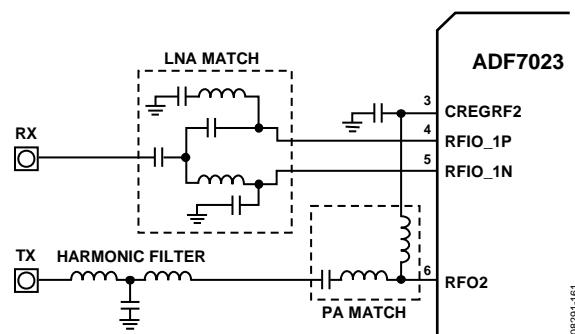

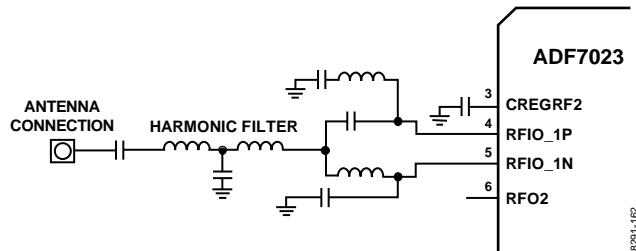

| 后同步码           | 47 | PA/LNA接口                     | 75 |

| 发射包时序          | 47 | 接收通道滤波器                      | 75 |

| 数据白化           | 48 | 镜像通道抑制                       | 75 |

| 曼彻斯特编码         | 48 | 自动增益控制(AGC)                  | 75 |

| 8b/10b编码       | 48 | RSSI                         | 76 |

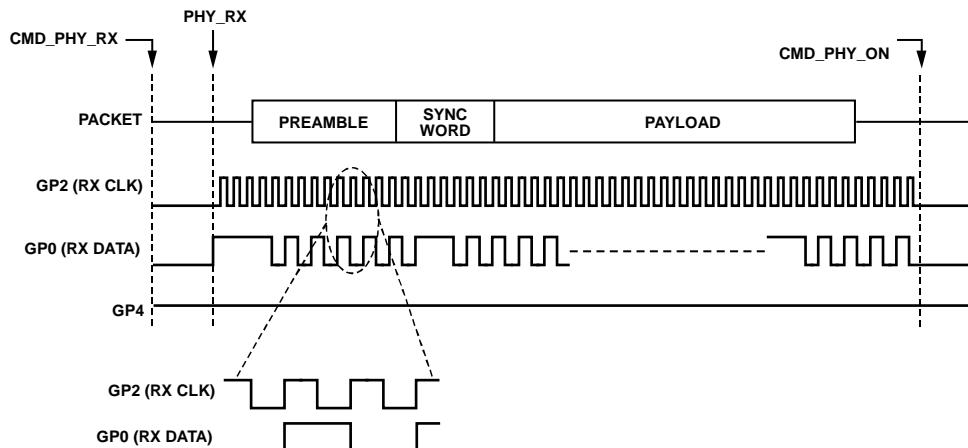

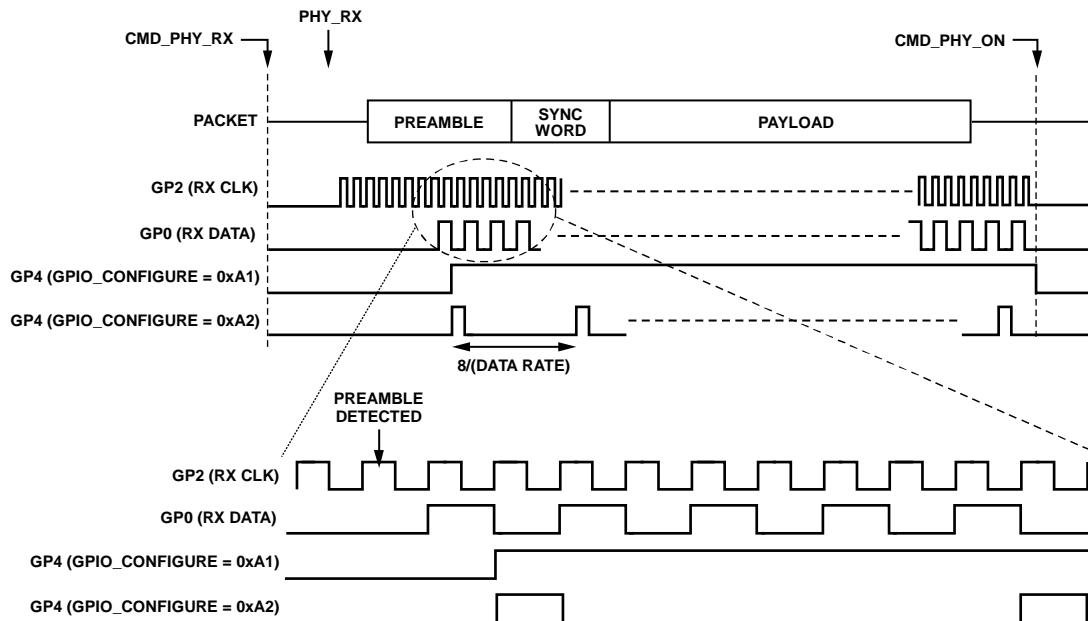

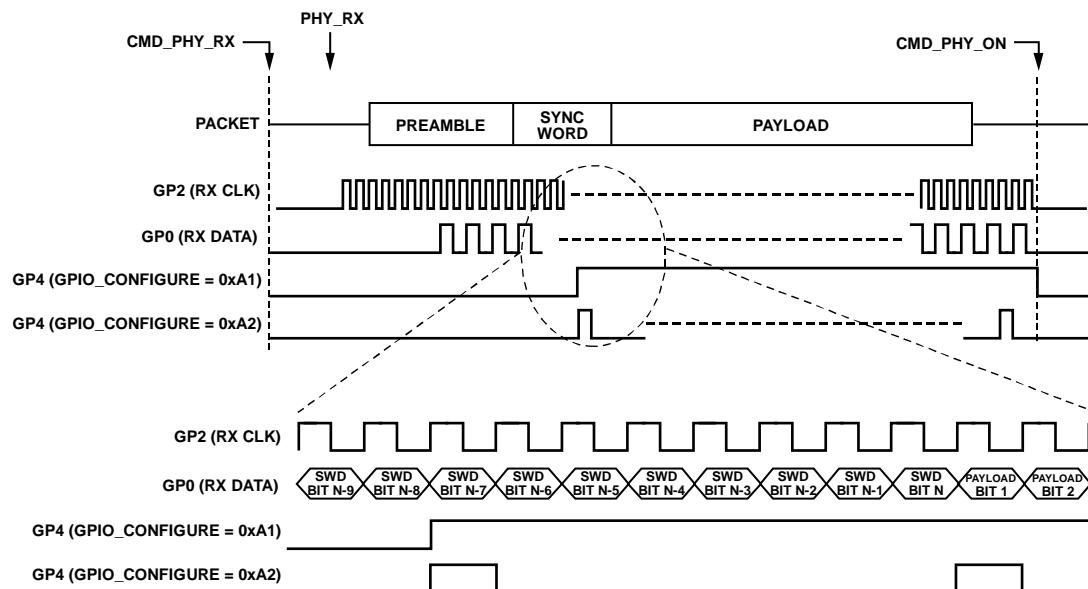

| SPORT模式        | 49 | 2FSK/GFSK/MSK/GMSK解调         | 78 |

| SPORT模式下的数据包结构 | 49 | 时钟恢复                         | 80 |

| SPORT发送模式      | 49 | OOK解调                        | 80 |

| SPORT接收模式      | 49 | 针对2FSK/GFSK/MSK/GMSK的建议接收机设置 | 81 |

| SPORT模式下的发送位延迟 | 49 | 针对OOK的建议接收机设置                | 82 |

| 中断产生           | 52 |                              |    |

|             |    |

|-------------|----|

| 外设特性.....   | 83 |

| 模数转换器 ..... | 83 |

| 温度传感器 ..... | 83 |

| 测试DAC.....  | 83 |

| 发射测试模式..... | 83 |

| 芯片版本回读..... | 83 |

| 应用信息.....   | 84 |

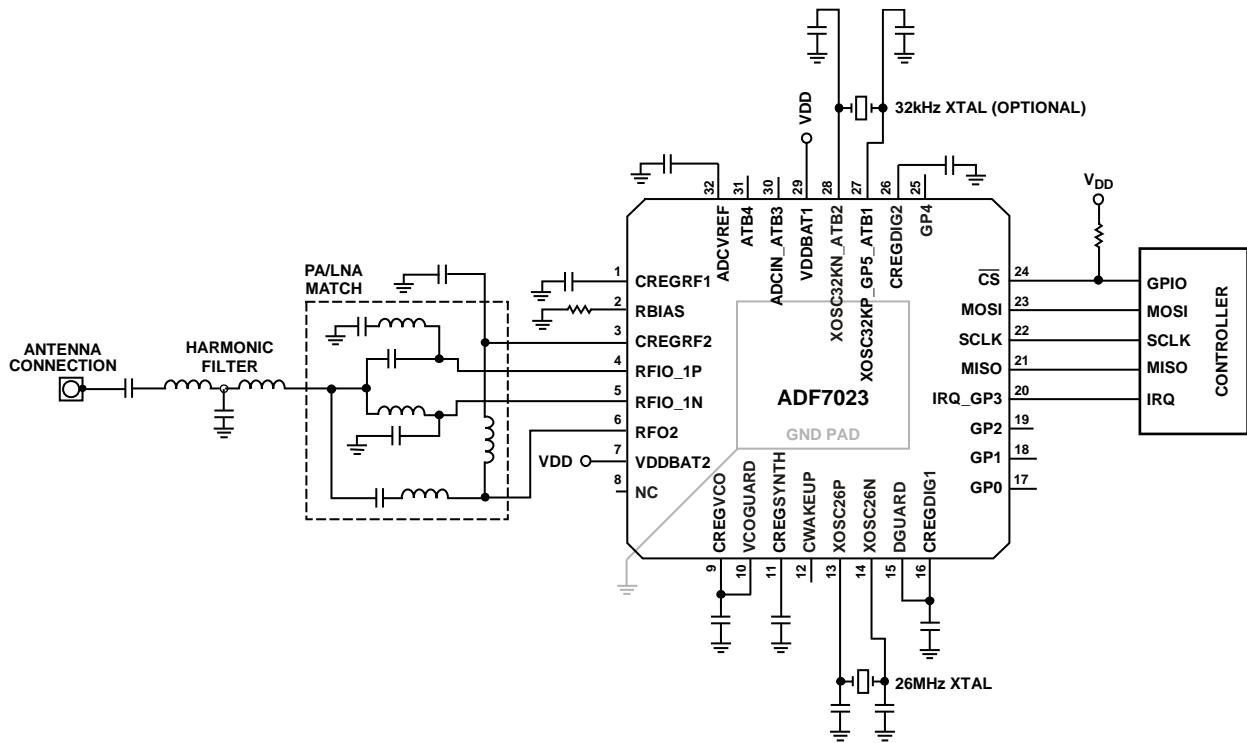

| 应用电路.....   | 84 |

|                 |     |

|-----------------|-----|

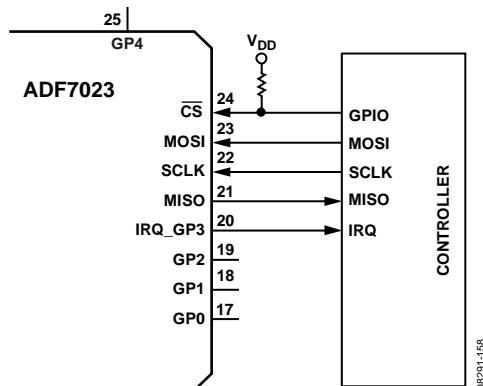

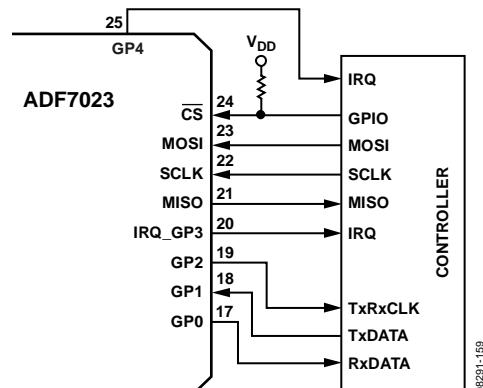

| 主机处理器接口.....    | 85  |

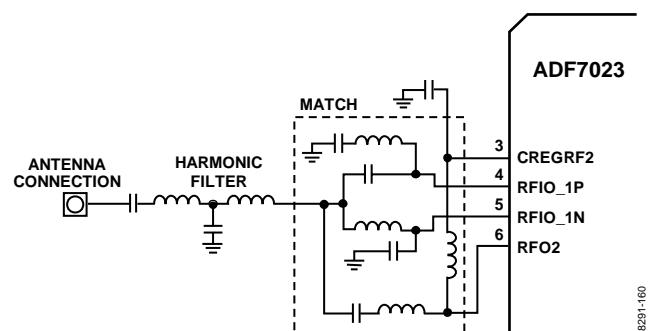

| PA/LNA匹配 .....  | 85  |

| 命令参考.....       | 87  |

| 寄存器映射.....      | 88  |

| BBRAM寄存器描述..... | 90  |

| MCR寄存器描述.....   | 100 |

| 外形尺寸 .....      | 109 |

| 订购指南.....       | 109 |

## 修订历史

### 2012年7月—修订版B至修订版C

|                                                                                           |    |

|-------------------------------------------------------------------------------------------|----|

| 更改特性部分 .....                                                                              | 1  |

| 将概述部分的1.8 V改为2.2 V.....                                                                   | 4  |

| 将表1摘要中的1.8 V改为2.2 V.....                                                                  | 6  |

| 将表2的1.8 V改为2.2 V.....                                                                     | 7  |

| 更改表3 .....                                                                                | 9  |

| 更改表5 .....                                                                                | 14 |

| 更改表6的V <sub>DD</sub> 参数 .....                                                             | 15 |

| 更改时序规格部分 .....                                                                            | 16 |

| 删除表7、图2和图3中的t <sub>1</sub> .....                                                          | 16 |

| 更改表9 .....                                                                                | 18 |

| 更改图5至图10 .....                                                                            | 20 |

| 更改图11、图12标题、图13和图14标题.....                                                                | 21 |

| 更改图19标题至图21标题.....                                                                        | 22 |

| 更改图26标题 .....                                                                             | 23 |

| 更改图34标题 .....                                                                             | 24 |

| 更改图61标题和图64标题 .....                                                                       | 29 |

| 更改图72 .....                                                                               | 31 |

| 更改PHY_SLEEP部分 .....                                                                       | 33 |

| 更改“加电后的初始化”部分、“发出CMD_HW_RESET命令后的初始化”部分、“从PHY_SLEEP跃迁时的初始化(CS拉低后)”部分、“WUC超时后的初始化”部分 ..... | 35 |

| 更改CMD_RAM_LOAD_DONE (0xC7)部分 .....                                                        | 37 |

| 删除CMD_SYNC (0xA2)部分 .....                                                                 | 37 |

| 更改“状态跃迁和命令时序”部分 .....                                                                     | 38 |

| 更改表11和表12 .....                                                                           | 39 |

| 更改“寻址”部分 .....                                                                            | 45 |

| 更改“地址检查示例”部分、表18和CRC部分 .....                                                              | 46 |

| 更改图79 .....                                                                               | 47 |

| 更改图81和图82 .....                                                                           | 50 |

| 更改图83和图84 .....                                                                           | 51 |

| 更改表24的CMD_FINISHED描述 .....                                                                | 53 |

| 更改“命令访问”部分 .....                                                                          | 56 |

| 更改图97 .....                                                                               | 63 |

| 更改表29 .....                                                                               | 68 |

|                                                 |     |

|-------------------------------------------------|-----|

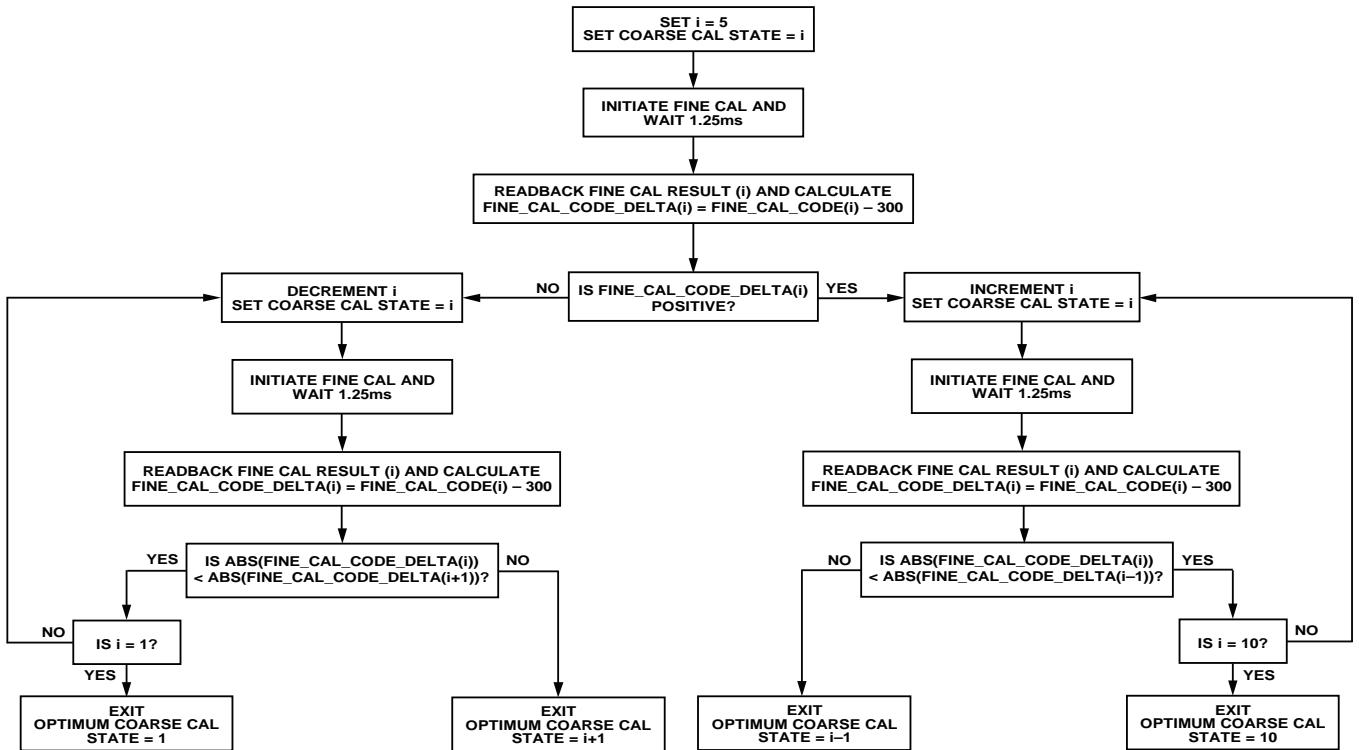

| 增加“RC振荡器校准”部分、“执行RC振荡器精校”部分和“执行RC振荡器粗校”部分 ..... | 69  |

| 增加图103；重新排序 .....                               | 70  |

| 更改“向程序RAM写入模块”部分 .....                          | 71  |

| 更改“自动PA斜坡”部分的公式和“镜像通道抑制”部分 .....                | 75  |

| 更改“温度传感器”部分和表43.....                            | 83  |

| 更改图110.....                                     | 84  |

| 更改图111和图112.....                                | 85  |

| 更改“支持外部PA和LNA控制”部分和表45 .....                    | 86  |

| 更改表46的CMD_SYNC描述栏 .....                         | 87  |

| 更改表48 .....                                     | 88  |

| 更改表49 .....                                     | 89  |

| 更改表70的SYNTH_LUT_CONTROL_1描述栏 .....              | 93  |

| 更改表78 .....                                     | 96  |

| 更改表79 .....                                     | 97  |

| 更改表84和表86 .....                                 | 98  |

| 更改表94 .....                                     | 99  |

| 增加表95、表96和表97；重新排序 .....                        | 100 |

| 更改表101 .....                                    | 101 |

| 增加表124和表125.....                                | 105 |

### 2011年3月—修订版A至修订版B

|                           |     |

|---------------------------|-----|

| 更改RSSI方法3的公式 .....        | 72  |

| 更改RSSI方法4的步骤3 .....       | 72  |

| 更改RSSI方法4的步骤5公式和近似公式..... | 73  |

| 表49增加寄存器0x361 .....       | 85  |

| 增加表129，后续重新排序 .....       | 104 |

### 2011年2月—修订版0至修订版A

|                                    |     |

|------------------------------------|-----|

| 更改表9的DGUARD描述 .....                | 18  |

| 更改“Sport接收模式”部分 .....              | 47  |

| 更改“晶振”部分、典型晶体负载电容调谐范围值和表31 ..      | 70  |

| 更改RSSI方法3部分 .....                  | 72  |

| 更改RSSI方法4部分 .....                  | 73  |

| 更改表41、9.6 kbps和1 kbps数据速率设置值 ..... | 78  |

| 更改表108的ADC_PD_N描述 .....            | 100 |

### 2010年8月—修订版0：初始版

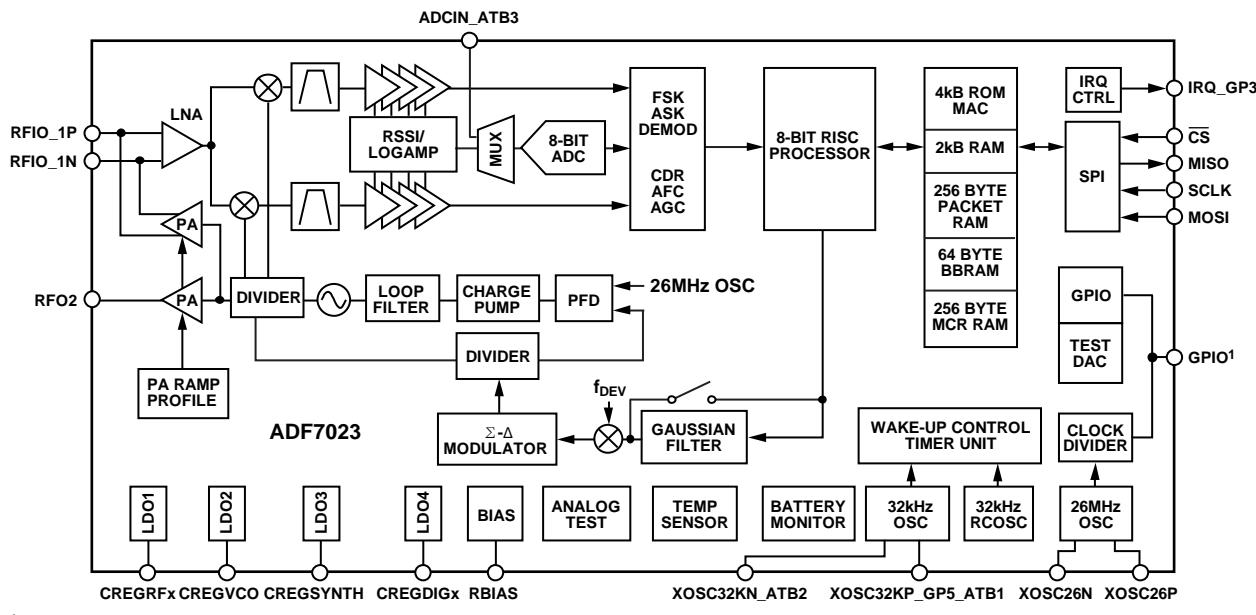

## 功能框图

<sup>1</sup>GPIO REFERS TO PINS 17, 18, 19, 20, 25, AND 27.

08291-001

图1.

## 概述

ADF7023是一款工作在862 MHz至928 MHz和431 MHz至464 MHz频段的极低功耗、高性能、高集成度2FSK/GFSK/OOK/MSK/GMSK收发器，这些频段覆盖免许可的433 MHz、868 MHz和915 MHz ISM频段。它适合欧洲ETSI EN300-220、北美FCC (Part 15)、中国短程无线监管标准或其它类似地区标准下的电路应用。支持1 kbps至300 kbps的数据速率。

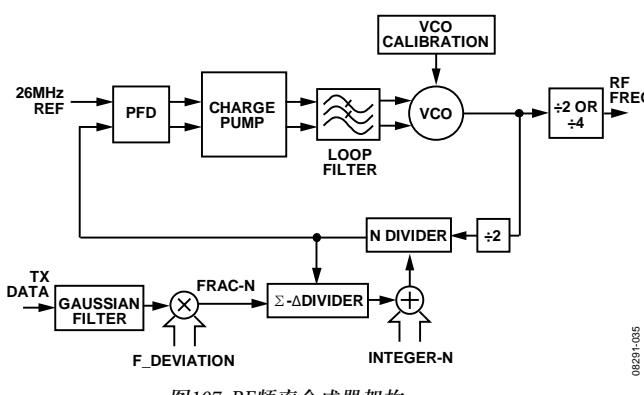

发射RF频率合成器包含一个VCO和一个输出通道频率分辨率为400 Hz的低噪声小数N分频锁相环(PLL)。VCO的工作频率为基频的2倍或4倍，可减少杂散发射。接收和发射频率合成器的带宽自动独立配置，以实现最佳的相位噪声、调制质量和建立时间。发射机输出功率可以在-20 dBm至+13.5 dBm范围内进行编程，自动PA斜坡能力可满足瞬时杂散性能要求。该器件同时拥有单端PA和差分PA，支持发射天线分集。

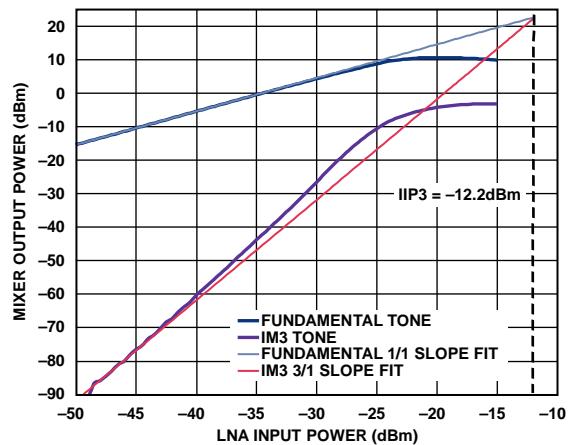

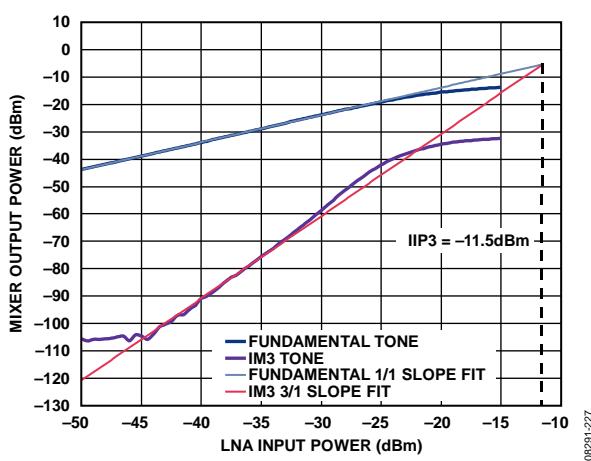

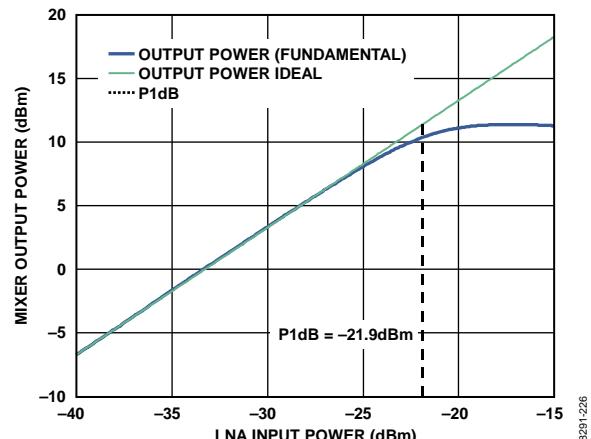

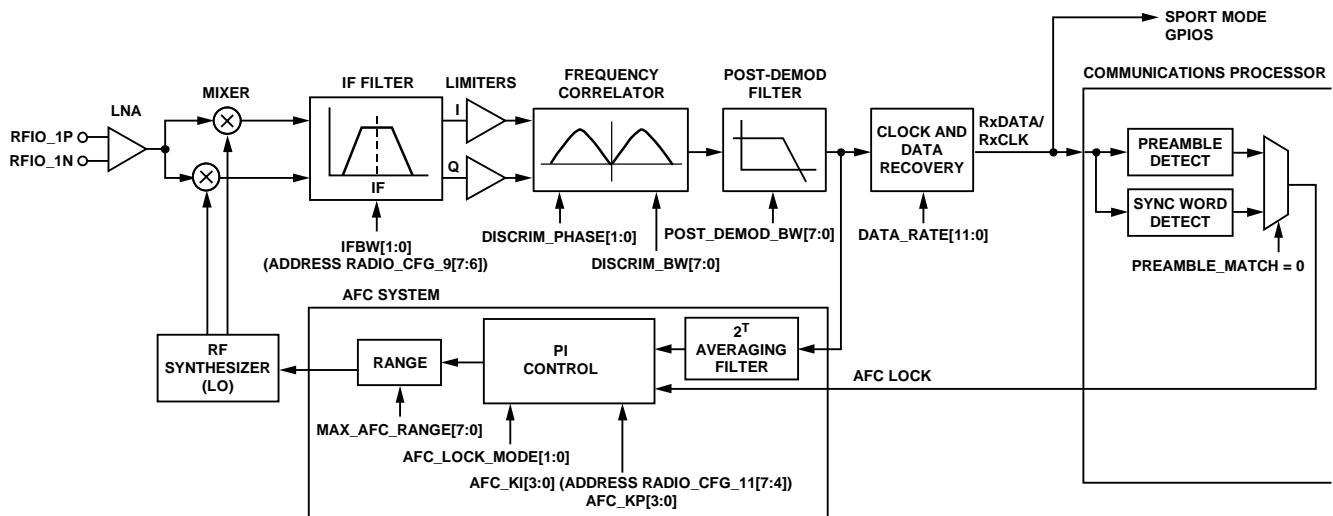

接收机具有极佳的线性度，最大增益和最小增益时的IP3分别为-12.2 dBm和-11.5 dBm，IP2分别为18.5 dBm和27 dBm。±2 MHz偏移时，接收机抗干扰性能为66 dB，±10 MHz偏移时为74 dB。因此，该器件对高频率噪声环境中的干扰信号具有极强的抗扰能力。接收机采用新颖的高速自动频率控制(AFC)环路，PLL能够发现并校正所恢复的数据包中的任何RF频率误差。

通过程序下载可以获得图像抑制校准方案，其专利正在审批中。该算法不需要使用外部RF源，启动后也不需要用户干预。校准结果可以存储在非易失性存储器中，供收发器后续上电使用。

ADF7023的电源电压范围为2.2 V至3.6 V，在Tx和Rx模式下的功耗均非常低，因此电池供电的系统在保持出色RF性能的同时，能够长时间工作。该器件可以进入低功耗休眠模式，此时配置设置保存在BBRAM中。

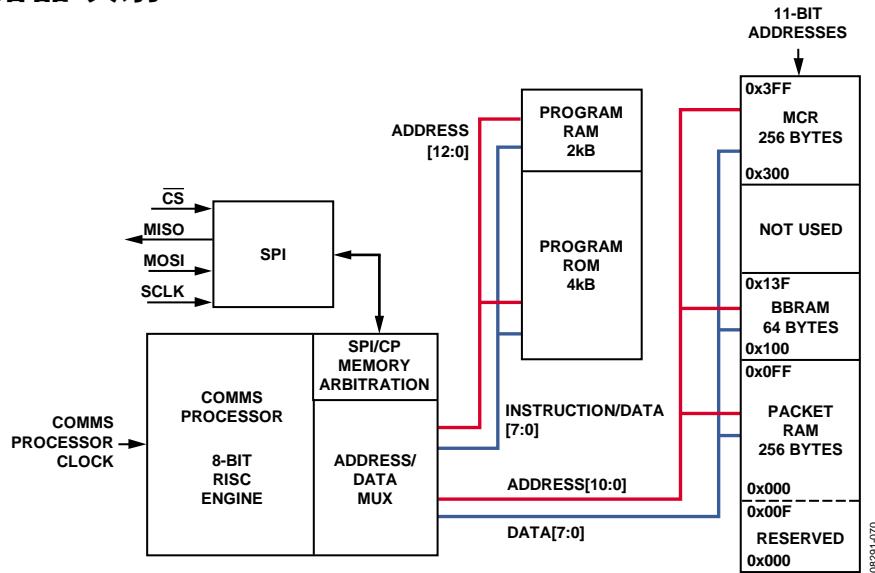

ADF7023具有一个超低功耗的片内8位RISC通信处理器，用于执行无线电控制、包管理和智能唤醒模式(SWM)功能。通信处理器集成了典型通信协议栈的较低层，可以减轻配套处理器的处理负担。利用通信处理器还能下载和执行一组固件模块，包括镜像抑制(IR)校准、AES加密和Reed Solomon编码。

通信处理器为主机处理器提供一个基于命令的简单无线电控制接口。通过单字节命令就能使无线电在不同状态之间跃迁，或者执行无线电功能。

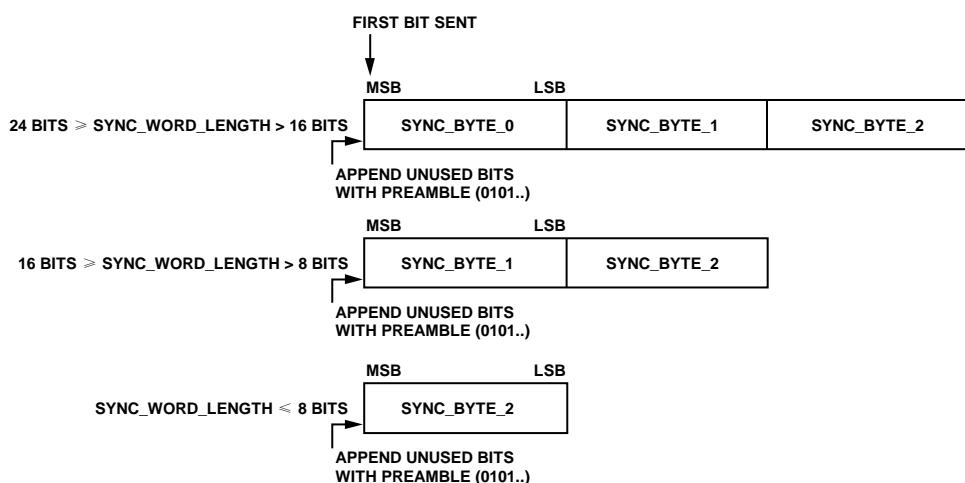

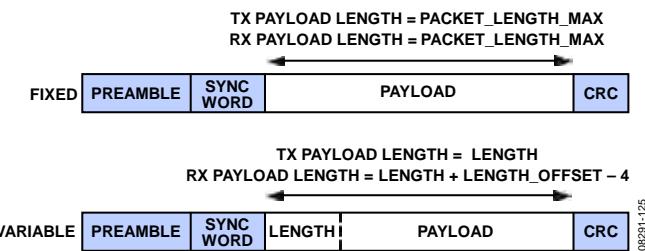

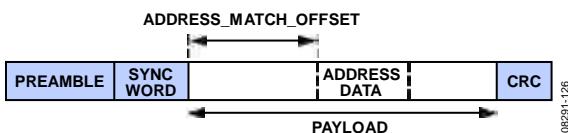

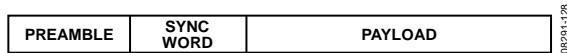

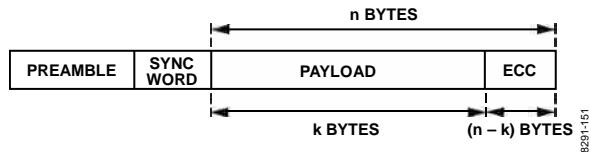

通信处理器支持通用包格式。包格式极为灵活，并且完全可编程，从而确保能与专有的包定义兼容。在发射模式下，可以将通信处理器配置为向包RAM中存储的有效载荷数据添加前同步码、同步字和CRC。在接收模式下，通信处理器可以在接收到前同步码、同步字、地址和CRC时检测和中断主机处理器，并将所接收的有效载荷存储在包RAM中。ADF7023采用一个高效中断系统，它由可以分别设置的MAC级中断和PHY级中断组成。有效载荷数据加上16位CRC可以利用曼彻斯特或8b/10b编码技术进行编码/解码，或者也可以应用数据白化和去白处理。

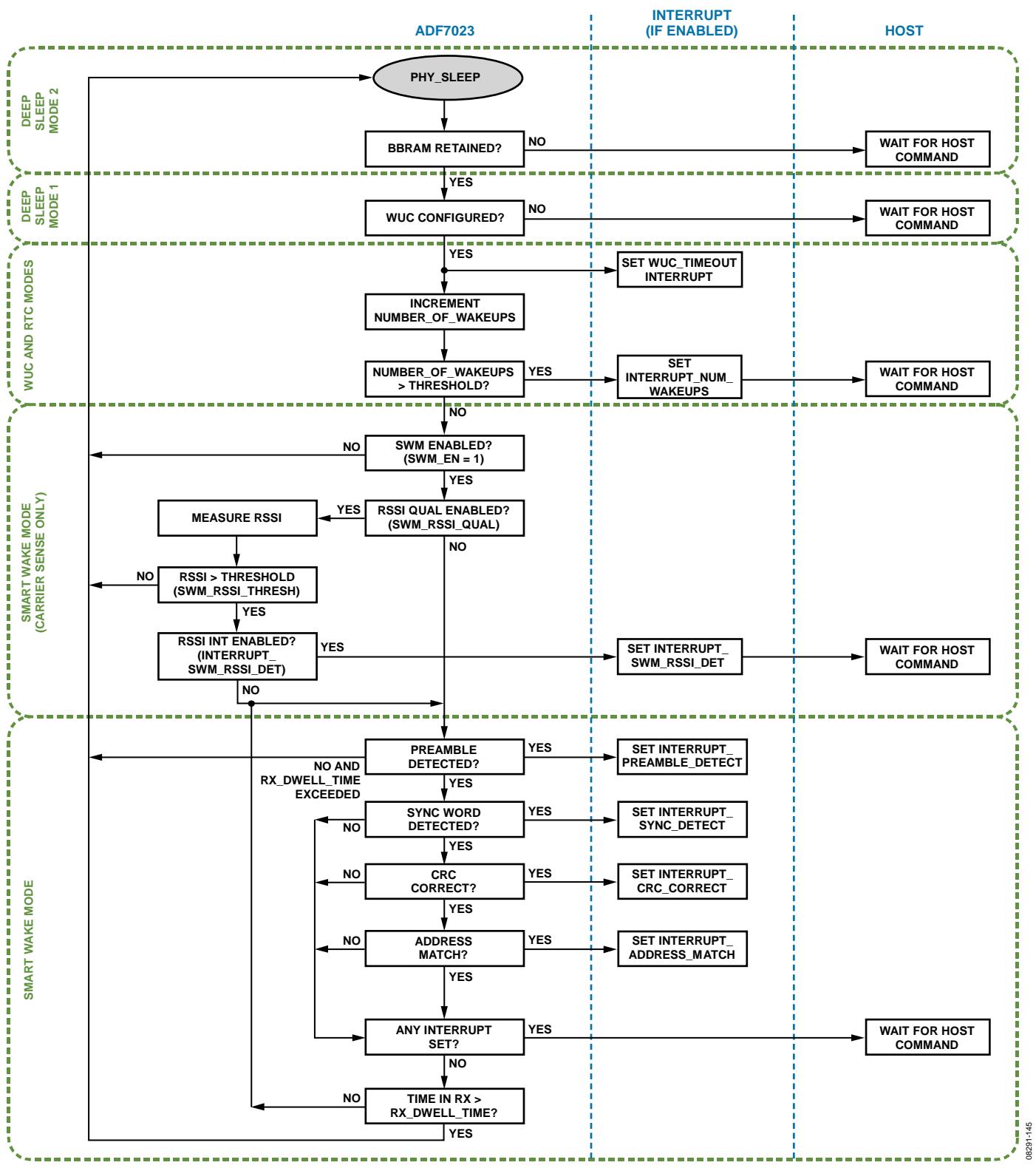

智能唤醒模式(SWM)允许ADF7023利用内部唤醒时钟从休眠状态自主唤醒，而无需主机处理器干预。唤醒后，ADF7023由通信处理器控制。利用该功能可以在主机处理器处于休眠时执行载波检测、包嗅探和包接收，从而降低系统总功耗。智能唤醒模式可以利用中断条件唤醒主机处理器。

可以对这些中断条件进行配置，使其包含有效前同步码、同步字、CRC的接收或地址匹配。从休眠模式唤醒也可以由主机处理器触发。对于要求唤醒定时非常精确的系统，可以使用一个32 kHz振荡器来驱动唤醒定时器。另外也可以使用内部RC振荡器，它在休眠模式下的功耗更低。

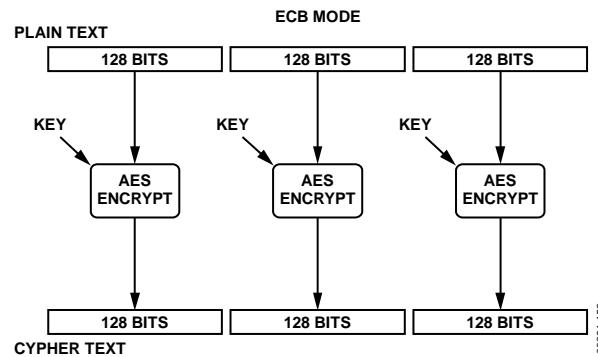

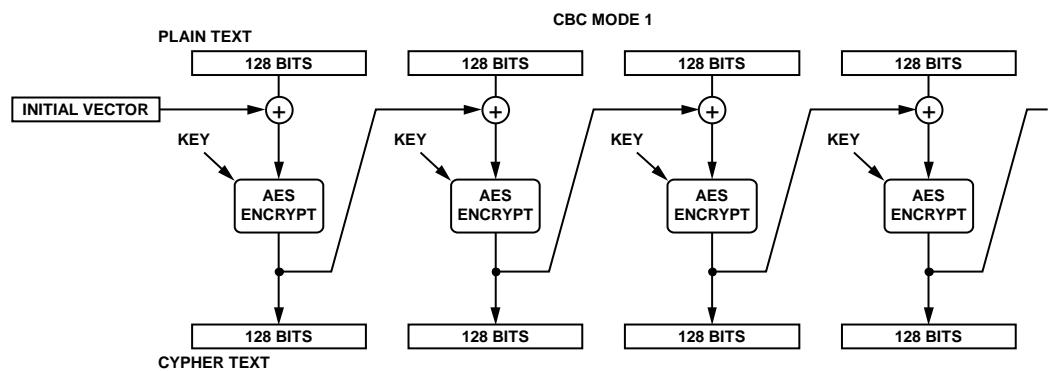

ADF7023具有一个高级加密标准(AES)引擎，采用硬件加速，提供128位块加密和解密，密钥大小为128位、192位和256位。电子密码本(ECB)和密码块链接模式1(CBC模式1)两种模式均受支持。AES引擎可以用来加密/解密包数据，并且可以用作独立引擎，用于主机处理器的加密/解密。将AES软件模块下载到程序RAM之后，ADF7023即可启用AES引擎。AES软件模块可从ADI公司获得。

片内集成的8位ADC可以回读外部模拟输入、RSSI信号或集成的温度传感器信号。一旦电池电压降至用户定义的阈值以下，集成的电池电压监控器就会向主机处理器发出一个中断标志。

## 技术规格

除非另有说明,  $V_{DD} = VDDBAT1 = VDDBAT2 = 2.2\text{ V}$ 至 $3.6\text{ V}$ ,  $GND = 0\text{ V}$ ,  $T_A = T_{MIN}$ 至 $T_{MAX}$ 。典型规格的条件:  $V_{DD} = 3\text{ V}$ ,  $T_A = 25^\circ\text{C}$ 。

### RF和频率合成器规格

表1.

| 参数              | 最小值        | 典型值        | 最大值 | 单位         | 测试条件                                                                                                     |

|-----------------|------------|------------|-----|------------|----------------------------------------------------------------------------------------------------------|

| RF特性            |            |            |     |            |                                                                                                          |

| 频率范围            | 862<br>431 | 928<br>464 |     | MHz<br>MHz |                                                                                                          |

| 锁相环             |            |            |     |            |                                                                                                          |

| 通道频率分辨率         |            | 396.7      |     | Hz         |                                                                                                          |

| 相位噪声(带内)        |            | −88        |     | dBc/Hz     | 10 kHz偏移, PA输出功率 = 10 dBm, RF频率 = 868 MHz                                                                |

| 下列偏移下的相位噪声      |            |            |     |            |                                                                                                          |

| 1 MHz           |            | −126       |     | dBc/Hz     | PA输出功率 = 10 dBm, RF频率 = 868 MHz                                                                          |

| 2 MHz           |            | −131       |     | dBc/Hz     | PA输出功率 = 10 dBm, RF频率 = 868 MHz                                                                          |

| 10 MHz          |            | −142       |     | dBc/Hz     | PA输出功率 = 10 dBm, RF频率 = 868 MHz                                                                          |

| VCO校准时间         |            | 142        |     | μs         |                                                                                                          |

| 频率合成器建立时间       |            | 56         |     | μs         | VCO校准、发射和接收之后, 频率合成器在此时间内建立到目标频率的±5 ppm以内, 2FSK/GFSK/MSK/GMSK                                            |

| 晶振              |            |            |     |            |                                                                                                          |

| 晶振频率            |            | 26         |     | MHz        | 并行负载谐振晶体                                                                                                 |

| 建议负载电容          | 7          |            | 18  | pF         |                                                                                                          |

| 最大晶振ESR         |            | 1800       |     | Ω          | 26 MHz晶振、18 pF负载电容                                                                                       |

| 引脚电容            |            | 2.1        |     | pF         | XOSC26P和XOSC26N的电容                                                                                       |

| 启动时间            |            | 310        |     | μs         | 26 MHz晶振、7 pF负载电容                                                                                        |

|                 |            | 388        |     | μs         | 26 MHz晶振、18 pF负载电容                                                                                       |

| 杂散发射            |            |            |     |            |                                                                                                          |

| 整数边界杂散          |            |            |     |            |                                                                                                          |

| 910.1 MHz       |            | −39        |     | dBc        | 采用130 kHz频率合成器带宽, 910 MHz(26 MHz × 35)下的整数边界杂散, 在频率合成器环路带宽内                                              |

| 911.0 MHz       |            | −79        |     | dBc        | 采用130 kHz频率合成器带宽, 910 MHz(26 MHz × 35)下的整数边界杂散, 在频率合成器环路带宽外                                              |

| 参考杂散            |            |            |     |            |                                                                                                          |

| 868 MHz/915 MHz |            | −80        |     | dBc        | 采用130 kHz和92 kHz(PHY_RX的默认值)频率合成器带宽                                                                      |

| 时钟相关杂散水平        |            | −60        |     | dBc        | 在±350 MHz范围内测量, 条件为: 频率合成器带宽 = 92 kHz, RF频率 = 868.95 MHz, PA输出功率 = 10 dBm, $V_{DD} = 3.6\text{ V}$ 、单端PA |

## 发射机规格

表2.

| 参数                                                                                                                               | 最小值      | 典型值                                                | 最大值         | 单位                                     | 测试条件                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------|-------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 数据速率<br>2FSK/GFSK/MSK/GMSK<br>OOK                                                                                                | 1<br>2.4 |                                                    | 300<br>19.2 | kbps<br>kbps                           | 使能曼彻斯特编码(曼彻斯特芯片速率 = 2 × 数据速率)                                                                                                                    |

| 数据速率分辨率                                                                                                                          |          | 100                                                |             | bps                                    |                                                                                                                                                  |

| 调制误差率(MER)<br>10 kbps至49.5 kbps<br>49.6 kbps至129.5 kbps<br>129.6 kbps至179.1 kbps<br>179.2 kbps至239.9 kbps<br>240 kbps至300 kbps   |          | 25.4<br>25.3<br>23.9<br>23.3<br>23                 |             | dB                                     | RF频率 = 928 MHz, GFSK<br>调制指数 = 1<br>调制指数 = 1<br>调制指数 = 0.5<br>调制指数 = 0.5<br>调制指数 = 0.5                                                           |

| 调制<br>2FSK/GFSK/MSK/GMSK<br>频率偏差<br>频率偏差分辨率<br>高斯滤波器BT                                                                           | 0.1      |                                                    | 409.5       | kHz                                    |                                                                                                                                                  |

| OOK<br>PA关闭馈通<br>VCO频率牵引                                                                                                         |          | 100<br>0.5                                         |             | Hz                                     | 不可编程                                                                                                                                             |

| 单端PA<br>最大功率 <sup>1</sup><br>最小功率<br>发射功率变化和<br>温度的关系<br>发射功率变化与V <sub>DD</sub> 的关系<br>发射功率平坦度<br>可编程阶跃信号幅度<br>-20 dBm至+13.5 dBm |          | 13.5<br>-20<br>±0.5<br>±1<br>±1                    |             | dBm<br>kHz<br>rms                      | 数据速率 = 19.2 kbps<br>(38.4 kcps曼彻斯特编码),<br>PA输出 = 10 dBm, PA斜坡速率 = 64 码/位                                                                         |

| 差分PA<br>最大功率 <sup>1</sup><br>最小功率<br>发射功率变化和<br>温度的关系<br>发射功率变化与V <sub>DD</sub> 的关系<br>发射功率平坦度<br>可编程阶跃信号幅度<br>-20 dBm至+10 dBm   |          | 10<br>-20<br>±1<br>±2<br>±1                        |             | dBm<br>dBm<br>dB<br>dB<br>dB           | 可编程、单独的PA与LNA匹配 <sup>2</sup><br>从-40°C到+85°C, RF频率 = 868 MHz<br>从2.2 V至3.6 V, RF频率 = 868 MHz<br>902 MHz至928 MHz和863 MHz<br>至870 MHz<br>可分63个阶跃编程 |

| 谐波<br>单端PA<br>二次谐波<br>三次谐波<br>所有其他谐波<br>差分PA<br>二次谐波<br>三次谐波<br>所有其他谐波                                                           |          |                                                    |             |                                        | 868 MHz, 未滤波导通,<br>PA输出功率 = 10 dBm                                                                                                               |

|                                                                                                                                  |          | -15.1<br>-29.3<br>-47.6<br>-23.2<br>-25.2<br>-24.2 |             | dBc<br>dBc<br>dBc<br>dBc<br>dBc<br>dBc |                                                                                                                                                  |

# ADF7023

| 参数                         | 最小值           | 典型值 | 最大值 | 单位       | 测试条件                                |

|----------------------------|---------------|-----|-----|----------|-------------------------------------|

| 最佳PA负载阻抗                   |               |     |     |          |                                     |

| 单端PA, 发射模式                 |               |     |     |          |                                     |

| $f_{RF} = 915 \text{ MHz}$ | 50.8 + j10.2  |     |     | $\Omega$ |                                     |

| $f_{RF} = 868 \text{ MHz}$ | 45.5 + j12.1  |     |     | $\Omega$ |                                     |

| $f_{RF} = 433 \text{ MHz}$ | 46.8 + j19.9  |     |     | $\Omega$ |                                     |

| 单端PA, 接收模式                 |               |     |     |          |                                     |

| $f_{RF} = 915 \text{ MHz}$ | 9.4 - j124    |     |     | $\Omega$ |                                     |

| $f_{RF} = 868 \text{ MHz}$ | 9.5 - j130.6  |     |     | $\Omega$ |                                     |

| $f_{RF} = 433 \text{ MHz}$ | 11.9 - j260.1 |     |     | $\Omega$ |                                     |

| 差分PA, 发射模式                 |               |     |     |          | RFIO_1P与RFIO_1N之间的负载阻抗,<br>确保最大输出功率 |

| $f_{RF} = 915 \text{ MHz}$ | 20.5 + j36.4  |     |     | $\Omega$ |                                     |

| $f_{RF} = 868 \text{ MHz}$ | 24.7 + j36.5  |     |     | $\Omega$ |                                     |

| $f_{RF} = 433 \text{ MHz}$ | 55.6 + j81.5  |     |     | $\Omega$ |                                     |

<sup>1</sup> 按最大末调制功率测定。

<sup>2</sup> 合并单端PA和LNA匹配可将可实现的最大输出功率降低多达1 dB。

## 接收机规格

表3.

| 参数                                 | 最小值    | 典型值 | 最大值 | 单位  | 测试条件                                                                                                      |

|------------------------------------|--------|-----|-----|-----|-----------------------------------------------------------------------------------------------------------|

| 2FSK/GFSK/MSK/GMSK输入灵敏度，比特误差率(BER) |        |     |     |     | BER = 1E - 3, RF频率 = 433 MHz、868 MHz、915 MHz, LNA和PA单独匹配 <sup>1</sup>                                     |

| 1.0 kbps                           | -116   |     |     | dBm | 频率偏差 = 4.8 kHz,<br>IF滤波器带宽 = 100 kHz                                                                      |

| 10 kbps                            | -111   |     |     | dBm | 频率偏差 = 9.6 kHz,<br>IF滤波器带宽 = 100 kHz                                                                      |

| 38.4 kbps                          | -107.5 |     |     | dBm | 频率偏差 = 20 kHz,<br>IF滤波器带宽 = 100 kHz                                                                       |

| 50 kbps                            | -106.5 |     |     | dBm | 频率偏差 = 12.5 kHz,<br>IF滤波器带宽 = 100 kHz                                                                     |

| 100 kbps                           | -105   |     |     | dBm | 频率偏差 = 25 kHz,<br>IF滤波器带宽 = 100 kHz                                                                       |

| 150 kbps                           | -104   |     |     | dBm | 频率偏差 = 37.5 kHz,<br>IF滤波器带宽 = 150 kHz                                                                     |

| 200 kbps                           | -103   |     |     | dBm | 频率偏差 = 50 kHz,<br>IF滤波器带宽 = 200 kHz                                                                       |

| 300 kbps                           | -100.5 |     |     | dBm | 频率偏差 = 75 kHz,<br>IF滤波器带宽 = 300 kHz                                                                       |

| 2FSK/GFSK/MSK/GMSK输入灵敏度，包误差率(PER)  |        |     |     |     | PER = 1%, RF频率 = 433 MHz、868 MHz、915 MHz, LNA和PA单独匹配 <sup>1</sup> ,<br>包长度 = 128位, 包模式                    |

| 1.0 kbps                           | -115.5 |     |     | dBm | 频率偏差 = 4.8 kHz,<br>IF滤波器带宽 = 100 kHz                                                                      |

| 9.6 kbps                           | -110.6 |     |     | dBm | 频率偏差 = 9.6 kHz,<br>IF滤波器带宽 = 100 kHz                                                                      |

| 38.4 kbps                          | -106   |     |     | dBm | 频率偏差 = 20 kHz,<br>IF滤波器带宽 = 100 kHz                                                                       |

| 50 kbps                            | -104.3 |     |     | dBm | 频率偏差 = 12.5 kHz,<br>IF滤波器带宽 = 100 kHz                                                                     |

| 100 kbps                           | -102.6 |     |     | dBm | 频率偏差 = 25 kHz,<br>IF滤波器带宽 = 100 kHz                                                                       |

| 150 kbps                           | -101   |     |     | dBm | 频率偏差 = 37.5 kHz,<br>IF滤波器带宽 = 150 kHz                                                                     |

| 200 kbps                           | -99.1  |     |     | dBm | 频率偏差 = 50 kHz,<br>IF滤波器带宽 = 200 kHz                                                                       |

| 300 kbps                           | -97.9  |     |     | dBm | 频率偏差 = 75 kHz,<br>IF滤波器带宽 = 300 kHz                                                                       |

| OOK输入灵敏度，包误差率(PER)                 |        |     |     |     | PER = 1%, RF频率 = 433 MHz、868 MHz、915 MHz, LNA和PA单独匹配 <sup>1</sup> ,<br>包长度 = 128位, 包模式, IF滤波器带宽 = 100 kHz |

| 19.2 kbps(38.4 kcps,<br>曼彻斯特编码)    | -104.7 |     |     | dBm |                                                                                                           |

| 2.4 kbps(4.8 kcps,<br>曼彻斯特编码)      | -109.7 |     |     | dBm |                                                                                                           |

| LNA和混频器, 输入IP3                     |        |     |     |     | 接收机LO频率( $f_{LO}$ ) = 914.8 MHz,<br>$f_{SOURCE1} = f_{LO} + 0.4$ MHz, $f_{SOURCE2} = f_{LO} + 0.7$ MHz    |

| 最小LNA增益                            | -11.5  |     |     | dBm |                                                                                                           |

| 最大LNA增益                            | -12.2  |     |     | dBm |                                                                                                           |

| LNA和混频器, 输入IP2                     |        |     |     |     | 接收机LO频率( $f_{LO}$ ) = 920.8 MHz,<br>$f_{SOURCE1} = f_{LO} + 1.1$ MHz, $f_{SOURCE2} = f_{LO} + 1.3$ MHz    |

| 最大LNA增益, 最大混频器增益                   | 18.5   |     |     | dBm |                                                                                                           |

| 最小LNA增益, 最小混频器增益                   | 27     |     |     | dBm |                                                                                                           |

# ADF7023

| 参数                       | 最小值   | 典型值 | 最大值 | 单位  | 测试条件                                                                                                                                              |

|--------------------------|-------|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

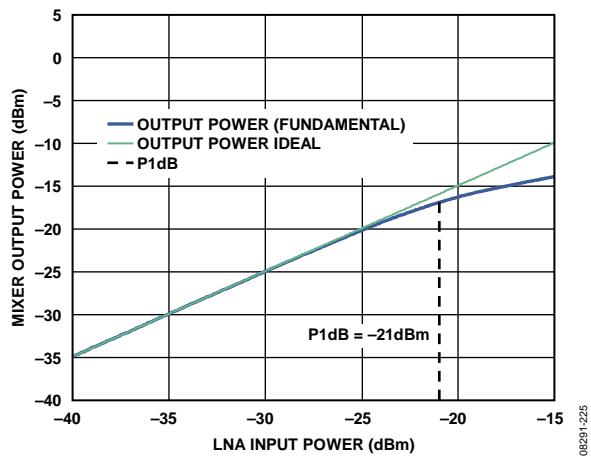

| LNA和混频器，<br>1 dB压缩点      |       |     |     |     | RF频率 = 915 MHz                                                                                                                                    |

| 最大LNA增益，最大混频器增益          | -21.9 |     |     | dBm |                                                                                                                                                   |

| 最小LNA增益，最小混频器增益          | -21   |     |     | dBm |                                                                                                                                                   |

| 邻道抑制<br>CW干扰源            |       |     |     |     | 所需信号超过输入灵敏度水平<br>3 dB (BER = 10 <sup>-3</sup> )； CW干扰强度<br>递增直至BER = 10 <sup>-3</sup> ，镜像校准                                                       |

| 200 kHz通道间隔              | 38    |     |     | dB  | IF带宽 = 100 kHz，所需信号：F <sub>DEV</sub> = 12.5 kHz,<br>数据速率 = 50 kbps                                                                                |

| 300 kHz通道间隔              | 39    |     |     | dB  | IF带宽 = 100 kHz，所需信号：F <sub>DEV</sub> = 25 kHz,<br>数据速率 = 100 kbps                                                                                 |

|                          | 38    |     |     | dB  | IF带宽 = 150 kHz，所需信号：F <sub>DEV</sub> = 37.5 kHz,<br>数据速率 = 150 kbps                                                                               |

| 400 kHz通道间隔              | 40    |     |     | dB  | IF带宽 = 200 kHz，所需信号：F <sub>DEV</sub> = 50 kHz,<br>数据速率 = 200 kbps                                                                                 |

| 600 kHz通道间隔              | 41    |     |     | dB  | IF带宽 = 300 kHz，所需信号：F <sub>DEV</sub> = 75 kHz,<br>数据速率 = 300 kbps                                                                                 |

| 调制干扰源                    |       |     |     |     | 所需信号超过输入灵敏度水平3 dB (BER = 10 <sup>-3</sup> ),<br>调制干扰源与所需信号的调制相同；干扰强度<br>递增直至BER = 10 <sup>-3</sup> ，镜像校准                                          |

| 200 kHz通道间隔              | 38    |     |     | dB  | IF带宽 = 100 kHz，所需信号：F <sub>DEV</sub> = 12.5 kHz,<br>数据速率 = 50 kbps                                                                                |

| 300 kHz通道间隔              | 36    |     |     | dB  | IF带宽 = 100 kHz，所需信号：F <sub>DEV</sub> = 25 kHz,<br>数据速率 = 100 kbps                                                                                 |

| 300 kHz通道间隔              | 36    |     |     | dB  | IF带宽 = 150 kHz，所需信号：F <sub>DEV</sub> = 37.5 kHz,<br>数据速率 = 150 kbps                                                                               |

| 400 kHz通道间隔              | 34    |     |     | dB  | IF带宽 = 200 kHz，所需信号：F <sub>DEV</sub> = 50 kHz,<br>数据速率 = 200 kbps                                                                                 |

| 600 kHz通道间隔              | 35    |     |     | dB  | IF带宽 = 300 kHz，所需信号：F <sub>DEV</sub> = 75 kHz,<br>数据速率 = 300 kbps                                                                                 |

| 同道抑制                     | -4    |     |     | dB  | 所需信号超过输入灵敏度水平10 dB (BER = 10 <sup>-3</sup> ),<br>数据速率 = 38.4 kbps，频率偏差 = 20 kHz,<br>RF频率 = 868 MHz                                                |

| 阻塞                       |       |     |     |     | 所需信号超过-107.5 dBm(数据速率 = 38.4 kbps)<br>的输入灵敏度水平3 dB (BER = 10 <sup>-3</sup> )，调制干扰强度<br>递增直至BER = 10 <sup>-3</sup> (其它偏移和IF带宽下的<br>阻塞参见“典型工作特性”部分) |

| RF频率 = 433 MHz<br>±2 MHz | 68    |     |     | dB  |                                                                                                                                                   |

| ±10 MHz                  | 76    |     |     | dB  |                                                                                                                                                   |

| RF频率 = 868 MHz<br>±2 MHz | 66    |     |     | dB  |                                                                                                                                                   |

| ±10 MHz                  | 74    |     |     | dB  |                                                                                                                                                   |

| RF频率 = 915 MHz<br>±2 MHz | 66    |     |     | dB  |                                                                                                                                                   |

| ±10 MHz                  | 74    |     |     | dB  |                                                                                                                                                   |

| 参数                           | 最小值     | 典型值 | 最大值 | 单位   | 测试条件                                                                                                                                                          |

|------------------------------|---------|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 阻塞, ETSI EN 300 220          |         |     |     |      | 测量程序根据ETSI EN 300 220-1 V2.3.1; 所需信号超过-99 dBm的ETSI EN 300 220参考灵敏度水平3 dB, IF带宽 = 100 kHz, 数据速率 = 38.4 kbps, 未调制干扰源; 其它偏移和IF带宽下的阻塞参见“典型工作特性”部分, RF频率 = 868 MHz |

| ±2 MHz                       | -28     |     |     | dBm  |                                                                                                                                                               |

| ±10 MHz                      | -20.5   |     |     | dBm  |                                                                                                                                                               |

| 宽带干扰抑制                       | 75      |     |     | dB   | RF频率 = 868 MHz, 扫描范围从10 MHz到100 MHz, 在RF频率的任一侧                                                                                                                |

| 镜像通道衰减                       |         |     |     |      | 测量IF滤波器输出端的镜像衰减, 载波干扰源低于通道频率400 kHz, 100 kHz IF滤波器带宽                                                                                                          |

| 868 MHz, 915 MHz             | 36/45   |     |     | dB   | 未校准/校准                                                                                                                                                        |

| 433 MHz                      | 40/54   |     |     | dB   | 未校准/校准                                                                                                                                                        |

| 自动频率控制                       |         |     |     |      |                                                                                                                                                               |

| 精度                           | 1       |     |     | kHz  |                                                                                                                                                               |

| 最大捕捉范围                       |         |     |     |      | 可实现的捕捉范围取决于鉴频器带宽和调制                                                                                                                                           |

| 300 kHz IF滤波器带宽              | ±150    |     |     | kHz  |                                                                                                                                                               |

| 200 kHz IF滤波器带宽              | ±100    |     |     | kHz  |                                                                                                                                                               |

| 150 kHz IF滤波器带宽              | ±75     |     |     | kHz  |                                                                                                                                                               |

| 100 kHz IF滤波器带宽              | ±50     |     |     | kHz  |                                                                                                                                                               |

| 前同步码长度                       |         |     |     |      | 前同步码最低位数, 确保在整个输入功率范围内实现最低包误差率                                                                                                                                |

| AFC关闭, 检测到同步字时<br>AGC锁定      |         |     |     |      |                                                                                                                                                               |

| 38.4 kbps                    | 8       |     |     | Bits |                                                                                                                                                               |

| 300 kbps                     | 24      |     |     | Bits |                                                                                                                                                               |

| AFC开启, 检测到前同步码时<br>AFC和AGC锁定 |         |     |     |      |                                                                                                                                                               |

| 9.6 kbps                     | 44      |     |     | Bits |                                                                                                                                                               |

| 38.4 kbps                    | 44      |     |     | Bits |                                                                                                                                                               |

| 50 kbps                      | 50      |     |     | Bits |                                                                                                                                                               |

| 100 kbps                     | 52      |     |     | Bits |                                                                                                                                                               |

| 150 kbps                     | 54      |     |     | Bits |                                                                                                                                                               |

| 200 kbps                     | 58      |     |     | Bits |                                                                                                                                                               |

| 300 kbps                     | 64      |     |     | Bits |                                                                                                                                                               |

| AFC开启, 检测到同步字时<br>AFC和AGC锁定  |         |     |     |      |                                                                                                                                                               |

| 38.4 kbps                    | 14      |     |     | Bits |                                                                                                                                                               |

| 300 kbps                     | 32      |     |     | Bits |                                                                                                                                                               |

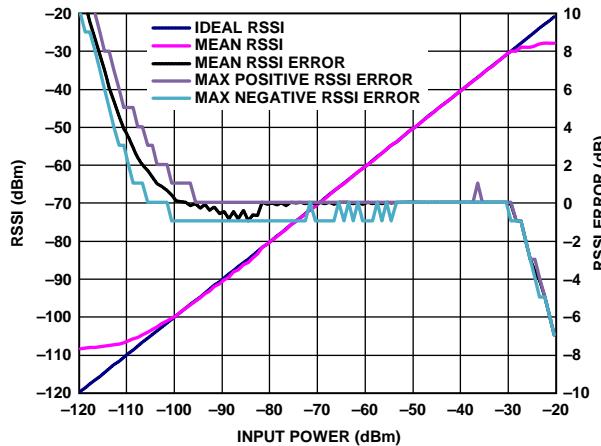

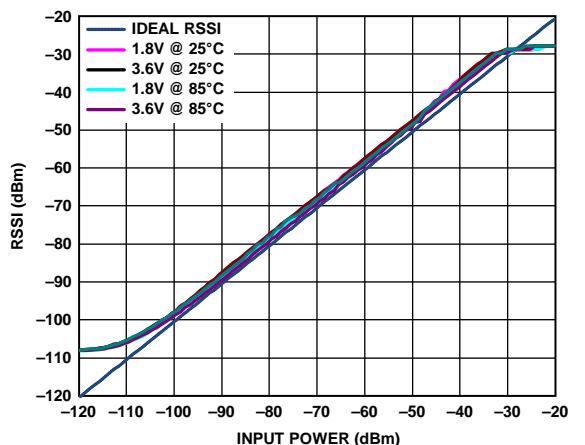

| RSSI                         |         |     |     |      |                                                                                                                                                               |

| 输入端范围                        | -97至-26 |     |     | dBm  |                                                                                                                                                               |

| 线性度                          | ±2      |     |     | dB   |                                                                                                                                                               |

| 绝对精度                         | ±3      |     |     | dB   |                                                                                                                                                               |

| 饱和(最大输入电平)                   |         |     |     |      |                                                                                                                                                               |

| 2FSK/GFSK/MSK/GMSK           | 12      |     |     | dBm  |                                                                                                                                                               |

| OOK                          | -13     |     |     | dBm  | OOK调制深度 = 20 dB                                                                                                                                               |

|                              | 10      |     |     | dBm  | OOK调制深度 = 60 dB                                                                                                                                               |

# ADF7023

| 参数                         | 最小值  | 典型值      | 最大值 | 单位           | 测试条件         |

|----------------------------|------|----------|-----|--------------|--------------|

| LNA输入阻抗                    |      |          |     |              |              |

| 接收模式                       |      |          |     |              |              |

| $f_{RF} = 915 \text{ MHz}$ | 75.9 | $-j32.3$ |     | $\Omega$     |              |

| $f_{RF} = 868 \text{ MHz}$ | 78.0 | $-j32.4$ |     | $\Omega$     |              |

| $f_{RF} = 433 \text{ MHz}$ | 95.5 | $-j23.9$ |     | $\Omega$     |              |

| 发射模式                       |      |          |     |              |              |

| $f_{RF} = 915 \text{ MHz}$ | 7.6  | $+j9.2$  |     | $\Omega$     |              |

| $f_{RF} = 868 \text{ MHz}$ | 7.7  | $+j8.6$  |     | $\Omega$     |              |

| $f_{RF} = 433 \text{ MHz}$ | 7.9  | $+j4.6$  |     | $\Omega$     |              |

| RX杂散发射 <sup>2</sup>        |      |          |     |              |              |

| 最大值 $< 1 \text{ GHz}$      | -66  |          |     | $\text{dBm}$ | 天线输入处, 未滤波导通 |

| 最大值 $> 1 \text{ GHz}$      | -62  |          |     | $\text{dBm}$ | 天线输入处, 未滤波导通 |

<sup>1</sup> 合并匹配网络的灵敏度通常比单独匹配网络低1 dB。

<sup>2</sup> 请遵循匹配和布局布线指南以达到相关的FCC/ETSI规格。

## 时序和数字规格

表4.

| 参数                              | 最小值                 | 典型值                 | 最大值 | 单位 | 测试条件                    |

|---------------------------------|---------------------|---------------------|-----|----|-------------------------|

| RX和TX时序参数                       |                     |                     |     |    | 更多信息参见“状态跃迁和命令时序”部分。    |

| PHY_ON至PHY_RX(CMD_PHY_RX时)      | 300                 |                     |     | μs | 包括VCO校准和频率合成器建立         |

| PHY_ON至PHY_TX(CMD_PHY_TX时)      | 296                 |                     |     | μs | 包括VCO校准和频率合成器建立，不包括PA斜升 |

| 逻辑输入                            |                     |                     |     |    |                         |

| 输入高电压 $V_{INH}$                 | $0.7 \times V_{DD}$ |                     |     | V  |                         |

| 输入低电压 $V_{INL}$                 |                     | $0.2 \times V_{DD}$ |     | V  |                         |

| 输入电流 $I_{INH}/I_{INL}$          |                     | $\pm 1$             |     | μA |                         |

| 输入电容 $C_{IN}$                   |                     | 10                  |     | pF |                         |

| 逻辑输出                            |                     |                     |     |    |                         |

| 输出高电压 $V_{OH}$                  | $V_{DD} - 0.4$      |                     |     | V  |                         |

| 输出低电压 $V_{OL}$                  |                     | 0.4                 |     | V  | $I_{OH} = 500 \mu A$    |

| GPIO上升/下降                       |                     | 5                   |     | ns | $I_{OL} = 500 \mu A$    |

| GPIO负载                          |                     |                     | 10  | pF |                         |

| 最大输出电流                          |                     | 5                   |     | mA |                         |

| ATB输出                           |                     |                     |     |    | 用于外部PA和LNA控制            |

| ADCIN_ATB3和ATB4                 |                     |                     |     |    |                         |

| 输出高电压 $V_{OH}$                  |                     | 1.8                 |     | V  |                         |

| 输出低电压 $V_{OL}$                  |                     | 0.1                 |     | V  |                         |

| 最大输出电流                          |                     | 0.5                 |     | mA |                         |

| XOSC32KP_GP5_ATB1和XOSC32KN_ATB2 |                     |                     |     |    |                         |

| 输出高电压 $V_{OH}$                  |                     | $V_{DD}$            |     | V  |                         |

| 输出低电压 $V_{OL}$                  |                     | 0.1                 |     | V  |                         |

| 最大输出电流                          |                     | 5                   |     | mA |                         |

## 辅助模块技术规格

表5.

| 参数             | 最小值                 | 典型值    | 最大值                | 单位   | 测试条件                                            |

|----------------|---------------------|--------|--------------------|------|-------------------------------------------------|

| 32 kHz RC振荡器   |                     |        |                    |      |                                                 |

| 频率             |                     | 32.768 |                    | kHz  | 校准后                                             |

| 频率精度           |                     | 1.5    |                    | %    | 25°C时校准后                                        |

| 频率漂移           |                     |        |                    |      |                                                 |

| 温度系数           |                     | 0.14   |                    | %/°C |                                                 |

| 电压系数           |                     | 4      |                    | %/V  |                                                 |

| 校准时间           |                     | 1.25   |                    | ms   |                                                 |

| 32 kHz XTAL振荡器 |                     |        |                    |      |                                                 |

| 频率             |                     | 32.768 |                    | kHz  |                                                 |

| 启动时间           |                     | 630    |                    | ms   | 32.768 kHz晶振、7 pF负载电容                           |

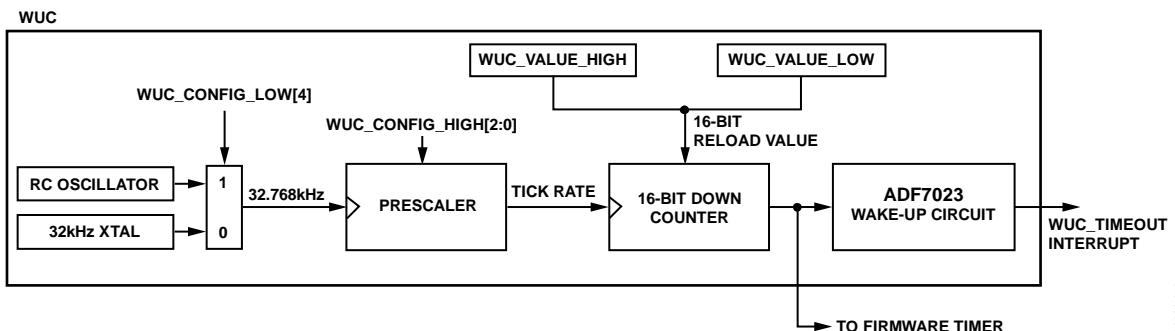

| 唤醒控制器(WUC)     |                     |        |                    |      |                                                 |

| 硬件定时器          |                     |        |                    |      |                                                 |

| 唤醒周期           | $61 \times 10^{-6}$ |        | $1.31 \times 10^5$ | 秒    |                                                 |

| 固件定时器          |                     |        |                    |      |                                                 |

| 唤醒周期           | 1                   |        | $2^{16}$           | 硬件周期 | 固件计数器计数硬件唤醒次数，<br>16位分辨率                        |

| ADC            |                     |        |                    |      |                                                 |

| 分辨率            |                     | 8      |                    | 位    |                                                 |

| 微分非线性(DNL)误差   |                     | ±1     |                    | LSB  | $V_{DD}$ 从2.2 V到3.6 V, $T_A = 25^\circ\text{C}$ |

| 积分非线性(INL)     |                     | ±1     |                    | LSB  | $V_{DD}$ 从2.2 V到3.6 V, $T_A = 25^\circ\text{C}$ |

| 转换时间           |                     | 1      |                    | μs   |                                                 |

| 输入电容           |                     | 12.4   |                    | pF   |                                                 |

| 电池监控器          |                     |        |                    |      |                                                 |

| 绝对精度           |                     | ±45    |                    | mV   |                                                 |

| 报警电压设定点        | 1.7                 |        | 2.7                | V    |                                                 |

| 报警电压阶跃信号幅度     |                     | 62     |                    | mV   | 5-bit分辨率                                        |

| 启动时间           |                     |        | 100                | μs   |                                                 |

| 功耗             |                     | 30     |                    | μA   | 使能时                                             |

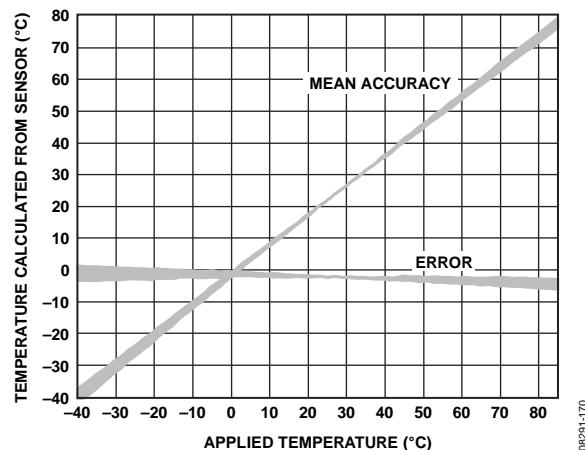

| 温度传感器          |                     |        |                    |      |                                                 |

| 范围             | -40                 |        | +85                | °C   |                                                 |

| 分辨率            |                     | 0.3    |                    | °C   | 求平均值                                            |

| 温度回读精度         |                     | +7/-4  |                    | °C   | -40°C至+85°C温度范围内<br>(校准温度+25°C)                 |

## 通用规格

表6.

| 参数                    | 最小值   | 典型值 | 最大值 | 单位 | 测试条件                                                                       |

|-----------------------|-------|-----|-----|----|----------------------------------------------------------------------------|

| 温度范围, $T_A$           | -40   | +85 | °C  |    |                                                                            |

| 电源电压<br>$V_{DD}$      | 2.2   | 3.6 | V   |    | 施加于VDBBAT1和VDBBAT2                                                         |

| 发射功耗                  |       |     |     |    | PHY_TX状态, 单端PA匹配50 Ω,<br>差分PA匹配100 Ω, 单独单端PA和<br>LNA匹配, 合并差分PA和LNA匹配       |

| 单端PA, 433 MHz         |       |     |     |    |                                                                            |

| -10 dBm               | 8.7   |     |     | mA |                                                                            |

| 0 dBm                 | 12.2  |     |     | mA |                                                                            |

| 10 dBm                | 23.3  |     |     | mA |                                                                            |

| 13.5 dBm              | 32.1  |     |     | mA |                                                                            |

| 差分PA, 433 MHz         |       |     |     |    |                                                                            |

| -10 dBm               | 7.9   |     |     | mA |                                                                            |

| 0 dBm                 | 11    |     |     | mA |                                                                            |

| 5 dBm                 | 15    |     |     | mA |                                                                            |

| 10 dBm                | 22.6  |     |     | mA |                                                                            |

| 单端PA, 868 MHz/915 MHz |       |     |     |    |                                                                            |

| -10 dBm               | 10.3  |     |     | mA |                                                                            |

| 0 dBm                 | 13.3  |     |     | mA |                                                                            |

| 10 dBm                | 24.1  |     |     | mA |                                                                            |

| 13.5 dBm              | 32.1  |     |     | mA |                                                                            |

| 差分PA, 868 MHz/915 MHz |       |     |     |    |                                                                            |

| -10 dBm               | 9.3   |     |     | mA |                                                                            |

| 0 dBm                 | 12    |     |     | mA |                                                                            |

| 5 dBm                 | 16.7  |     |     | mA |                                                                            |

| 10 dBm                | 28    |     |     | mA |                                                                            |

| 功耗模式                  |       |     |     |    |                                                                            |

| PHY_SLEEP(深度休眠模式2)    | 0.18  |     |     | μA | 休眠模式, 不保留唤醒配置值(BBRAM)                                                      |

| PHY_SLEEP(深度休眠模式1)    | 0.33  |     |     | μA | 休眠模式, 保留唤醒配置值(BBRAM)                                                       |

| PHY_SLEEP(RCO唤醒模式)    | 0.75  |     |     | μA | WUC有效, RC振荡器运行,<br>保留唤醒配置值(BBRAM)                                          |

| PHY_SLEEP(XTO唤醒模式)    | 1.28  |     |     | μA | WUC有效, 32 kHz晶振运行,<br>保留唤醒配置值(BBRAM)                                       |

| PHY_OFF               | 1     |     |     | mA | 器件处于PHY_OFF状态, 26 MHz振荡器运行,<br>数字和频率合成器有效,<br>保留所有寄存器值                     |

| PHY_ON                | 1     |     |     | mA | 器件处于PHY_ON状态, 26 MHz振荡器运行,<br>数字、频率合成器、VCO和RF调节器有效,<br>执行基带滤波器校准, 保留所有寄存器值 |

| PHY_RX                | 12.8  |     |     | mA | 器件处于PHY_RX状态                                                               |

| 智能唤醒模式                |       |     |     |    |                                                                            |

|                       | 21.78 |     |     | μA | 平均功耗<br>每隔1秒自主接收, 接收驻留时间为1.25 ms,<br>使用RC振荡器, 数据速率 = 38.4 kbps             |

|                       | 11.75 |     |     | μA | 每隔1秒自主接收, 接收驻留时间为0.5 ms,<br>使用RC振荡器, 数据速率 = 300 kbps                       |

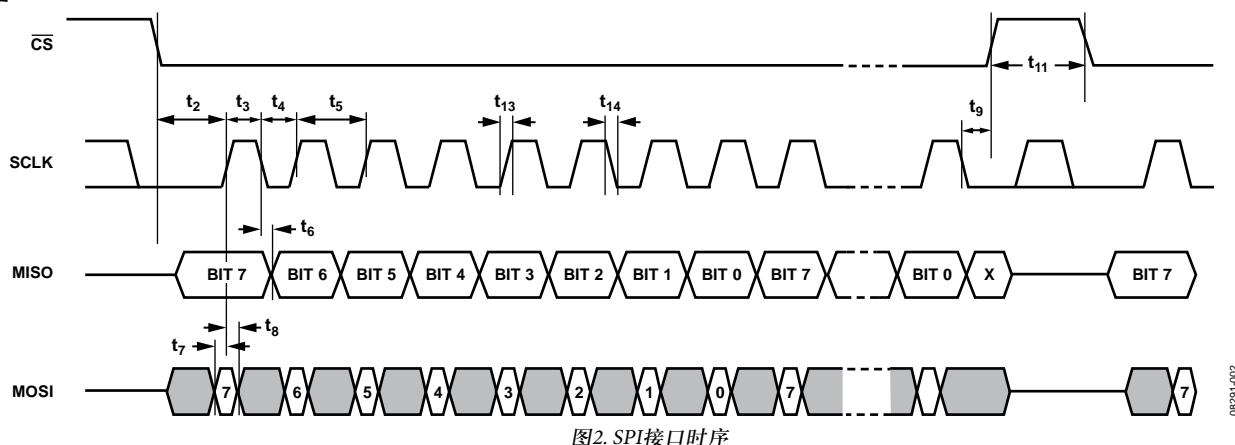

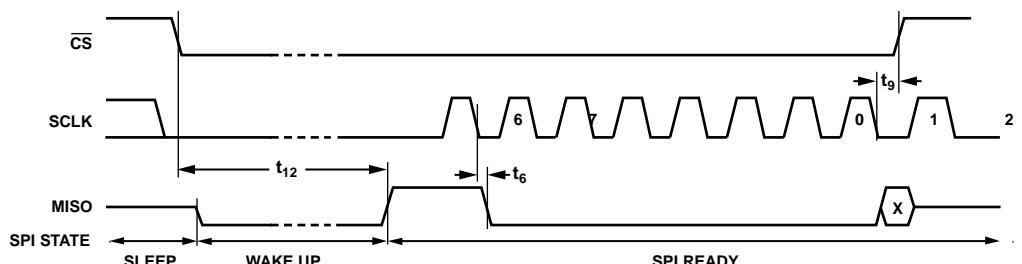

## 时序规格

除非另有说明,  $V_{DD} = VDDBAT1 = VDDBAT2 = 2.2\text{ V}$ 至 $3.6\text{ V}$ ,  $V_{GND} = GND = 0\text{ V}$ ,  $T_A = T_{MIN}$ 至 $T_{MAX}$ 。

表7. SPI接口时序

| 参数       | 限值  | 单位      | 测试条件/注释                                                          |

|----------|-----|---------|------------------------------------------------------------------|

| $t_2$    | 85  | ns(最小值) | CS 低电平到SCLK建立时间                                                  |

| $t_3$    | 85  | ns(最小值) | SCLK高电平时间                                                        |

| $t_4$    | 85  | ns(最小值) | SCLK低电平时间                                                        |

| $t_5$    | 170 | ns(最小值) | SCLK周期                                                           |

| $t_6$    | 10  | ns(最大值) | SCLK下降沿到MISO延迟时间                                                 |

| $t_7$    | 5   | ns(最小值) | MOSI到SCLK上升沿建立时间                                                 |

| $t_8$    | 5   | ns(最小值) | MOSI到SCLK上升沿保持时间                                                 |

| $t_9$    | 85  | ns(最小值) | SCLK下降沿到CS保持时间                                                   |

| $t_{11}$ | 270 | ns(最小值) | CS 高电平时间                                                         |

| $t_{12}$ | 310 | μs typ  | CS 低电平到MISO高电平唤醒时间, 带7 pF负载电容的26 MHz晶振, $T_A = 25^\circ\text{C}$ |

| $t_{13}$ | 20  | ns(最大值) | SCLK上升时间                                                         |

| $t_{14}$ | 20  | ns(最大值) | SCLK下降时间                                                         |

## 时序图

图2. SPI接口时序

08291-002

图3. PHY\_SLEEP到SPI就绪状态时序(CS下降沿后的SPI就绪T12)

08291-003

## 绝对最大额定值

除非另有说明,  $T_A = 25^\circ\text{C}$ 。

表8.

| 参数                       | 额定值            |

|--------------------------|----------------|

| VDDBAT1、VDDBAT2至GND      | -0.3 V至+3.96 V |

| 工业温度范围                   | -40°C至+85°C    |

| 存储温度范围                   | -65°C至+125°C   |

| 最高结温                     | 150°C          |

| LFCSP封装 $\theta_{JA}$ 热阻 | 26°C/W         |

| 回流焊                      |                |

| 峰值温度                     | 260°C          |

| 峰值温度时间                   | 40秒            |

注意, 超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定最值, 并不能以这些条件或者在任何其它超出本技术规范操作章节中所示规格的条件下, 推断器件能否正常工作。长期在绝对最大额定值条件下工作会影响器件的可靠性。

LFCSP封装的底部焊盘应连接到地。

本器件为高性能RF集成电路, ESD额定值小于2 kV, 对ESD(静电放电)敏感。搬运和装配时应采取适当的防范措施。

### ESD警告

#### ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路, 但在遇到高能量ESD时, 器件可能会损坏。因此, 应当采取适当的ESD防范措施, 以避免器件性能下降或功能丧失。

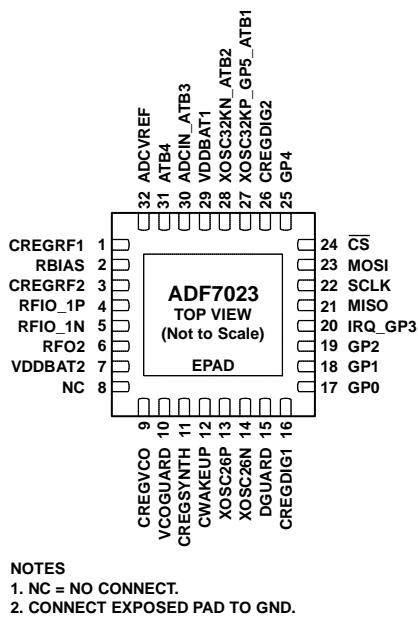

## 引脚配置和功能描述

图4. 引脚配置

表9. 引脚功能描述

| 引脚编号 | 引脚名称      | 功能                                                         |

|------|-----------|------------------------------------------------------------|

| 1    | CREGRF1   | RF的调节器电压。在此引脚和接地之间应放置一个220 nF电容以稳定调节器并抑制噪声。                |

| 2    | RBIAS     | 外部偏置电阻。应使用2%容差的36 kΩ电阻。                                    |

| 3    | CREGRF2   | RF的调节器电压。在此引脚和接地之间应放置一个220 nF电容以稳定调节器并抑制噪声。                |

| 4    | RFIO_1P   | 接收模式下为LNA正输入。发射模式、差分PA下为PA正输出。                             |

| 5    | RFIO_1N   | 接收模式下为LNA负输入。发射模式、差分PA下为PA负输出。                             |

| 6    | RFO2      | 单端PA输出。                                                    |

| 7    | VDBBAT2   | 电源引脚2。至地层的去耦电容应尽可能靠近此引脚。                                   |

| 8    | NC        | 不连接。                                                       |

| 9    | CREGVCO   | VCO的调节器电压。在此引脚和接地之间应放置一个220 nF电容以稳定调节器并抑制噪声。               |

| 10   | VCOGUARD  | VCO的防护/屏蔽。此引脚应连接到引脚9。                                      |

| 11   | CREGSYNTH | 频率合成器的调节器电压。在此引脚和接地之间应放置一个220 nF电容以稳定调节器抑制噪声。              |

| 12   | CWAKEUP   | 唤醒控制的外部电容。应在此引脚与接地之间放置一个150 nF电容。                          |

| 13   | XOSC26P   | 应在此引脚与XOSC26N之间连接26 MHz参考晶振。如果外部参考连接到XOSC26N，此引脚应保持开路。     |

| 14   | XOSC26N   | 应在此引脚与XOSC26P之间连接26 MHz参考晶振。或者，也可以将一个外部26 MHz参考信号交流耦合到此引脚。 |

| 15   | DGUARD    | 数字电路的内部防护/屏蔽。将此引脚连接到引脚16 CREGDIG1。                         |

| 16   | CREGDIG1  | 芯片数字部分的调节器电压。在此引脚和接地之间应放置一个220 nF电容以稳定调节器并抑制噪声。            |

| 17   | GP0       | 数字GPIO引脚0。                                                 |

| 18   | GP1       | 数字GPIO引脚1。                                                 |

| 19   | GP2       | 数字GPIO引脚2。                                                 |

| 20   | IRQ_GP3   | 中断请求，数字GPIO测试引脚3。                                          |

| 21   | MISO      | 串行端口主机输入/从机输出。                                             |

| 引脚编号 | 引脚名称              | 功能                                                                        |

|------|-------------------|---------------------------------------------------------------------------|

| 22   | SCLK              | 串行端口时钟。                                                                   |

| 23   | MOSI              | 串行端口主机输出/从机输入。                                                            |

| 24   | $\overline{CS}$   | 片选(低电平有效)。建议将一个100 k $\Omega$ 上拉电阻接到V <sub>DD</sub> ，以防主机处理器无意中唤醒ADF7023。 |

| 25   | GP4               | 数字GPIO测试引脚4。                                                              |

| 26   | CREGDIG2          | 芯片数字部分的调节器电压。在此引脚和接地之间应放置一个220 nF电容以稳定调节器并抑制噪声。                           |

| 27   | XOSC32KP_GP5_ATB1 | 数字GPIO测试引脚5。可以在此引脚与XOSC32KN_ATB2之间连接32 kHz时钟晶振。<br>模拟测试引脚1。               |

| 28   | XOSC32KN_ATB2     | 可以在此引脚与XOSC32KP_GP5_ATB1之间连接32 kHz时钟晶振。模拟测试引脚2。                           |

| 29   | VDBBAT1           | 数字电源引脚1。至地层的去耦电容应尽可能靠近此引脚。                                                |

| 30   | ADCIN_ATB3        | 模数转换器输入。可以配置为外部PA使能信号。模拟测试引脚3。                                            |

| 31   | ATB4              | 模拟测试引脚4。可以配置为外部LNA使能信号。                                                   |

| 32   | ADCVREF           | ADC基准电压输出。在此引脚和接地之间应放置一个220 nF电容以充分抑制噪声。                                  |

| EPAD | GND               | 裸露的封装焊盘。连接到GND。                                                           |

## 典型性能参数

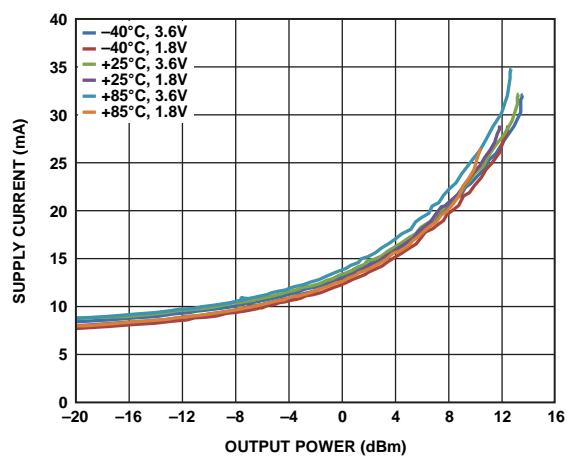

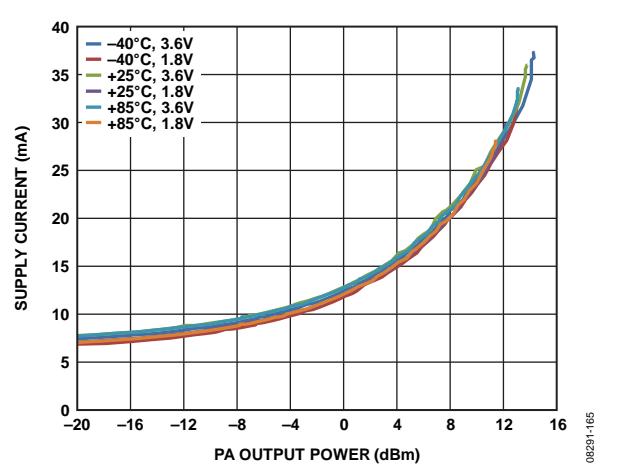

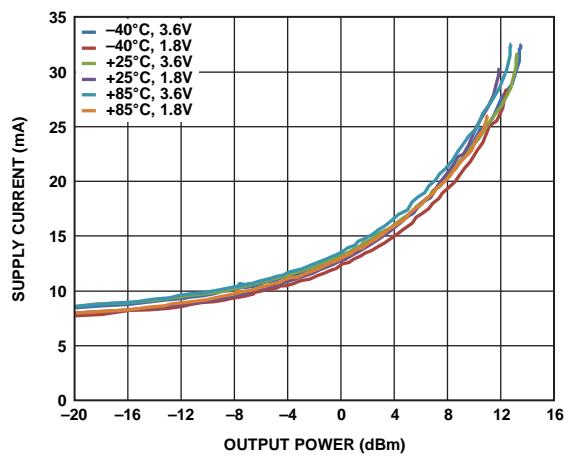

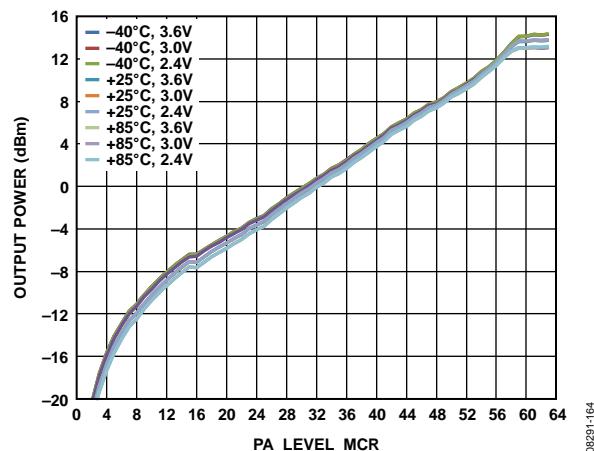

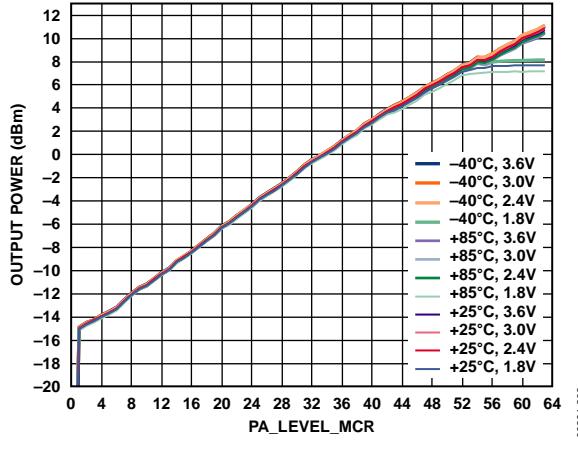

图11. 差分PA (433 MHz): 输出功率与PA\_LEVEL\_MCR设置、温度和 $V_{DD}$ 的关系(建议最小 $V_{DD} = 2.2$  V, 显示1.8 V操作是为了说明其鲁棒性)

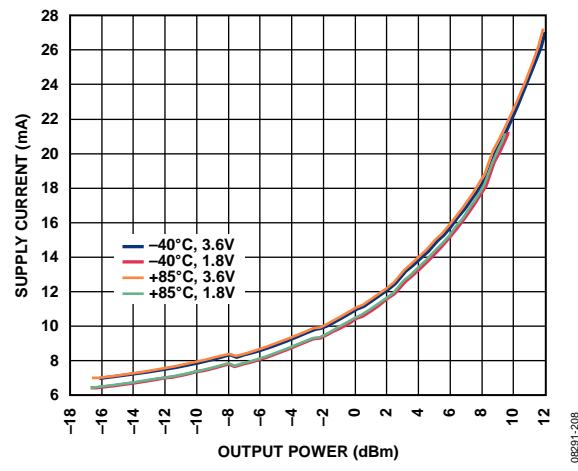

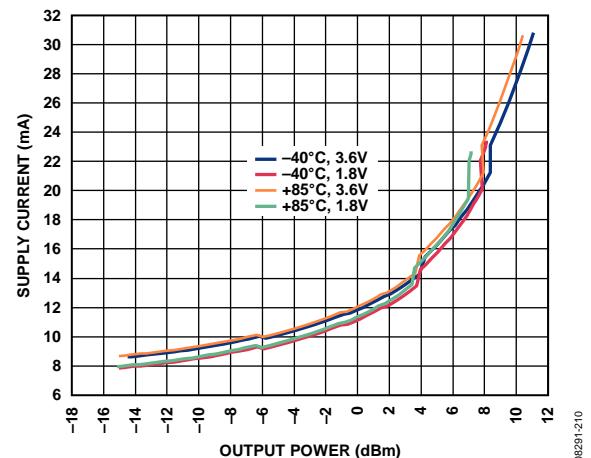

图12. 差分PA (433 MHz): 电源电流与输出功率、温度和 $V_{DD}$ 的关系(建议最小 $V_{DD} = 2.2$  V, 显示1.8 V操作是为了说明其鲁棒性)

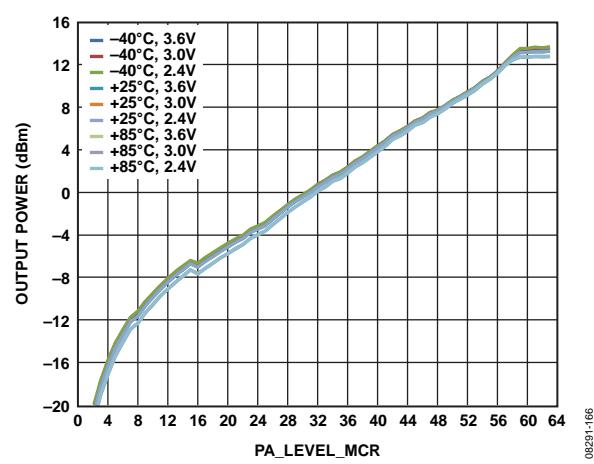

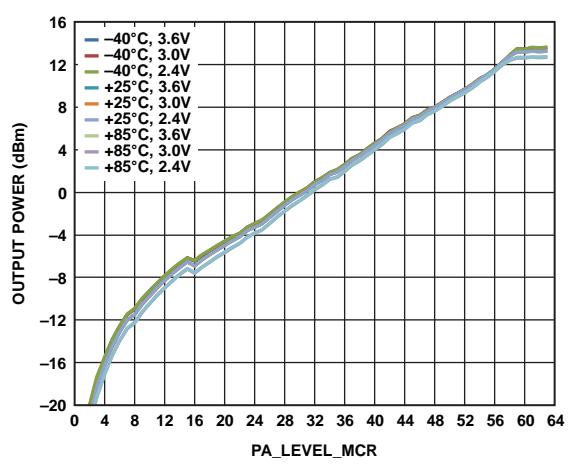

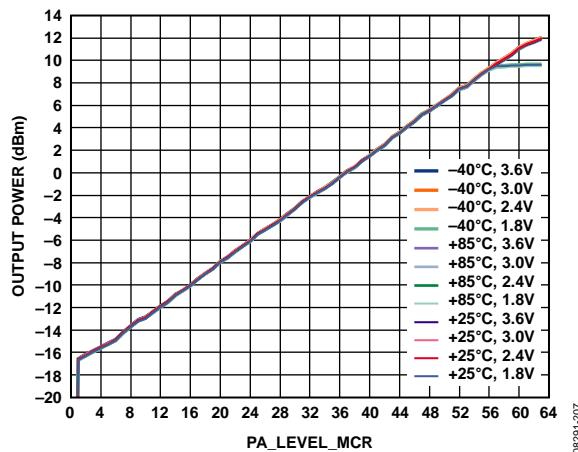

图13. 差分PA (915 MHz): 输出功率与PA\_LEVEL\_MCR设置、温度和 $V_{DD}$ 的关系(建议最小 $V_{DD} = 2.2$  V, 显示1.8 V操作是为了说明其鲁棒性)

图14. 差分PA (915 MHz): 电源电流与输出功率、温度和 $V_{DD}$ 的关系(建议最小 $V_{DD} = 2.2$  V, 显示1.8 V操作是为了说明其鲁棒性)

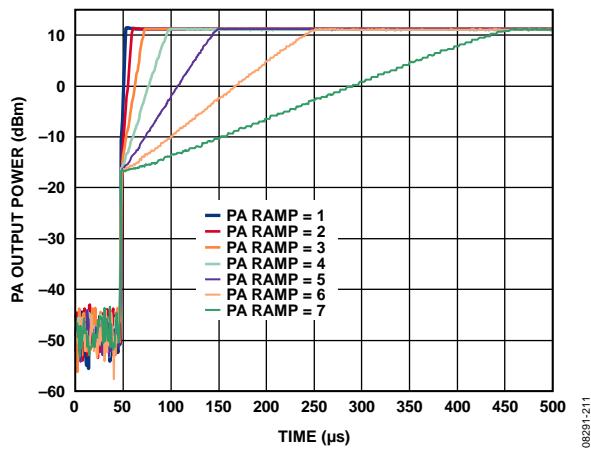

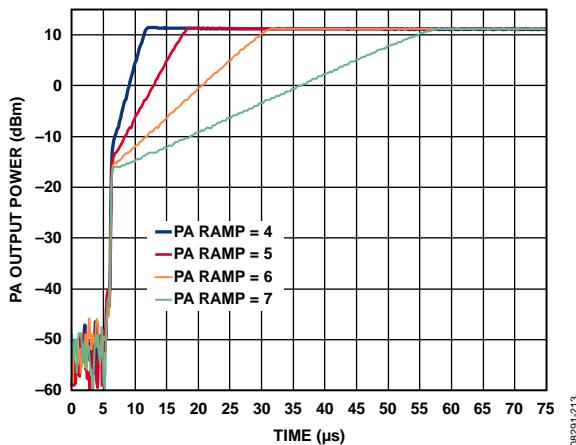

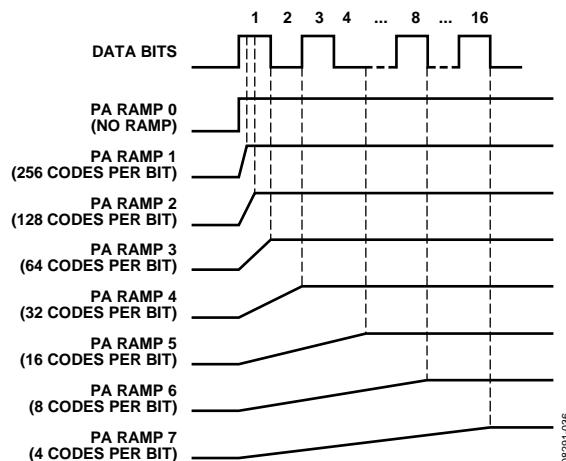

图15. 每个PA\_RAMP设置的PA斜升图:

数据速率=38.4 kbps、差分PA

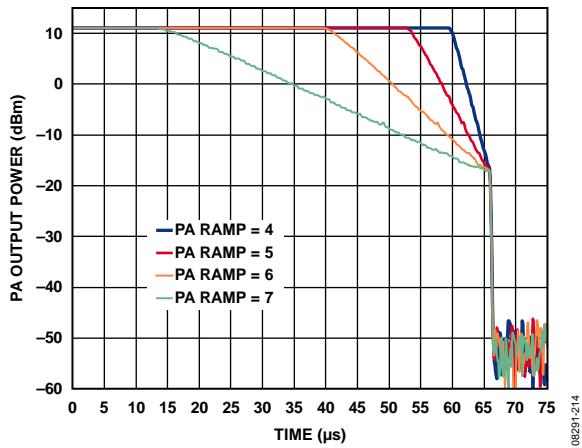

图16. 每个PA\_RAMP设置的PA斜降图:

数据速率=38.4 kbps、差分PA

图17. 每个PA\_RAMP设置的PA斜升图：

数据速率 = 300 kbps、差分PA

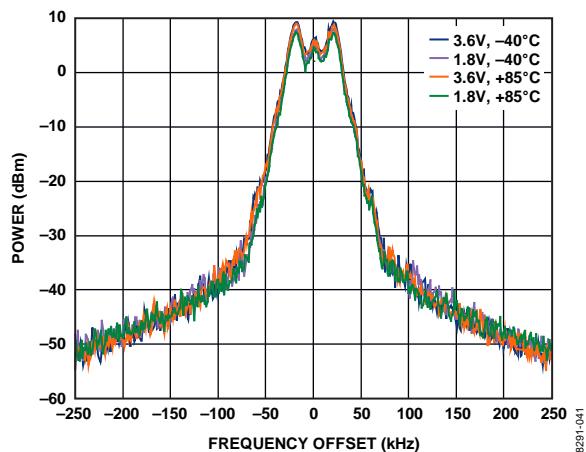

图20. 发射频谱：868 MHz、GFSK、数据速率 = 38.4 kbps，

频率偏差 = 20 kHz(建议最小 $V_{DD}$  = 2.2 V，

显示1.8 V操作是为了说明其鲁棒性)

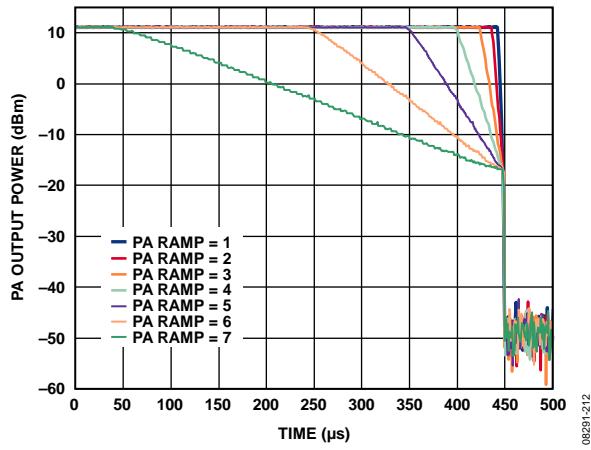

图18. 每个PA\_RAMP设置的PA斜降图：

数据速率 = 300 kbps、差分PA

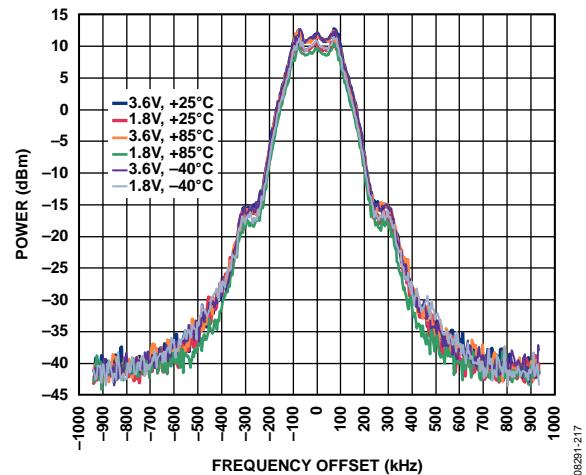

图21. 发射频谱：928 MHz、GFSK、数据速率 = 300 kbps，

频率偏差 = 75 kHz(建议最小 $V_{DD}$  = 2.2 V，

显示1.8 V操作是为了说明其鲁棒性)

图19. 发射频谱：868 MHz、FSK、数据速率 = 38.4 kbps，

频率偏差 = 20 kHz(建议最小 $V_{DD}$  = 2.2 V，

显示1.8 V操作是为了说明其鲁棒性)

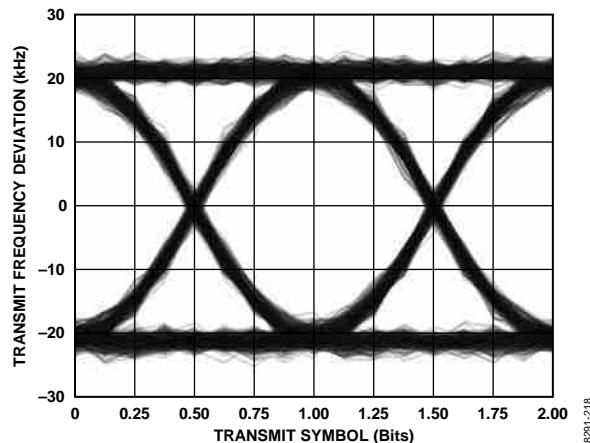

图22. 发射眼图：868 MHz、GFSK，

数据速率 = 38.4 kbps、频率偏差 = 21 kHz

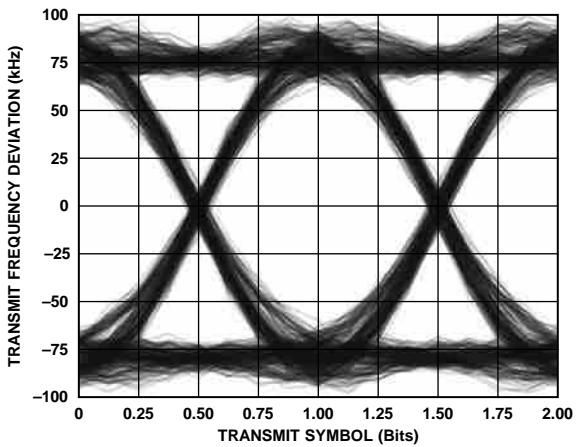

图23. 发射眼图: 868 MHz, GFSK、

数据速率 = 300 kbps、频率偏差 = 75 kHz

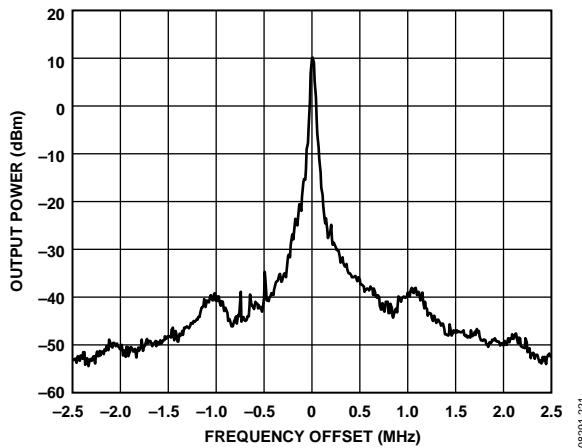

图24. OOK发射频谱: 100次扫描的最大保持、

单端PA、868.95 MHz、数据速率 = 16.4 kbps

(32.8 kcps曼彻斯特编码)、PA\_RAMP = 1

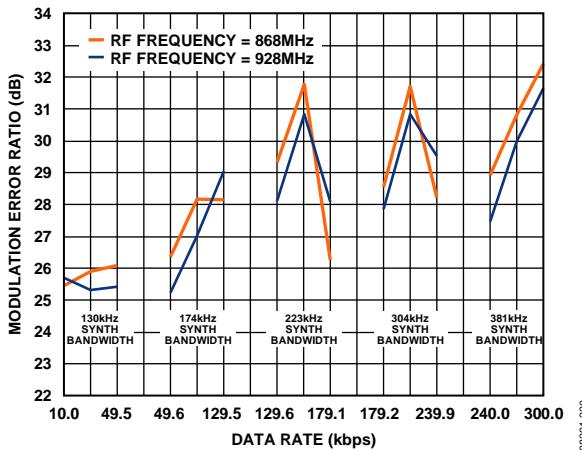

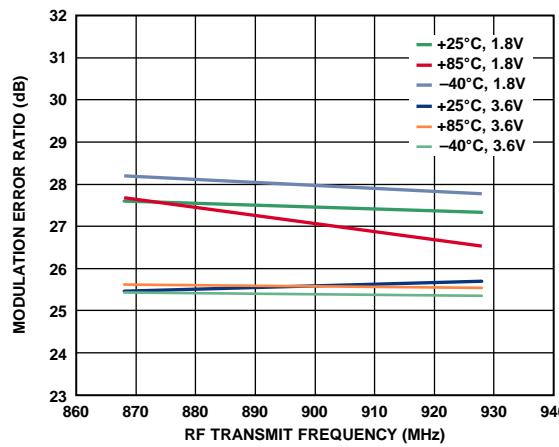

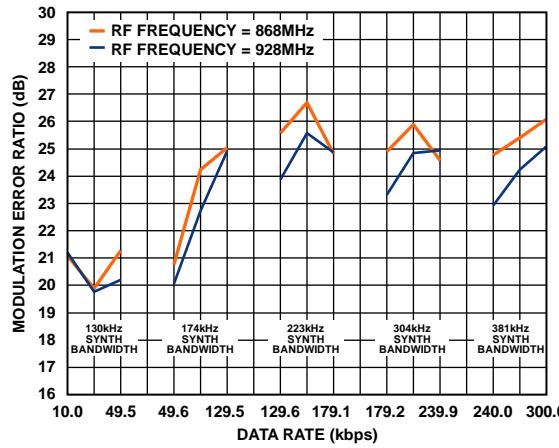

图25. 调制误差比(MER)与数据速率、

频率合成器环路带宽和RF频率的关系, 调制指数 = 1

图26. 调制误差比(MER)与RF频率、温度和V<sub>DD</sub>的关系,

调制指数 = 1, 数据速率 = 10 kbps

(建议最小V<sub>DD</sub> = 2.2 V, 显示1.8 V操作是为了说明其鲁棒性)

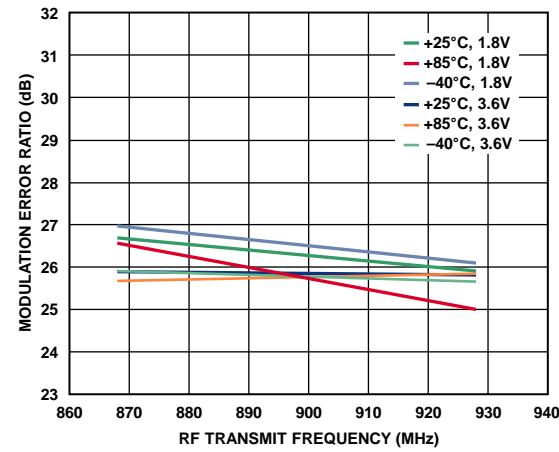

图27. 调制误差比(MER)与数据速率、

频率合成器环路带宽和RF频率的关系, 调制指数 = 0.5

图28. 调制误差比(MER)与RF频率、温度和V<sub>DD</sub>的关系,

调制指数 = 0.5, 数据速率 = 10 kbps

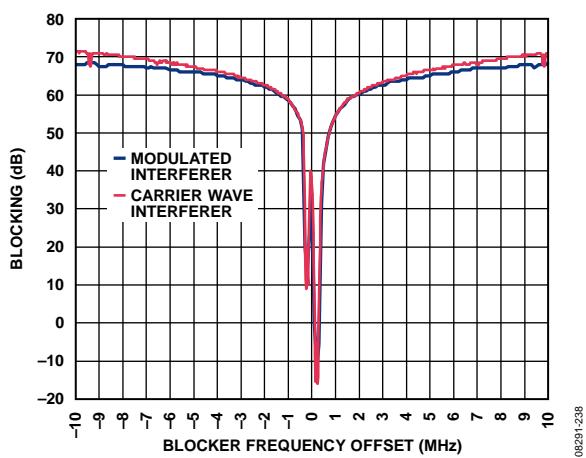

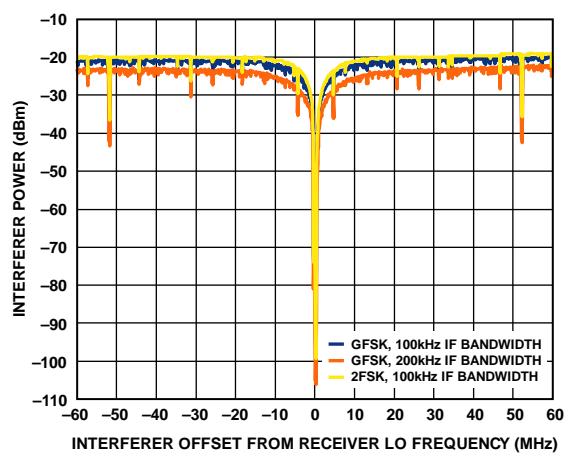

图35. 接收机宽带阻塞: 433 MHz, 数据速率 = 38.4 kbps

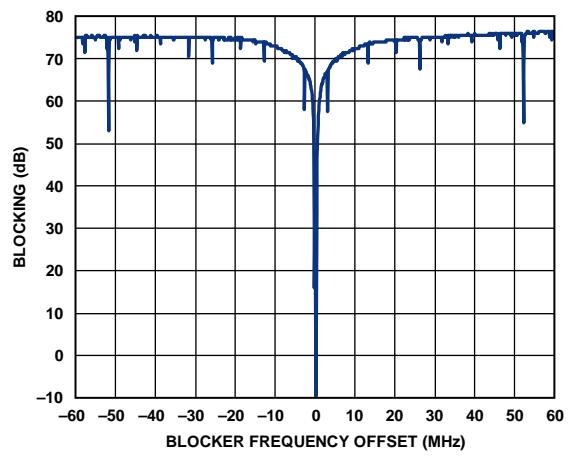

图38. 接收机宽带阻塞至±60 MHz: 868 MHz, 数据速率 = 38.4 kbps, 载波干扰源

图36. 接收机宽带阻塞: 433 MHz, 数据速率 = 100 kbps

图39. 接收机宽带阻塞: 868 MHz, 数据速率 = 100 kbps

图37. 接收机宽带阻塞: 433 MHz, 数据速率 = 300 kbps

图40. 接收机宽带阻塞: 868 MHz, 数据速率 = 300 kbps

# ADF7023

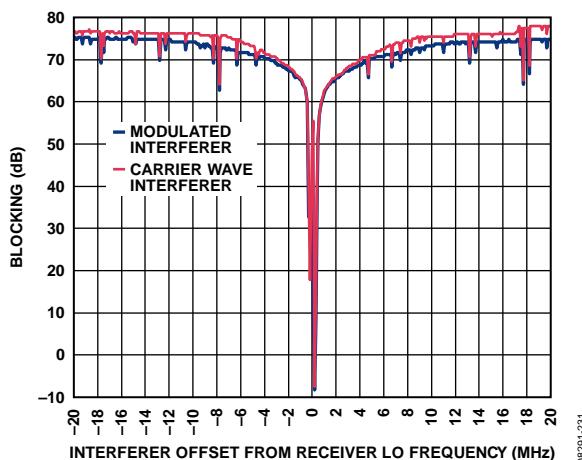

图41. 接收机宽带阻塞: 915 MHz、数据速率 = 38.4 kbps

图42. 接收机宽带阻塞: 915 MHz、数据速率 = 100 kbps

图43. 接收机宽带阻塞: 915 MHz、数据速率 = 300 kbps

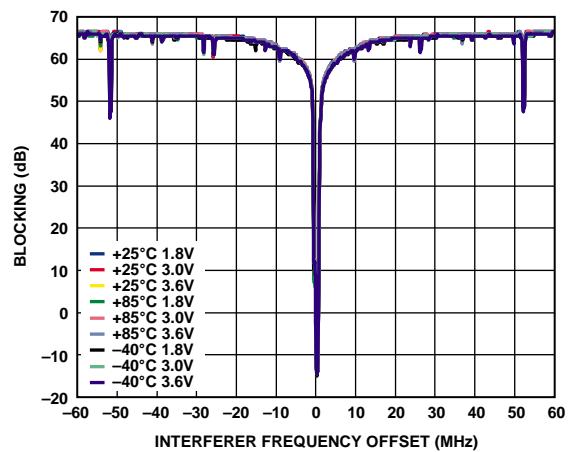

图44. 接收机宽带阻塞与  $V_{DD}$  和温度的关系:

915 MHz、数据速率 = 300 kbps

图45. 接收机宽带阻塞: 868 MHz、数据速率 = 38.4 kbps,

根据ETSI EN 300 220进行测量

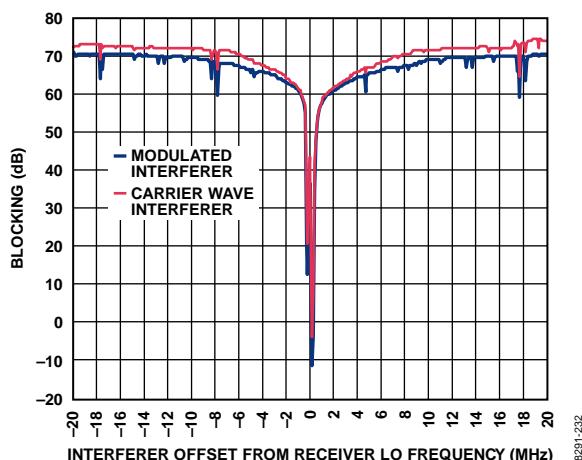

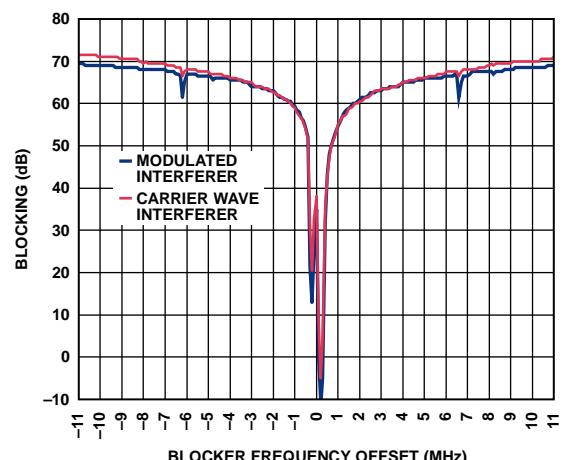

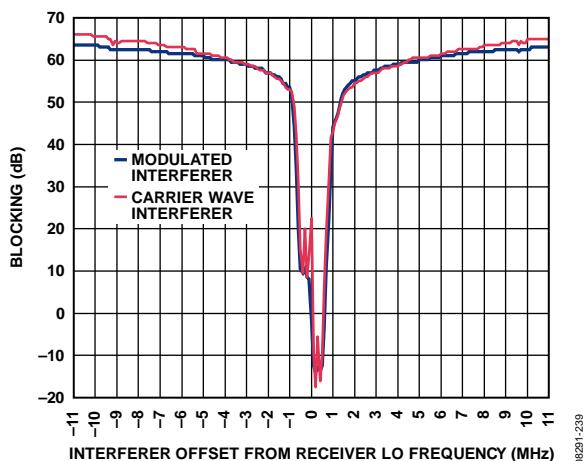

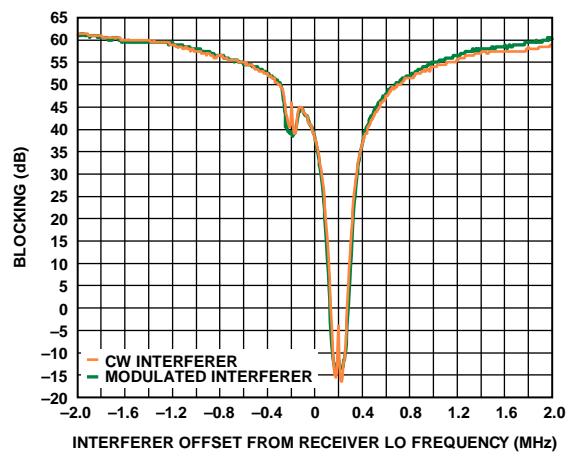

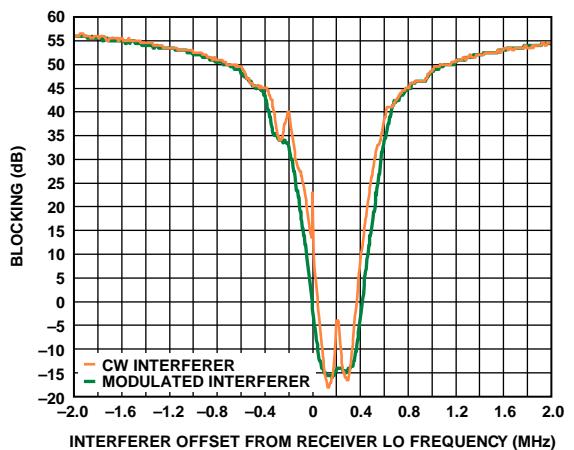

图46. 接收机带内阻塞: 915 MHz、数据速率 = 50 kbps,

IF滤波器带宽 = 100 kHz、镜像校准

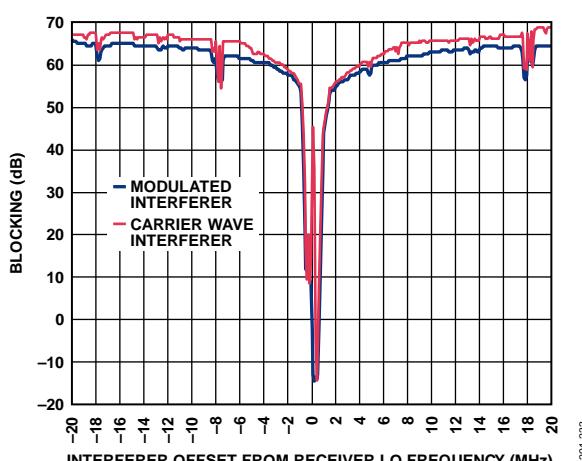

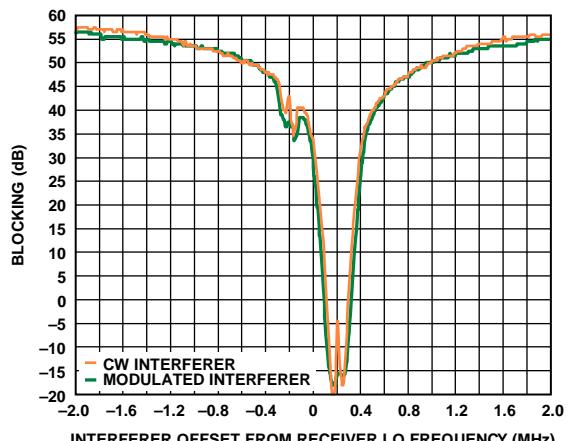

图47. 接收机带内阻塞: 915 MHz, 数据速率 = 100 kbps, IF滤波器带宽 = 100 kHz、镜像校准

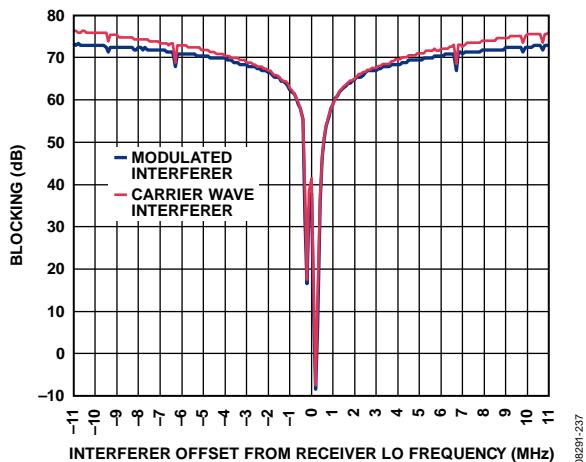

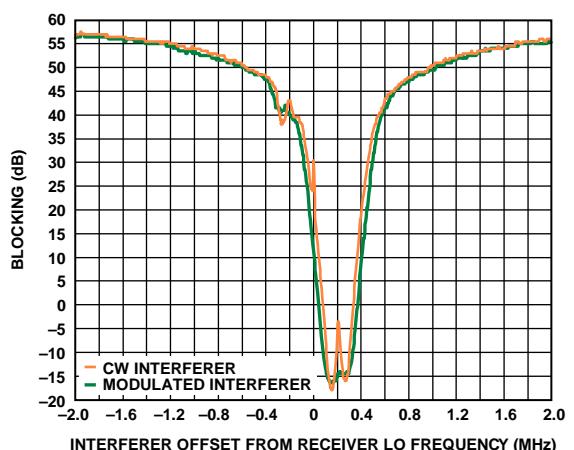

图50. 接收机带内阻塞: 915 MHz、数据速率 = 300 kbps, IF滤波器带宽 = 300 kHz、镜像校准

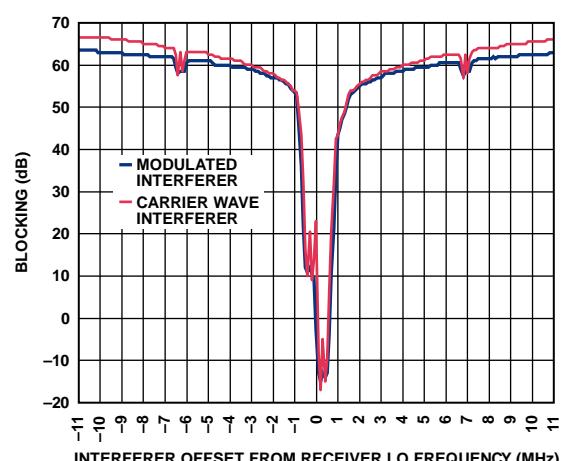

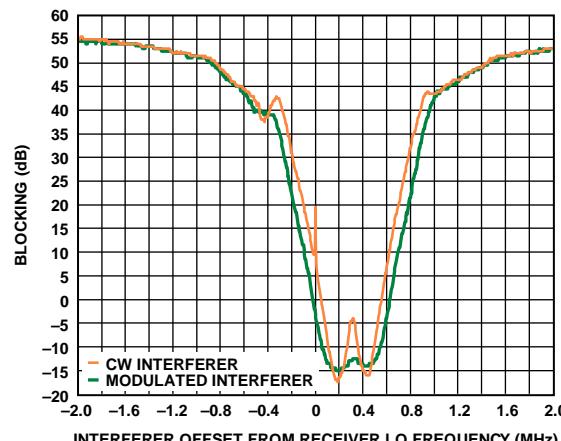

图48. 接收机带内阻塞: 915 MHz, 数据速率 = 150 kbps, IF滤波器带宽 = 150 kHz, 镜像校准

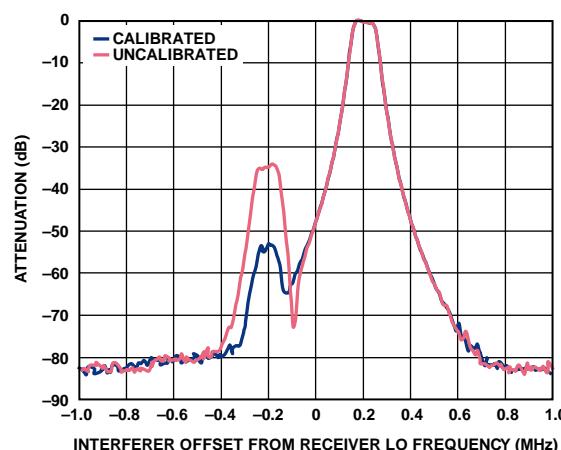

图51. 校准和未校准镜像的镜像抑制: 915 MHz, IF滤波器带宽 = 100 kHz,  $V_{DD} = 3.0$  V, 温度 =  $25^\circ C$

图49. 接收机带内阻塞: 915 MHz, 数据速率 = 200 kbps, IF滤波器带宽 = 200 kHz, 镜像校准

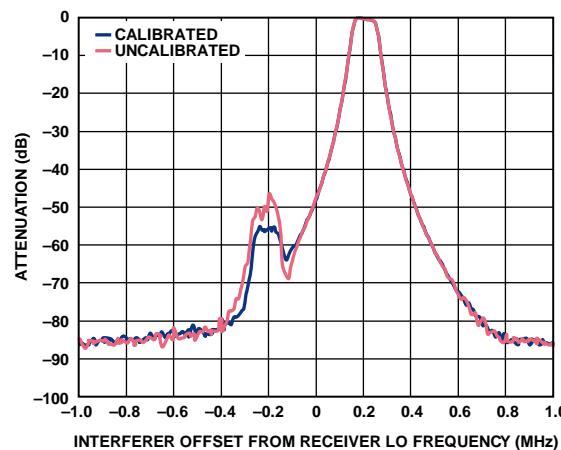

图52. 校准和未校准镜像的镜像抑制: 433 MHz, IF滤波器带宽 = 100 kHz,  $V_{DD} = 3.0$  V, 温度 =  $25^\circ C$

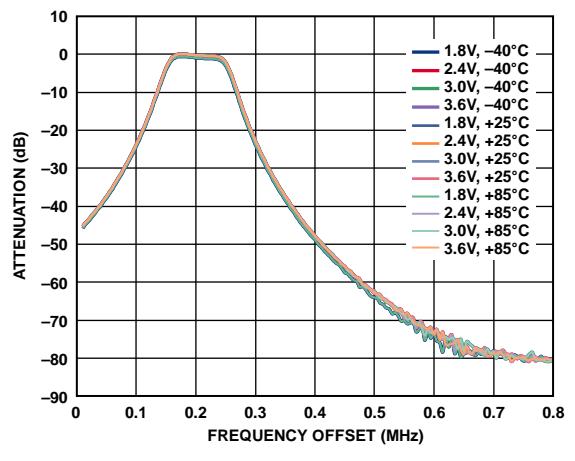

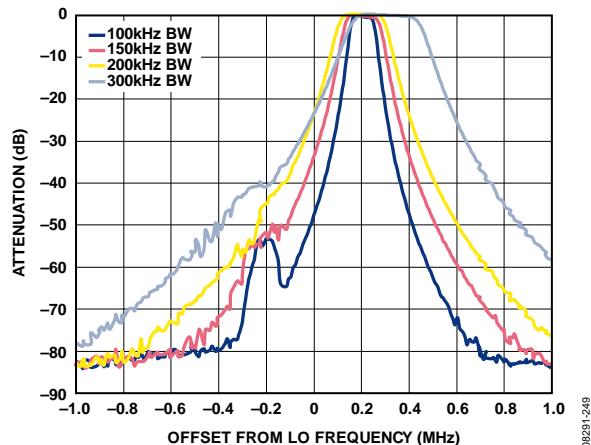

图53. 含校准镜像的IF滤波器响应与IF滤波器带宽的关系:

921 MHz,  $V_{DD} = 3.0$  V, 温度 = 25°C

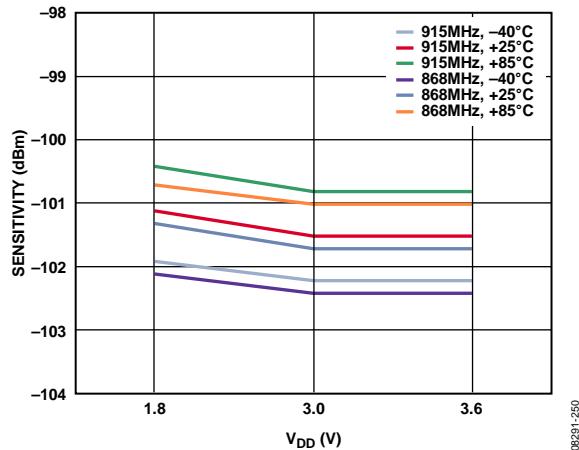

图54. 接收机灵敏度(比特误率为 $1E-3$ )与 $V_{DD}$ 、温度和RF频率的关系: 数据速率 = 300 kbps, GFSK, 频率偏差 = 75 kHz, IF带宽 = 300 kHz

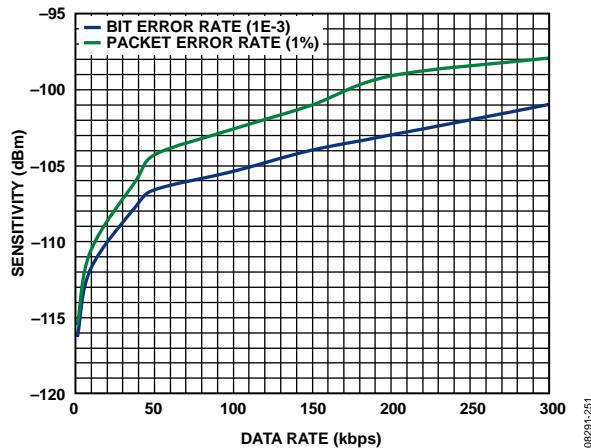

图55. 比特误差率灵敏度(BER =  $1E-3$ )和包误差率灵敏度(PER = 1%)与数据速率的关系:

GFSK,  $V_{DD} = 3.0$  V, 温度 = 25°C

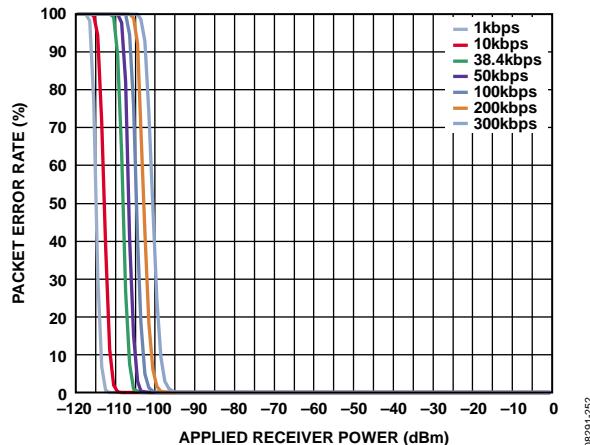

图56. 包误差率与RF输入功率和数据速率的关系:

FSK/GFSK, 928 MHz, 前同步码长度 = 64位,  $V_{DD} = 3.0$  V, 温度 = 25°C

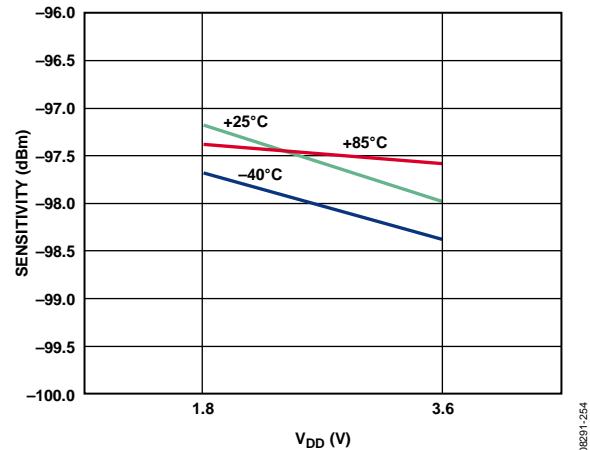

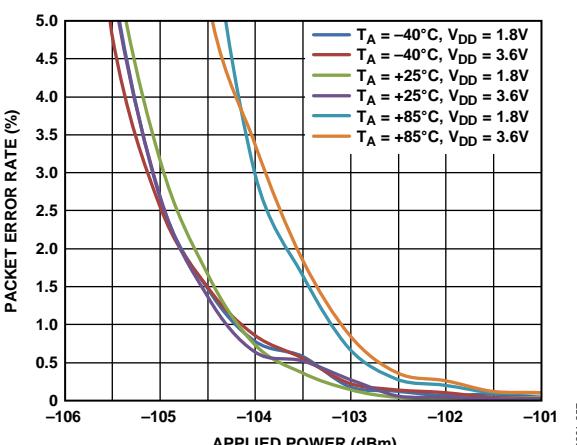

图57. 接收机灵敏度(包误差率为1%)与 $V_{DD}$ 、温度和RF频率的关系:

数据速率 = 300 kbps, GFSK, 频率偏差 = 75 kHz, IF带宽 = 300 kHz

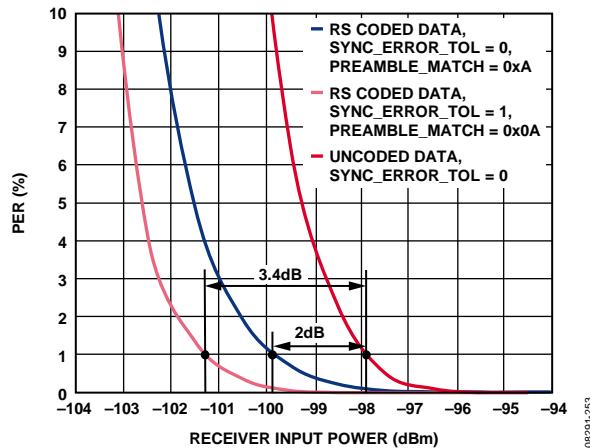

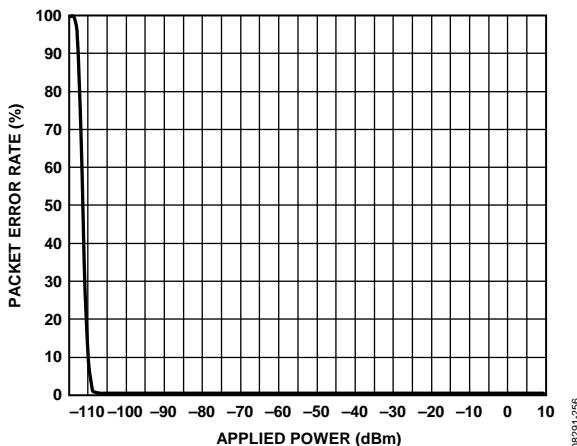

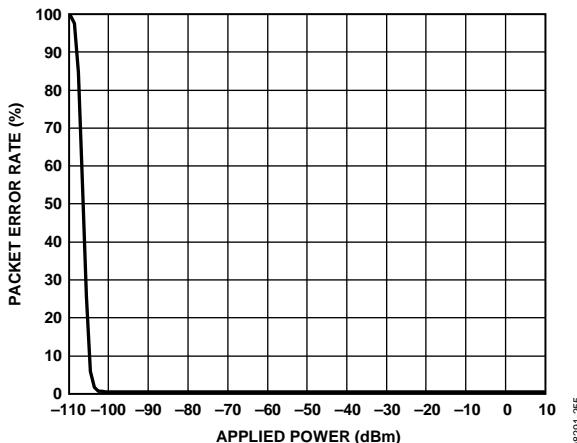

图58. 采用Reed Solomon (RS)编码时的接收机PER; RF频率 = 915 MHz, GFSK, 数据速率 = 300 kbps, 频率偏差 = 75 kHz, 包长度 = 28字节(未编码); Reed Solomon配置:  $n = 38$ ,  $k = 28$ ,  $t = 5$

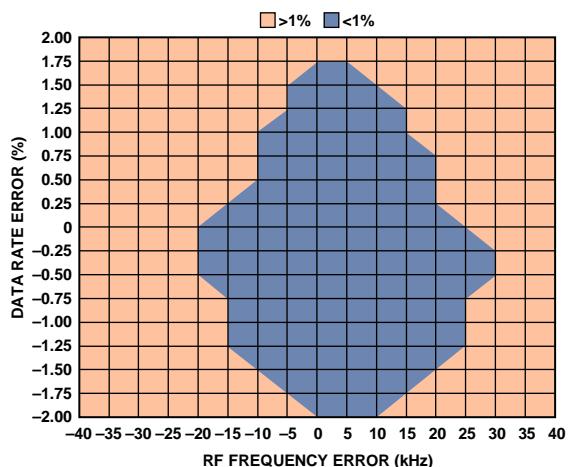

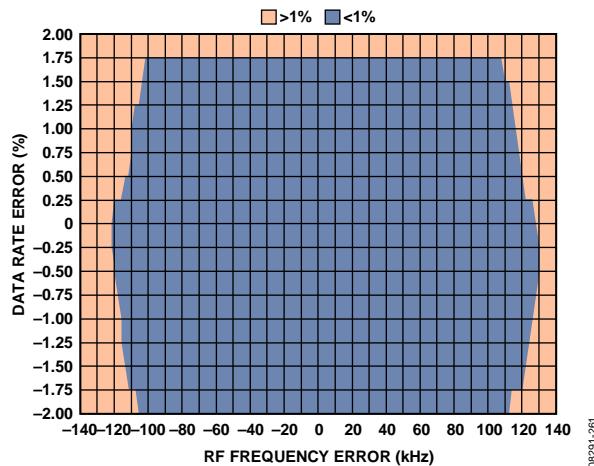

图65. AFC开启: 包误差率与RF频率误差和数据速率误差的关系,

数据速率=300 kbps, 频率偏差=75 kHz,

GFSK, AGC\_LOCK\_MODE = 前同步码后锁定

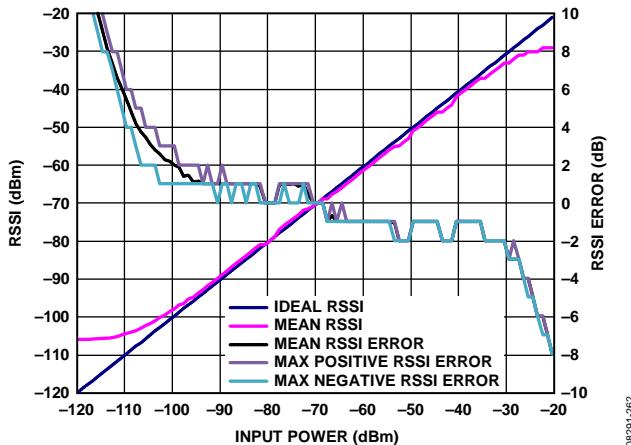

图66. RSSI(通过CMD\_GET\_RSSI)与RF输入功率的关系:

868 MHz, GFSK, 数据速率 = 38.4 kbps, 频率偏差 = 20 kHz,

IF带宽 = 100 kHz, 每个输入功率电平进行100次RSSI测量

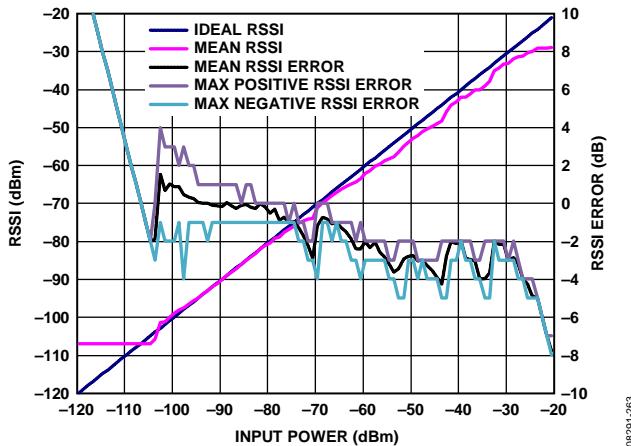

图67. RSSI(通过“自动包结束RSSI测量”)与RF输入功率的关系:

868 MHz, GFSK, 数据速率 = 300 kbps, 频率偏差 = 75 kHz,

IF带宽 = 300 kHz, AGC\_CLOCK\_DIVIDE = 15,

每个输入功率电平进行100次RSSI测量

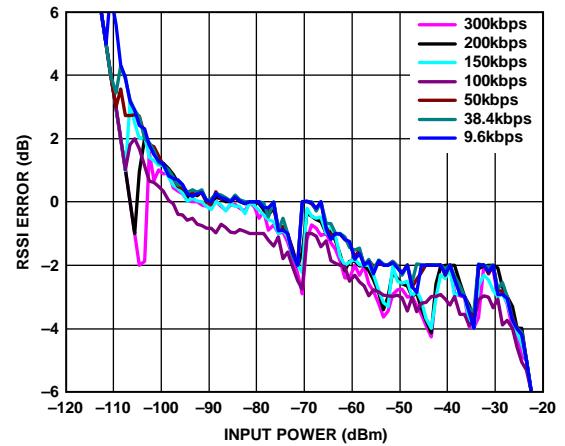

图68. 平均RSSI误差(通过“自动包结束RSSI测量”)与

RF输入功率和数据速率的关系: RF频率 = 868 MHz,

GFSK, 每个输入功率电平进行100次RSSI测量

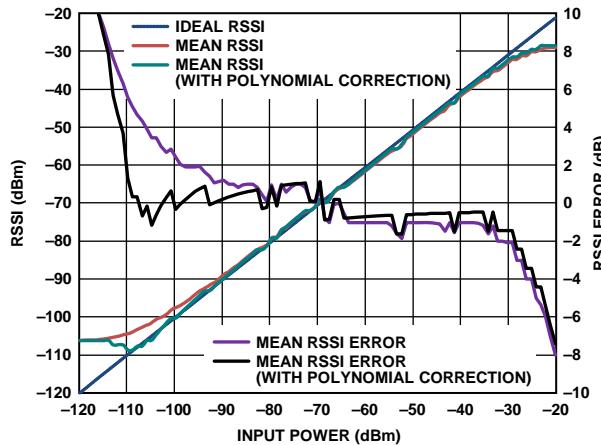

图69. 采用和不采用余弦多项式校正的RSSI

(通过“自动包结束RSSI测量”),

每个输入功率电平进行100次RSSI测量

图70. OOK RSSI和OOK RSSI误差与RF输入功率的关系:

915 MHz, 数据速率 = 19.2 kbps (38.4 kcps),

每个输入功率电平进行200次RSSI测量

图71. OOK RSSI与RF输入功率、 $V_{DD}$ 和温度的关系：

RF频率 = 915 MHz, 数据速率 = 19.2 kbps(38.4 kcps曼彻斯特编码)

图72. 温度传感器的典型精度范围与所施加温度的关系，

校准温度25°C

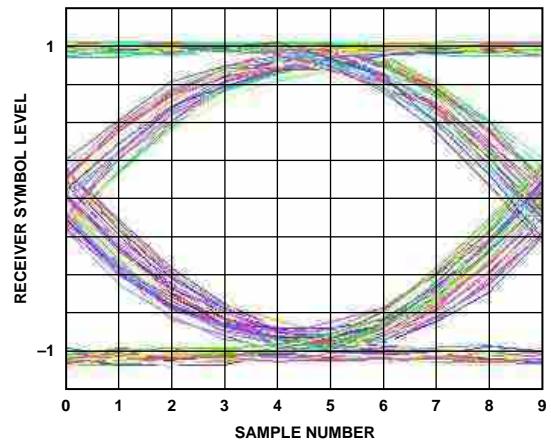

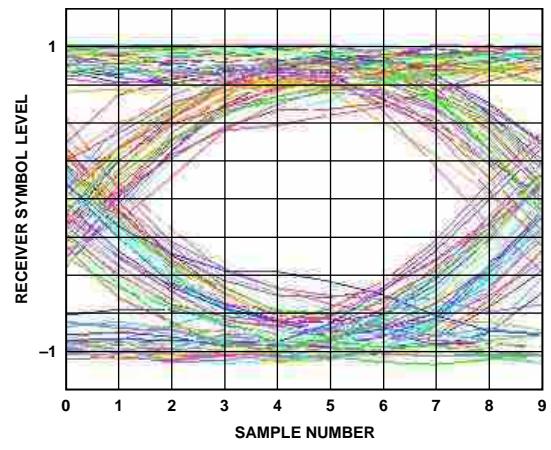

图73. 接收机眼图：采用测试DAC测量, RF频率 = 915 MHz,

RF输入功率 = -80 dBm, 数据速率 = 100 kbps, 频率偏差 = 50 kHz

图74. 接收机眼图：采用测试DAC测量, RF频率 = 915 MHz,

RF输入功率 = -105 dBm, 数据速率 = 100 kbps, 频率偏差 = 50 kHz

## 术语

### ADC

模数转换器

### 自动增益控制

自动增益控制

### 自动频率控制

自动频率控制

### Battmon

电池监控器

### BBRAM

备用电池随机存取存储器

### CBC

密码块链接

### CRC

循环冗余校验

### DR

数据速率

### ECB

电子密码本

### ECC

差错校验码

### 2FSK

两级频移键控

### GFSK

两级高斯频移键控

### GMSK

高斯最小频移键控

### LO

本振

### MAC

媒体访问控制

### MCR

调制解调器配置随机存取存储器

### MER

调制误差率

### MSK

最小频移键控

### 无操作(NOP)

无操作

### OOK

开关键控

### PA

功率放大器

### PFD

鉴频鉴相器

### PHY

物理层

### RCO

RC振荡器

### RISC

精简指令集计算机

### RSSI

接收信号强度指示器

### Rx

接收

### SAR

逐次逼近寄存器

### SWM

智能唤醒模式

### Tx

发射

### VCO

电压控制振荡器

### WUC

唤醒控制器

### XOSC

晶振

## 无线电控制

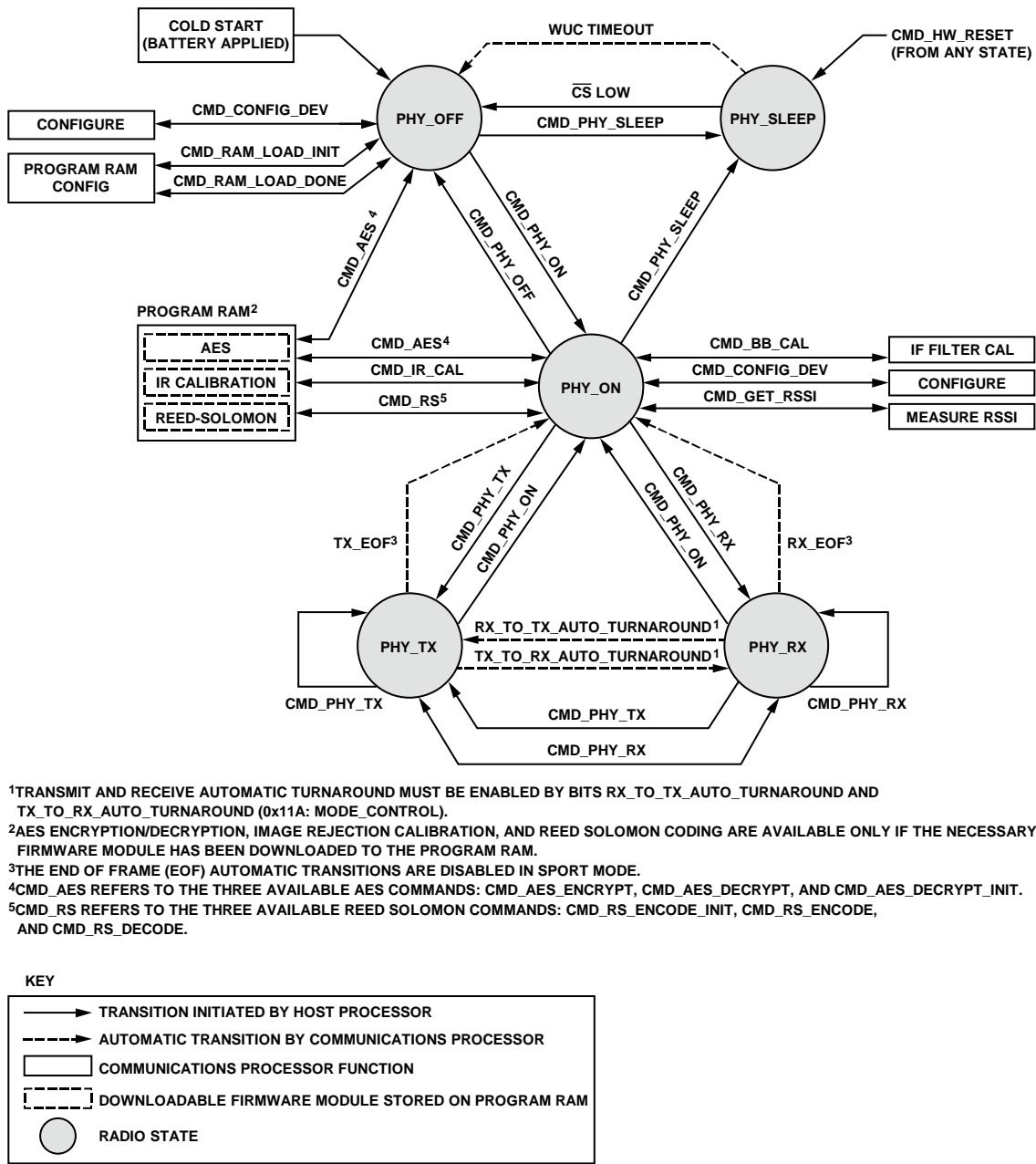

ADF7023具有五种无线电状态，分别称为PHY\_SLEEP、PHY\_OFF、PHY\_ON、PHY\_RX和PHY\_TX。主机处理器可以通过SPI接口发出单字节命令，使ADF7023在不同状态之间跃迁。图75显示了各种命令和状态。通信处理器处理各种无线电电路的序列化和关键时序功能，从而简化无线电操作，减轻主机处理器的负荷。

### 无线电状态

#### PHY\_SLEEP

在该状态下，器件处于低功耗休眠模式。可以从PHY\_OFF或PHY\_ON状态进入该状态，方法是发出CMD\_PHY\_SLEEP命令。要将无线电从该状态唤醒，应将CS引脚拉低，或者使用唤醒控制器(32.768kHz RC或32.768kHz晶体)唤醒。唤醒定时器应在进入PHY\_SLEEP状态之前设置。如果不需要保留BBRAM内容，可以使用深度休眠模式2，以进一步降低PHY\_SLEEP状态下的功耗。要进入深度休眠模式2，需发出CMD\_HW\_RESET命令。PHY\_SLEEP状态的选项详见表10。在PHY\_SLEEP状态下，IRQ\_GP3中断引脚处于逻辑低电平，其它GPx引脚则处于高阻态。

#### PHY\_OFF

在PHY\_OFF状态下，26 MHz晶振、数字调节器和频率合成器调节器上电。所有存储器均可完全访问。退出此状态前，BBRAM寄存器必须有效。

#### PHY\_ON

在PHY\_ON状态下，除晶振、数字调节器和频率合成器调节器上电外，VCO和RF调节器也上电。从PHY\_OFF状态进入此状态时，如果MODE\_CONTROL寄存器(地址0x11A)的BB\_CAL位置1，则会执行基带滤波器校准。器件已准备好工作，可以进入PHY\_TX和PHY\_RX状态。

#### PHY\_TX

在PHY\_TX状态下，频率合成器使能并接受校准。功率放大器使能，器件以CHANNEL\_FREQ[23:0]设置(地址0x109至0x10B)所定义的通道频率发射信号。要进入该状态，需

发出CMD\_PHY\_TX命令。器件自动发送包RAM中存储的发送数据包。发送完毕后，PA禁用，器件自动返回PHY\_ON状态，此时可以产生一个中断(可选项)。

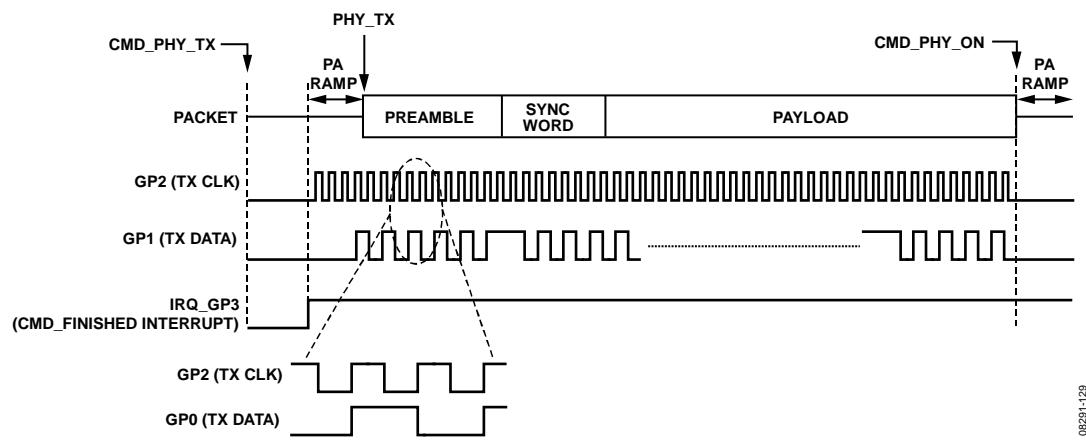

在Sport模式下，器件发送GP2引脚上的数据，如Sport部分所述。在Sport模式下退出PHY\_TX状态时，主机处理器必须发出CMD\_PHY\_ON命令。

#### PHY\_RX

在PHY\_RX状态下，频率合成器使能并执行校准。ADC、RSSI、IF滤波器、混频器和LNA使能。无线电处于接收模式，通道频率由CHANNEL\_FREQ[23:0]设置(地址0x109至0x10B)定义。

接收到有效数据包后，器件返回PHY\_ON状态，此时可以产生一个中断(可选项)。在Sport模式下，器件一直处于PHY\_RX状态，直到发出CMD\_PHY\_ON命令为止。

#### 功耗

每种状态下的典型功耗详见表10。

表10. ADF7023无线电状态的功耗

| 状态                     | 典型功耗         | 条件                                   |

|------------------------|--------------|--------------------------------------|

| PHY_SLEEP<br>(深度休眠模式2) | 0.18 $\mu$ A | 唤醒定时器关闭，不留BBRAM内容，通过发出CMD_HW_RESET进入 |

| PHY_SLEEP<br>(深度休眠模式1) | 0.33 $\mu$ A | 唤醒定时器关闭，保留BBRAM内容                    |

| PHY_SLEEP<br>(RCO模式)   | 0.75 $\mu$ A | 唤醒定时器开启，使用32 kHz RC振荡器，保留BBRAM内容     |

| PHY_SLEEP<br>(XTO模式)   | 1.28 $\mu$ A | 唤醒定时器开启，使用32 kHz XTAL振荡器，保留BBRAM内容   |

| PHY_OFF                | 1.0 mA       |                                      |

| PHY_ON                 | 1.0 mA       |                                      |

| PHY_TX                 | 24.1 mA      | 10 dBm, 单端PA, 868 MHz                |

| PHY_RX                 | 12.8 mA      |                                      |

图75. 无线电状态图

## 初始化

### 加电后的初始化

通过VDDBAT1/VDDBAT2引脚对ADF7023施加电源后，它记录一个上电复位事件(POR)，并跃迁到PHY\_OFF状态。BBRAM存储器为未知值，包RAM存储器清零至0x00，MCR存储器复位为默认值。主机处理器应通过下列步骤完成初始化序列：

1. 将SPI的CS引脚拉低，等待MISO输出变为高电平。

2. 轮询状态字，等待CMD\_READY位变为高电平。

3. 写入所有64个BBRAM寄存器以配置器件。

4. 发出CMD\_CONFIG\_DEV命令，以便利用BBRAM值更新无线电设置。

ADF7023现已配置为PHY\_OFF状态。

### 发出CMD\_HW\_RESET命令后的初始化

CMD\_HW\_RESET命令会使所有硬件完全掉电，器件进入PHY\_SLEEP状态。要完成硬件复位，主机处理器应完成下列步骤：

1. 等待1 ms。

2. 将SPI的CS引脚拉低，等待MISO输出变为高电平。ADF7023记录一个POR并进入PHY\_OFF状态。

3. 轮询状态字，等待CMD\_READY位变为高电平。

4. 写入所有64个BBRAM寄存器以配置器件。

5. 发出CMD\_CONFIG\_DEV命令，以便利用BBRAM值更新无线电设置。

ADF7023现已配置为PHY\_OFF状态。

### 从PHY\_SLEEP跃迁时的初始化(CS拉低后)

主机处理器可以随时拉低CS，使ADF7023从PHY\_SLEEP状态唤醒。该事件不会作为POR事件记录下来，因为BBRAM内容有效。主机处理器需要完成下列步骤：

1. 将SPI的CS线拉低，等待MISO输出变为高电平。ADF7023进入PHY\_OFF状态。

2. 轮询状态字，等待CMD\_READY位变为高电平。

3. 发出CMD\_CONFIG\_DEV命令，以便利用BBRAM值更新无线电设置。

ADF7023现在配置就绪，可以跃迁到PHY\_ON状态。

### WUC超时后的初始化

ADF7023可以利用唤醒控制器从PHY\_SLEEP状态自主唤醒。在智能唤醒模式(SWM)下，如果ADF7023在WUC超时后唤醒，它将根据BBRAM中的智能唤醒模式配置执行SWM程序(参见“低功耗模式”部分)。当SWM禁用且固件定时器禁用时，如果ADF7023在WUC超时后唤醒，它将处于PHY\_OFF状态，并且主机处理器需要执行下列步骤：

1. 轮询状态字，等待CMD\_READY位变为高电平。

2. 发出CMD\_CONFIG\_DEV命令，以便利用BBRAM值更新无线电设置。

ADF7023现已配置为PHY\_OFF状态。

## 命令

本节详细介绍无线电控制器支持的命令。这些命令用于启动无线电状态跃迁或者执行图75中所示的任务。

### CMD\_PHY\_OFF (0xB0)

此命令使ADF7023跃迁到PHY\_OFF状态。可以在PHY\_ON状态下发出此命令。它会关断RF和VCO调节器。

### CMD\_PHY\_ON (0xB1)

此命令使ADF7023跃迁到PHY\_ON状态。

在PHY\_OFF状态下发出此命令时，RF和VCO调节器上电；如果MODE\_CONTROL寄存器(地址0x11A)的BB\_CAL位置1，则还会执行IF滤波器校准。

如果从PHY\_TX状态发出此命令，则主机处理器执行下列步骤：

1. 使PA斜降。

2. 将外部PA信号拉低(如已使能)。

3. 关闭数字发送时钟。

4. 关断频率合成器。

5. 设置FW\_STATE = PHY\_ON。

如果从PHY\_RX状态发出此命令，则通信处理器执行下列步骤：

1. 将测得的RSSI复制到RSSI\_READBACK寄存器。

2. 将外部LNA信号拉低(如已使能)。

3. 关闭数字接收时钟。

4. 关断频率合成器和接收机电路(ADC、RSSI、IF滤波器、混频器和LNA)。

5. 设置FW\_STATE = PHY\_ON。

## CMD\_PHY\_SLEEP (0xBA)

此命令可使ADF7023跃迁到功耗极低的PHY\_SLEEP状态，此时WUC运行(如已使能)，BBRAM内容会被保留。可以从PHY\_OFF或PHY\_ON状态发出此命令。

## CMD\_PHY\_RX (0xB2)

可以在PHY\_ON、PHY\_RX或PHY\_TX状态下发出此命令。如果在PHY\_ON状态下发出此命令，则通信处理器执行下列步骤：

1. 使频率合成器上电。

2. 使接收机电路(ADC、RSSI、IF滤波器、混频器和LNA)上电。

3. 根据BBRAM中的CHANNEL\_FREQ[23:0]值设置RF通道。

4. 设置频率合成器带宽。

5. 执行VCO校准。

6. 等待频率合成器建立。

7. 使能数字接收机模块。

8. 将外部LNA使能信号拉高(如已使能)。

9. 设置FW\_STATE = PHY\_RX。

如果在PHY\_RX状态下发出此命令，则通信处理器执行下列步骤：

1. 将外部LNA信号拉低(如已使能)。

2. 解除AFC和AGC锁定。

3. 关闭接收模块。

4. 根据BBRAM中的CHANNEL\_FREQ[23:0]值设置RF通道。

5. 设置频率合成器带宽。

6. 执行VCO校准。

7. 等待频率合成器建立。

8. 使能数字接收机模块。

9. 将外部LNA使能信号拉高(如已使能)。

10. 设置FW\_STATE = PHY\_RX。

如果在PHY\_TX状态下发出此命令，则通信处理器执行下列步骤：

1. 使PA斜降。

2. 将外部PA信号拉低(如已使能)。

3. 关闭数字发送模块。

4. 使接收机电路(ADC、RSSI、IF滤波器、混频器和LNA)上电。

5. 根据BBRAM中的CHANNEL\_FREQ[23:0]值设置RF通道。

6. 设置频率合成器带宽。

7. 执行VCO校准。

8. 等待频率合成器建立。

9. 使能数字接收机模块。

10. 将外部LNA使能信号拉高(如已使能)。

11. 设置FW\_STATE = PHY\_RX。

## CMD\_PHY\_TX (0xB5)

可以在PHY\_ON、PHY\_TX或PHY\_RX状态下发出此命令。如果在PHY\_ON状态下发出此命令，则通信处理器执行下列步骤：

1. 使频率合成器上电。

2. 根据BBRAM中的CHANNEL\_FREQ[23:0]值设置RF通道。

3. 设置频率合成器带宽。

4. 执行VCO校准。

5. 等待频率合成器建立。

6. 使能数字发送模块。

7. 将外部PA使能信号拉高(如已使能)。

8. 使PA斜升。

9. 设置FW\_STATE = PHY\_TX。

10. 发送数据。

如果在PHY\_TX状态下发出此命令，则通信处理器执行下列步骤：

1. 使PA斜降。

2. 将外部PA使能信号拉低(如已使能)。

3. 关闭数字发送模块。

4. 根据BBRAM中的CHANNEL\_FREQ[23:0]值设置RF通道。

5. 设置频率合成器带宽。

6. 执行VCO校准。

7. 等待频率合成器建立。

8. 使能数字发送模块。

9. 将外部PA使能信号拉高(如已使能)。

10. 使PA斜升。

11. 设置FW\_STATE = PHY\_TX。

12. 发送数据。

如果在PHY\_RX状态下发出此命令，则通信处理器执行下列步骤：

1. 将外部LNA信号拉低(如已使能)。

2. 解除AFC和AGC锁定。

3. 关闭接收模块。

4. 关断接收机电路(ADC、RSSI、IF滤波器、混频器和LNA)。

5. 根据BBRAM中的CHANNEL\_FREQ[23:0]值设置RF通道。

6. 设置频率合成器带宽。

7. 等待频率合成器建立。

8. 使能数字发送模块。

9. 将外部PA使能信号拉高(如已使能)。

10. 使PA斜升。

11. 设置FW\_STATE = PHY\_TX。

12. 发送数据。

## **CMD\_CONFIG\_DEV (0xBB)**

此命令用于解释BBRAM内容，并根据这些内容配置各无线电参数。可以从PHY\_OFF或PHY\_ON状态发出此命令。唯一不由此命令配置的无线电参数是CHANNEL\_FREQ[23:0]设置，它是在CMD\_PHY\_TX或CMD\_PHY\_RX命令中配置的。

用户应写入BBRAM的全部64个字节，然后发出CMD\_CONFIG\_DEV命令，可以在PHY\_OFF或PHY\_ON状态下发出该命令。

## **CMD\_GET\_RSSI (0xBC)**

此命令可开启接收机，对当前通道执行RSSI测量，并使ADF7023返回PHY\_ON状态。可以从PHY\_ON状态发出此命令。RSSI结果将保存到RSSI\_READBACK寄存器(地址0x312)。此命令只能从PHY\_ON状态发出。

## **CMD\_BB\_CAL (0xBE)**

此命令执行IF滤波器校准。只能在PHY\_ON状态下发出此命令。许多情况下不必使用此命令，因为从PHY\_OFF跃迁到PHY\_ON时，如果MODE\_CONTROL寄存器(地址0x11A)的BB\_CAL = 1，会自动执行IF滤波器校准。

## **CMD\_HW\_RESET (0xC8)**

此命令会使所有硬件完全掉电，器件进入PHY\_SLEEP状态。可以在任何状态下发出此命令，它与通信处理器的状态无关。CMD\_HW\_RESET命令之后的器件初始化过程详见“初始化”部分。

## **CMD\_RAM\_LOAD\_INIT (0xBF)**

此命令使通信处理器准备就绪，能够将软件模块下载到程序RAM。只能在主机处理器写入程序RAM之前发出此命令。

## **CMD\_RAM\_LOAD\_DONE (0xC7)**

只有将软件模块下载到程序RAM之后才需要发出此命令。它告知通信处理器，已有一个软件模块下载到程序RAM。只能在PHY\_OFF状态下发出此命令。它会复位通信处理器和包RAM。

## **CMD\_IR\_CAL (0xBD)**

此命令用于对ADF7023接收机执行全自动镜像抑制校准。

此命令要求已将IR校准固件模块下载到ADF7023程序RAM。固件模块可从ADI公司获得。更多信息参见“可下载的固件模块”部分。

## **CMD\_AES\_ENCRYPT (0xD0)、CMD\_AES\_DECRYPT (0xD2)和CMD\_AES\_DECRYPT\_INIT (0xD1)**

这些命令支持利用128位、192位或256位的密钥对发送和接收数据进行AES 128位块加密和解密。

AES命令要求已将AES固件模块下载到ADF7023程序RAM。AES固件模块可从ADI公司获得。有关AES加密和解密模块的详细信息，参见“可下载的固件模块”部分。

## **CMD\_RS\_ENCODE\_INIT (0xD1)、CMD\_RS\_ENCODE (0xD0)和CMD\_RS\_DECODE (0xD2)**

这些命令用于对发送和接收数据执行Reed Solomon编码和解码，因而能够检测并校正接收包中的错误。

这些命令要求已将Reed Solomon固件模块下载到ADF7023程序RAM。Reed Solomon固件模块可从ADI公司获得。有关此模块的详细信息，参见“可下载的固件模块”部分。

## **自动状态跃迁**

发生某些事件时，通信处理器可以使ADF7023在不同状态之间自动跃迁。图75中的虚线所示为自动跃迁，本节将予以详细说明。

## TX\_EOF

数据包发送完毕时，通信处理器自动使器件从PHY\_TX状态跃迁到PHY\_ON状态。跃迁时，通信处理器执行下列操作：

1. 使PA斜降。

2. 将外部PA信号拉低。

3. 禁用数字发射机模块。

4. 关断频率合成器。

5. 设置FW\_STATE = PHY\_ON。

## RX\_EOF

数据包接收完毕时，通信处理器自动使器件从PHY\_RX状态跃迁到PHY\_ON状态。跃迁时，通信处理器执行下列操作：

1. 将测得的RSSI复制到RSSI\_READBACK寄存器(地址0x312)。

2. 将外部LNA信号拉低。

3. 禁用数字接收机模块。

4. 关断频率合成器和接收机电路(ADC、RSSI、IF滤波器、混频器和LNA)。

5. 设置FW\_STATE = PHY\_ON。

## RX\_TO\_TX\_AUTO\_TURNAROUND

如果MODE\_CONTROL寄存器(地址0x11A)的RX\_TO\_TX\_AUTO\_TURNAROUND位使能，则在有效数据包接收完毕时，器件自动跃迁到PHY\_TX状态，RF通道频率不变。跃迁时，通信处理器执行下列操作：

1. 将外部LNA信号拉低。

2. 解除AGC和AFC锁定(如已使能)。

3. 禁用数字接收机模块。

4. 关断接收机电路(ADC、RSSI、IF滤波器、混频器和LNA)。

5. 设置RF通道频率(与先前的接收通道频率相同)。

6. 设置频率合成器带宽。

7. 执行VCO校准。

8. 等待频率合成器建立。

9. 使能数字发射机模块。

10. 将外部PA信号拉高(如已使能)。

11. 使PA斜升。

12. 设置FW\_STATE = PHY\_TX。

13. 发送数据。

在Sport模式下，禁用RX\_TO\_TX\_AUTO\_TURNAROUND跃迁。

## TX\_TO\_RX\_AUTO\_TURNAROUND

如果MODE\_CONTROL寄存器(地址0x11A)的TX\_TO\_RX\_AUTO\_TURNAROUND位使能，则在数据包发送完毕时，器件自动跃迁到PHY\_RX状态，RF通道频率不变。跃迁时，通信处理器执行下列操作：

1. 使PA斜降。

2. 将外部PA信号拉低。

3. 禁用数字发射机模块。

4. 使接收机电路(ADC、RSSI、IF滤波器、混频器和LNA)上电。

5. 设置RF通道(与先前的发射通道频率相同)。

6. 设置频率合成器带宽。

7. 执行VCO校准。

8. 等待频率合成器建立。

9. 开启AGC和AFC(如已使能)。

10. 使能数字接收机模块。

11. 将外部LNA信号拉高(如已使能)。

12. 设置FW\_STATE = PHY\_RX。

在Sport模式下，禁用TX\_TO\_RX\_AUTO\_TURNAROUND跃迁。

## WUC超时

ADF7023可以利用WUC，在硬件定时器超时时唤醒。器件唤醒后进入PHY\_OFF状态。更多信息参见“WUC模式”部分。

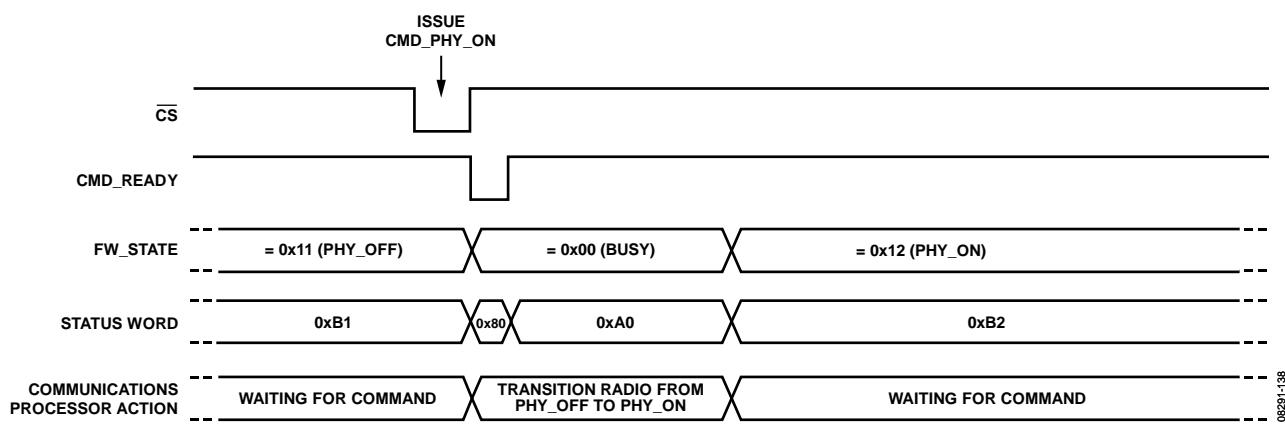

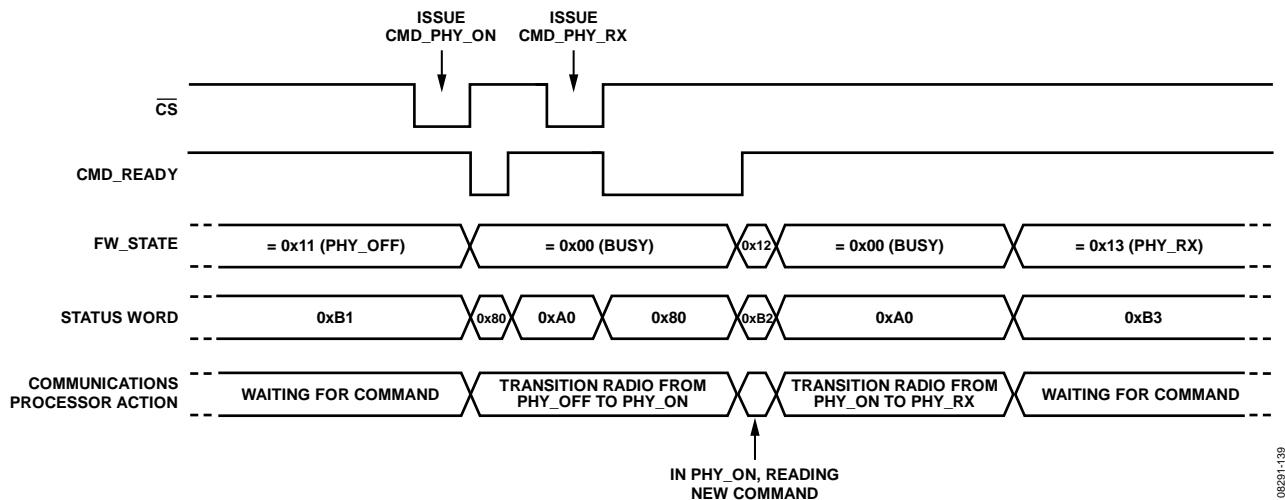

## 状态跃迁和命令时序

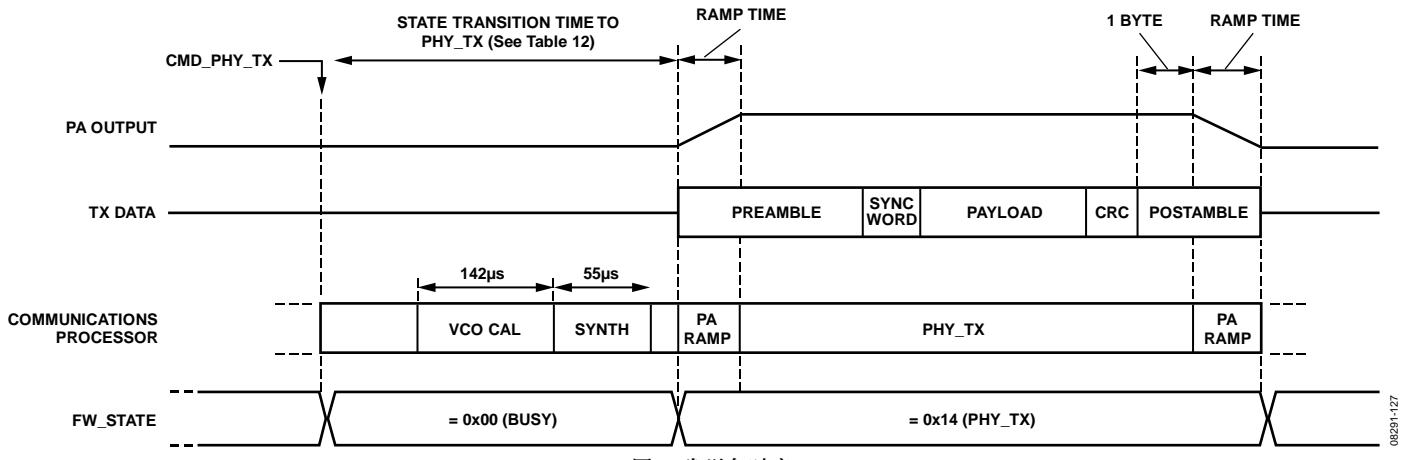

所有无线电状态跃迁的执行时间详见表11和表12。注意：这些时间是典型值，可能因不同的BBRAM配置而异。如需正常跃迁时间，请将TRANSITION\_CLOCK\_DIV(位置0x13A)设为0x04。如需快速跃迁时间，请将TRANSITION\_CLOCK\_DIV设为0x01。建议使能快速跃迁时间以降低系统功耗。

如SPI接口部分所述，命令在命令的最后一个正SCLK沿执行。对于表11和表12给出的值，最后一个正SCLK沿与CS上升沿之间存在一个200 ns的额外时间，它与所用的SPI速率有关。

表11. 与PHY\_TX或PHY\_RX无关的ADF7023命令执行时间和状态跃迁时间

| 命令/位                    | 命令发出者 | 当前状态      | 下一状态      | 正常跃迁时间(μs),<br>典型值 | 快速跃迁时间(μs),<br>典型值 | 条件                                                                              |

|-------------------------|-------|-----------|-----------|--------------------|--------------------|---------------------------------------------------------------------------------|

| CMD_HW_RESET            | 主机    | 任何        | PHY_SLEEP | 1                  | 1                  |                                                                                 |