# CMPA0060025D

# 25 W, 20 MHz - 6.0 GHz, GaN MMIC, Power Amplifier

Cree's CMPA0060025D is a gallium nitride (GaN) High Electron Mobility Transistor (HEMT) based monolithic microwave integrated circuit (MMIC). GaN has superior properties compared to silicon or gallium arsenide, including higher breakdown voltage, higher saturated electron drift velocity and higher thermal conductivity. GaN HEMTs also offer greater power density and wider bandwidths compared to Si and GaAs transistors. This MMIC enables very wide bandwidths.

PN: CMPA0060025D

# Typical Performance Over 1.0-6.0 GHz (T<sub>c</sub> = 25°C)

| Parameter                                | 1.0 GHz | 2.0 GHz | 3.0 GHz | 4.0 GHz | 5.0 GHz | 6.0 GHz | Units |

|------------------------------------------|---------|---------|---------|---------|---------|---------|-------|

| Gain                                     | 18.0    | 18.0    | 18.5    | 18.0    | 17.0    | 17.0    | dB    |

| Output Power @ P <sub>IN</sub> 32 dBm    | 34      | 38      | 42      | 29      | 30      | 31      | W     |

| Associated Gain @ P <sub>IN</sub> 32 dBm | 13.3    | 13.9    | 14.2    | 12.6    | 13.1    | 12.9    | dB    |

| PAE @ P <sub>IN</sub> 32 dBm             | 54      | 45      | 46      | 33      | 34      | 33      | %     |

Note:  $V_{DD}$  = 50 V,  $I_{D}$  = 500 mA

#### **Features**

- 18 dB Small Signal Gain

- 30 W Typical P<sub>SAT</sub>

- Operation up to 50 V

- · High Breakdown Voltage

- High Temperature Operation

- Size 0.157 x 0.094 x 0.004 inches

### **Applications**

- Ultra Broadband Amplifiers

- Test Instrumentation

- EMC Amplifier Drivers

# Absolute Maximum Ratings (not simultaneous) at 25°C

| Parameter                                                    | Symbol                             | Rating    | Units | Conditions |

|--------------------------------------------------------------|------------------------------------|-----------|-------|------------|

| Drain-source Voltage                                         | V <sub>DSS</sub>                   | 84        | VDC   |            |

| Gate-source Voltage                                          | $V_{\sf GS}$                       | -10, +2   | VDC   |            |

| Storage Temperature                                          | T <sub>STG</sub>                   | -65, +150 | °C    |            |

| Operating Junction Temperature                               | T <sub>J</sub>                     | 225       | °C    |            |

| Maximum Forward Gate Current                                 | I <sub>GMAX</sub>                  | 12        | mA    |            |

| Thermal Resistance, Junction to Case (packaged) <sup>1</sup> | $R_{\scriptscriptstyle{\thetaJC}}$ | 2.32      | °C/W  | 85°C       |

| Thermal Resistance (die only) 1                              | $R_{_{\theta JC}}$                 | 1.40      | °C/W  | 85°C       |

| Input Power <sup>2</sup>                                     | P <sub>IN</sub>                    | 36        | dBm   |            |

Note<sup>1</sup> Eutectic die attach using 80/20 AuSn solder mounted to a 10 mil thick CuMo carrier.

Note<sup>2</sup> Limit for internal resistor only. Thermal dissipation may be exceeded at this level.

# Electrical Characteristics (Frequency = 20 MHz to 6.0 GHz unless otherwise stated; T<sub>c</sub> = 25°C)

| Characteristics                      | Symbol            | Min. | Тур. | Max. | Units | Conditions                                                                                                  |

|--------------------------------------|-------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------------|

| DC Characteristics                   |                   |      |      |      |       |                                                                                                             |

| Gate Threshold Voltage <sup>1</sup>  | $V_{(GS)TH}$      | -3.8 | -3.0 | -2.7 | V     | $V_{DS} = 20 \text{ V, } \Delta I_{D} = 6 \text{ mA}$                                                       |

| Gate Quiescent Voltage               | $V_{(GS)Q}$       | -    | -2.7 | -    | VDC   | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA}$                                                           |

| Saturated Drain Current <sup>2</sup> | I <sub>DS</sub>   | -    | 12   | -    | А     | V <sub>DS</sub> = 12.0 V, V <sub>GS</sub> = 2.0 V                                                           |

| RF Characteristics                   |                   |      |      |      |       |                                                                                                             |

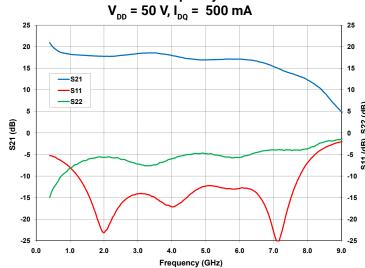

| Small Signal Gain                    | S21               | -    | 18   | -    | dB    | V <sub>DD</sub> = 50 V, I <sub>DQ</sub> = 500 mA                                                            |

| Input Return Loss                    | S11               | -    | 9    | -    | dB    | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA}$                                                           |

| Output Return Loss                   | S22               | -    | 7    | -    | dB    | V <sub>DD</sub> = 50 V, I <sub>DQ</sub> = 500 mA                                                            |

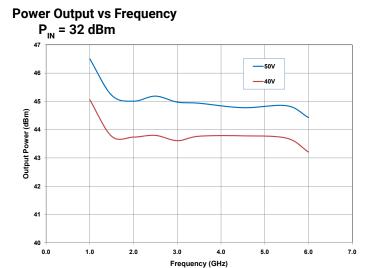

| Output Power, 1                      | P <sub>out1</sub> | 17   | 29   | -    | W     | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA,}$ $P_{IN} = 32 \text{ dBm, Freq} = 4.0 \text{ GHz}$        |

| Output Power, 2                      | P <sub>OUT2</sub> | 23   | 30   | -    | W     | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA,}$<br>$P_{IN} = 32 \text{ dBm, Freq} = 5.0 \text{ GHz}$     |

| Output Power, 3                      | P <sub>out3</sub> | 23   | 31   | -    | W     | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA,}$<br>$P_{IN} = 32 \text{ dBm, Freq} = 6.0 \text{ GHz}$     |

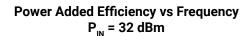

| Power Added Efficiency, 1            | PAE1              | 18   | 33   | -    | %     | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA,}$ $P_{IN} = 32 \text{ dBm, Freq} = 4.0 \text{ GHz}$        |

| Power Added Efficiency, 2            | PAE2              | 23   | 34   | -    | %     | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA,}$<br>$P_{IN} = 32 \text{ dBm, Freq} = 5.0 \text{ GHz}$     |

| Power Added Efficiency, 3            | PAE3              | 22   | 33   | -    | %     | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA,}$<br>$P_{IN} = 32 \text{ dBm, Freq} = 6.0 \text{ GHz}$     |

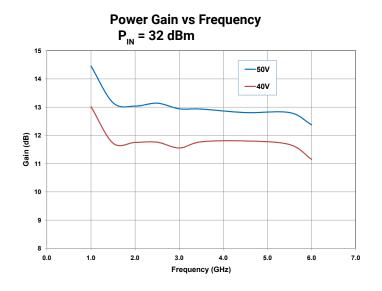

| Power Gain                           | $G_{p}$           | -    | 13   | -    | dB    | $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA,}$<br>$P_{IN} = 32 \text{ dBm}$                             |

| Output Mismatch Stress               | VSWR              | -    | -    | 5:1  | Ψ     | No damage at all phase angles, $V_{DD} = 50 \text{ V, } I_{DQ} = 500 \text{ mA,}$ $P_{IN} = 32 \text{ dBm}$ |

#### Notes:

<sup>&</sup>lt;sup>1</sup> The device will draw approximately 55-70 mA at pinch off due to the internal circuit structure.

<sup>&</sup>lt;sup>2</sup> Scaled from PCM data.

$<sup>^{3}</sup>$  All data pulsed with Pulse Width at 10 $\mu\text{S},$  1% Duty Cycle

<sup>&</sup>lt;sup>3</sup> Data measured into a 15 dB output load with a maximum return loss.

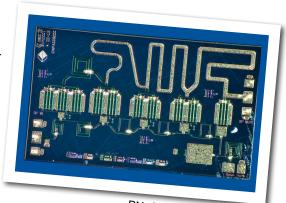

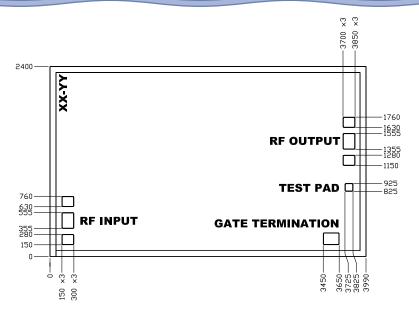

### **Die Dimensions (units in microns)**

Overall die size 3990 x 2400 (+0/-50) microns, die thickness 100 (+/-10) micron. All Gate and Drain pads must be wire bonded for electrical connection.

| Pad Number | Function            | Description                                                                                                  | Pad Size (microns) |

|------------|---------------------|--------------------------------------------------------------------------------------------------------------|--------------------|

| 1          | RF IN <sup>1</sup>  | RF-Input pad. Matched to 50 ohm. Requires gate control from an external bias $\neg$ T from -2.3 V to -3.8 V. | 150 x 200          |

| 2          | Gate Termination    | Off Chip termination for the Gate. It needs to be DC-blocked .                                               | 200 x 150          |

| 3          | RF OUT <sup>1</sup> | RF-Output pad. Matched to 50 ohm. Requires Drain supply from an external bias $\neg$ T up to 50 V , 2.0 A    | 150 x 200          |

#### Notes:

#### **Die Assembly Notes:**

- Recommended solder is AuSn (80/20) solder. Refer to Cree's website for the Eutectic Die Bond Procedure application note at <u>www.cree.com/RF/Document-Library</u>

- Vacuum collet is the preferred method of pick-up.

- The backside of the die is the Source (ground) contact.

- Die back side gold plating is 5 microns thick minimum.

- Thermosonic ball or wedge bonding are the preferred connection methods.

- · Gold wire must be used for connections.

- Test pad must be bonded to Ground.

- Use the die label (XX-YY) for correct orientation.

<sup>&</sup>lt;sup>1</sup> The RF In and Out pads have a ground-signal-ground configuration with a pitch of 75 microns.

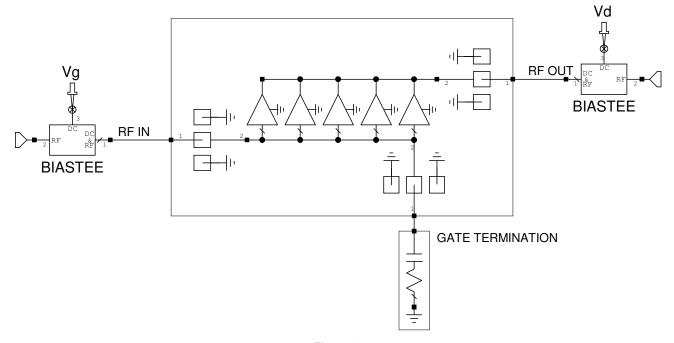

### **Functional Block Diagram**

This device employs a wideband amplifier topology. It has an internal termination for the Gate, which works well over 1.0-6.0 GHz. For operation below 1.0 GHz an external termination is required. This termination needs to be DC-blocked and suitable to withstand up to 2 W of RF power. (Refer to the reference design section for the LF-termination in this data sheet for more details). The circuits also require external wideband Bias –T's to supply voltage to the Gate and Drain. The Bias-T at the Drain needs to be designed to handle 50 V and up to 2.0 A.

Figure 1.

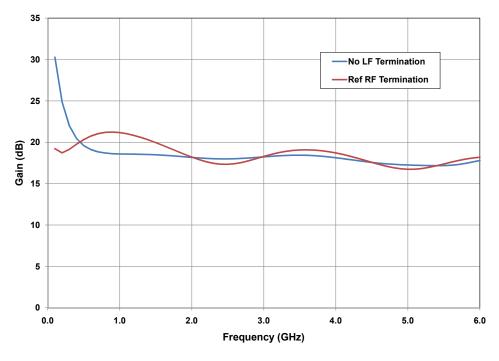

# **External Termination Reference Design**

The following is a plot of the gain of the die with and without an RC reference circuit.

#### Notes:

#### **RC Reference Circuit**

The reference circuit is a series capacitor and resistor as shown below.

Figure 2.

The resistor needs to handle 2.0 W.

<sup>&</sup>lt;sup>1</sup> An off chip termination is needed to reduce the high gain peak at low frequencies.

<sup>&</sup>lt;sup>2</sup> The off chip termination should be designed to minimize the impact on the MMIC's performance at higher frequencies.

# **Typical Performance**

### **Gain and Return Losses vs Frequency**

# **Electrostatic Discharge (ESD) Classifications**

| Parameter           | Symbol | Class            | Test Methodology    |

|---------------------|--------|------------------|---------------------|

| Human Body Model    | НВМ    | 1A (> 250 V)     | JEDEC JESD22 A114-D |

| Charge Device Model | CDM    | II (200 < 500 V) | JEDEC JESD22 C101-C |

# **Product Ordering Information**

| Order Number | Description                       | Unit of Measure |

|--------------|-----------------------------------|-----------------|

| CMPA0060025D | GaN MMIC Power Amplifier Bare Die | Each            |

#### **Disclaimer**

Specifications are subject to change without notice. Cree, Inc. believes the information contained within this data sheet to be accurate and reliable. However, no responsibility is assumed by Cree for its use or for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Cree. Cree makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose. "Typical" parameters are the average values expected by Cree in large quantities and are provided for information purposes only. These values can and do vary in different applications, and actual performance can vary over time. All operating parameters should be validated by customer's technical experts for each application. Cree products are not designed, intended, or authorized for use as components in applications intended for surgical implant into the body or to support or sustain life, in applications in which the failure of the Cree product could result in personal injury or death, or in applications for the planning, construction, maintenance or direct operation of a nuclear facility. CREE and the CREE logo are registered trademarks of Cree, Inc.

For more information, please contact:

Cree, Inc. 4600 Silicon Drive Durham, North Carolina, USA 27703 www.cree.com/RF

Sarah Miller Marketing Cree, RF Components 1.919.407.5302

Ryan Baker Marketing & Sales Cree, RF Components 1.919.407.7816

Tom Dekker Sales Director Cree, RF Components 1.919.407.5639