SBAS437A-MAY 2008-REVISED JUNE 2009

# LOW-POWER, 12-BIT, 1MHz, SINGLE/DUAL UNIPOLAR INPUT, ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL INTERFACE

#### **FEATURES**

- 2.7V to 5.5V Analog Supply, Low Power:

- 13.7mW (1MHz, +VA = 3V, +VBD = 1.8V)

- 1MHz Sampling Rate 3V ≤ +VA ≤ 5.5V, 900kHz Sampling Rate 2.7V ≤ +VA ≤ 3V

- Excellent DC Performance:

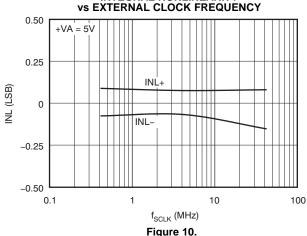

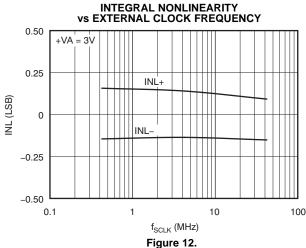

- ±0.15LSB Typ, ±0.5LSB Max INL

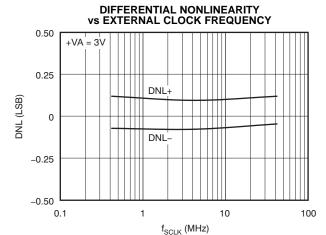

- ±0.12LSB Typ, ±0.5LSB Max DNL

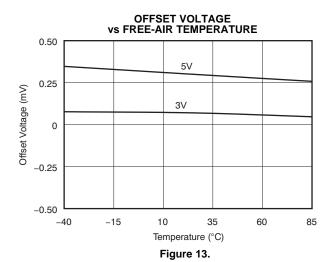

- ±0.8mV Max Offset Error at 3V

- ±1.25mV Max Offset Error at 5V

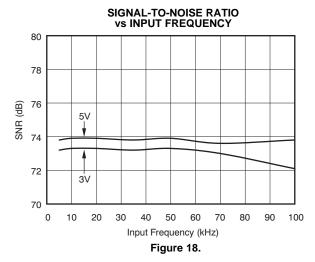

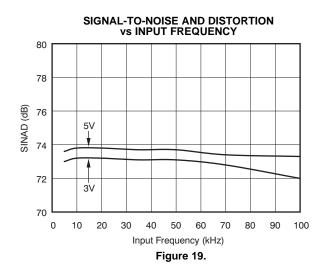

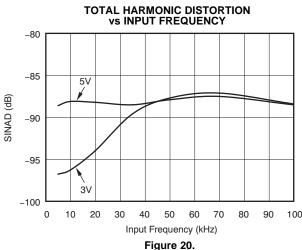

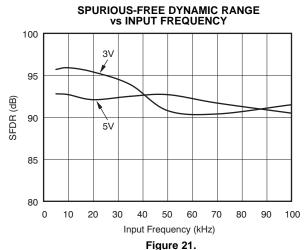

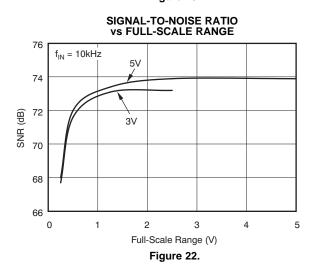

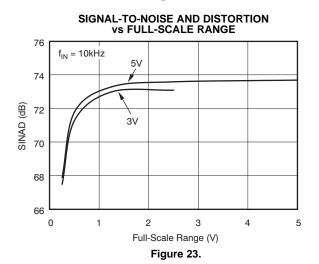

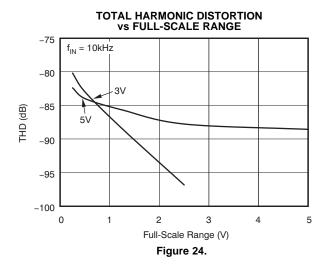

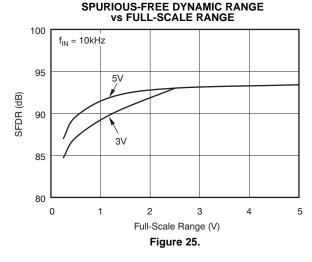

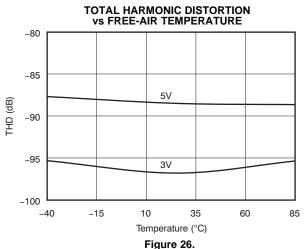

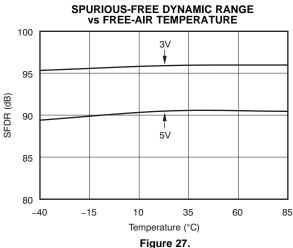

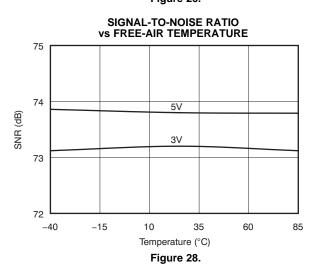

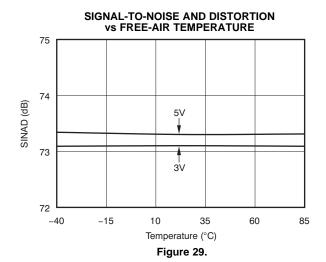

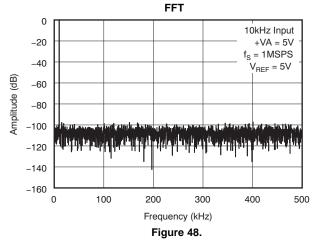

- Excellent AC Performance at f<sub>1</sub> = 10kHz with 73.9dB SNR, 93.4dB SFDR, -88.5dB THD

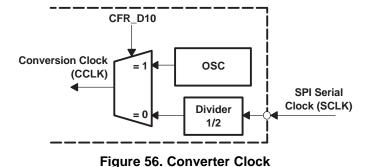

- Built-In Conversion Clock (CCLK)

- 1.65V to 5.5V I/O Supply:

- SPI™/DSP-Compatible Serial Interface

- SCLK up to 50MHz

- Comprehensive Power-Down Modes:

- Deep Power-Down

- Nap Power-Down

- Auto Nap Power-Down

- Unipolar Input Range: 0V to VREE

- Software Reset

- Global CONVST (Independent of CS)

- Programmable Status/Polarity EOC/INT

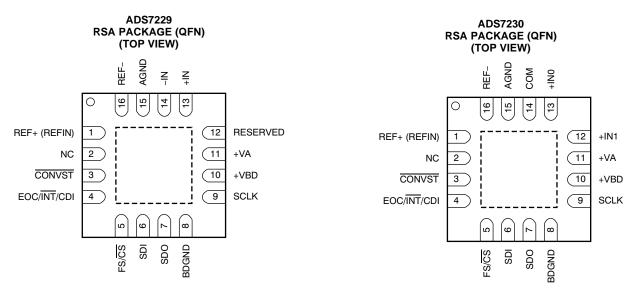

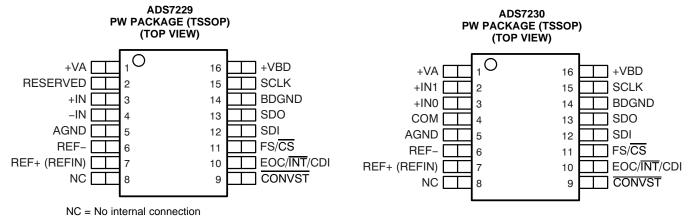

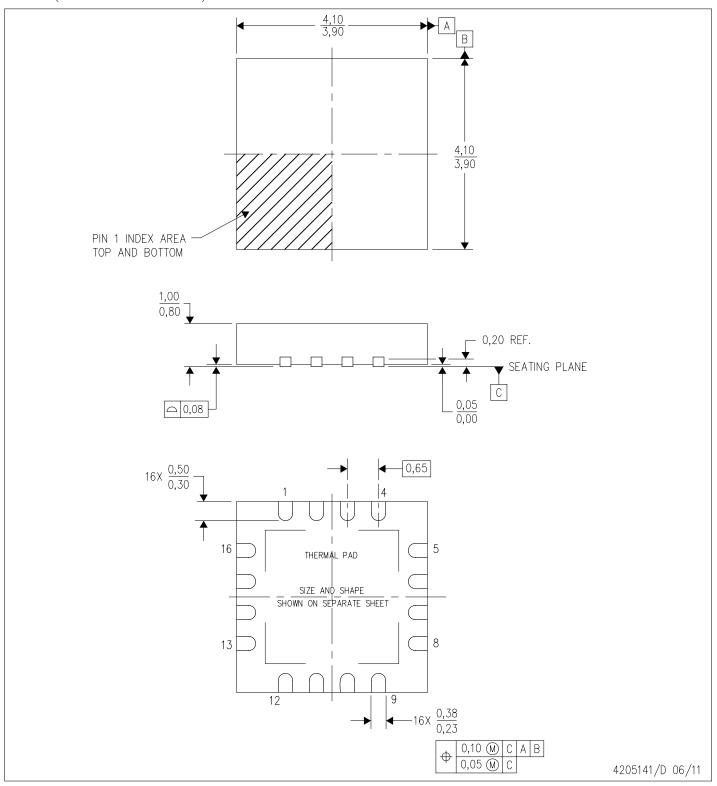

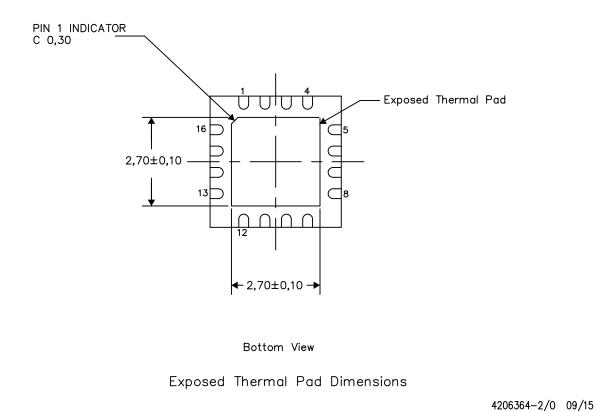

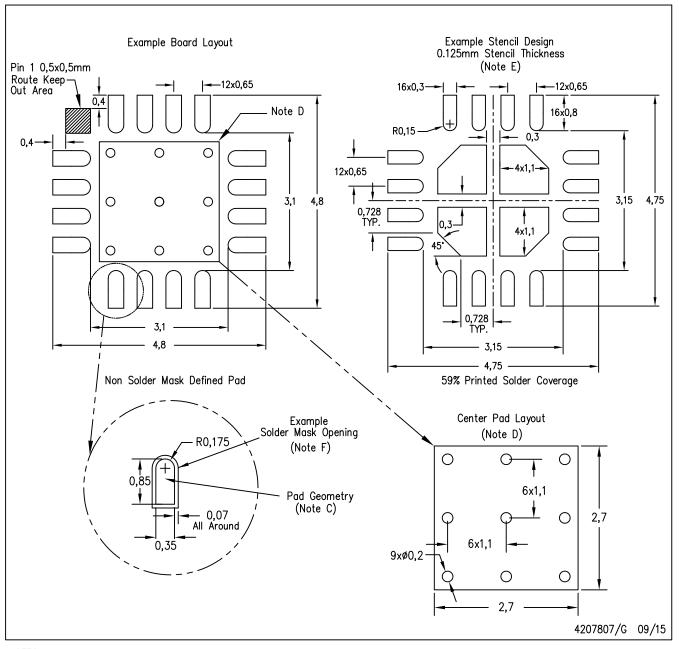

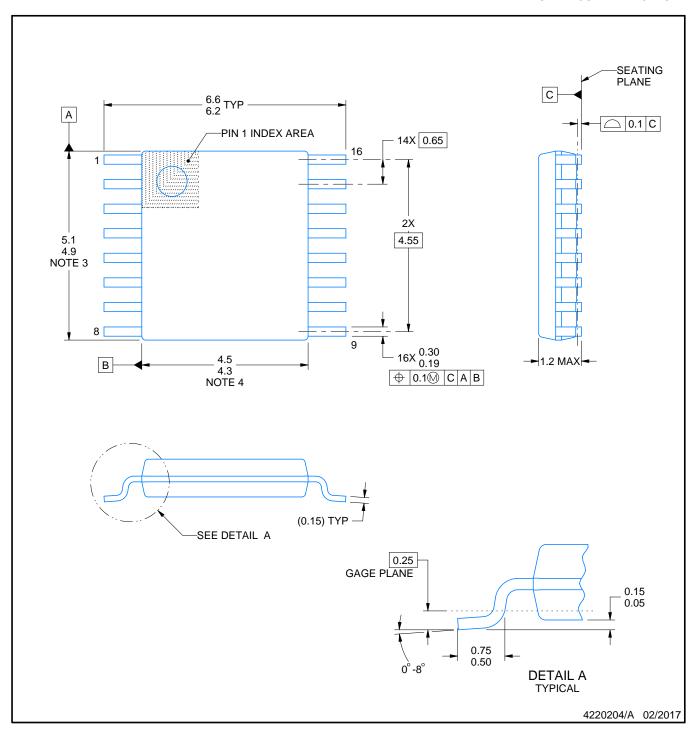

- 4 x 4 QFN-16 and TSSOP-16 Packages

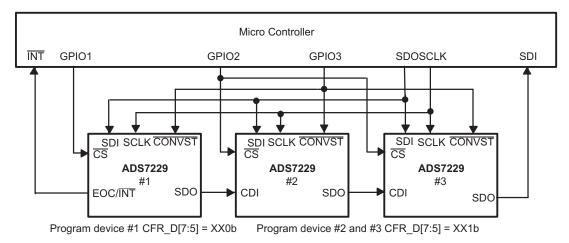

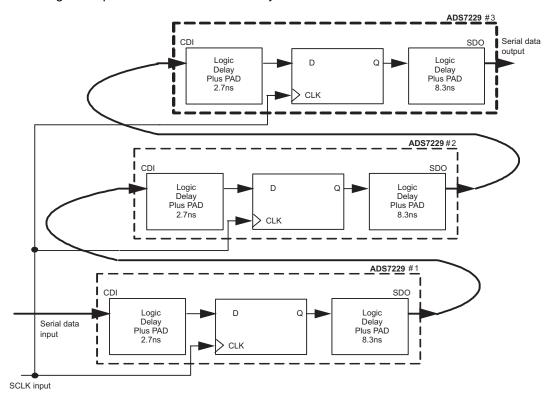

- Multi-Chip Daisy-Chain Mode

- Programmable TAG Bit Output

- Auto/Manual Channel Select Mode (ADS7230)

## **APPLICATIONS**

- Communications

- Transducer Interface

- Medical Instruments

- Magnetometers

- Industrial Process Control

- Data Acquisition Systems

- Automatic Test Equipment

## DESCRIPTION

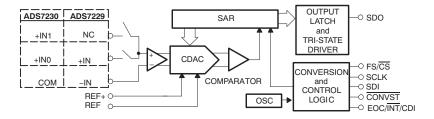

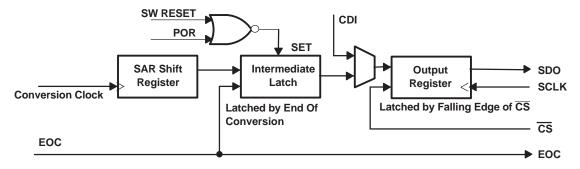

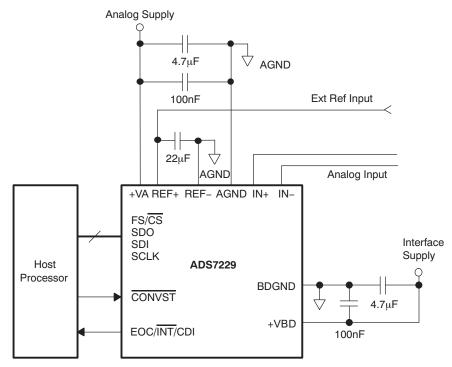

The ADS7229 is a low-power, 12-bit, 1MSPS analog-to-digital converter (ADC) with a unipolar input. The device includes a 12-bit capacitor-based successive approximation register (SAR) ADC with inherent sample-and-hold.

The ADS7230 is based on the same core and includes a 2-to-1 input MUX with a programmable TAG bit output option. Both the ADS7229 and ADS7230 offer a high-speed, wide voltage serial interface and are capable of daisy-chain mode operation when multiple converters are used.

These devices are available in  $4 \times 4$  QFN and TSSOP-16 packages, and are fully specified for operation over the industrial  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

### Low Power, High-Speed SAR Converter Family

| Type/Speed          | 500 kSPS | 1 MSPS  |         |

|---------------------|----------|---------|---------|

| 16-bit single-ended | Single   | ADS8327 | ADS8329 |

|                     | Dual     | ADS8328 | ADS8330 |

|                     | Single   | _       | ADS7279 |

| 14-bit single-ended | Dual     | _       | ADS7280 |

| 10 hit single anded | Single   | _       | ADS7229 |

| 12-bit single-ended | Dual     | _       | ADS7230 |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI is a trademark of Motorola, Inc.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## ORDERING INFORMATION(1)

| MODEL    | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>OFFSET<br>ERROR<br>(mV) | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | TEMPERATURE<br>RANGE | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA,<br>QUANTITY |                |            |          |       |              |     |                |              |                     |

|----------|-------------------------------------------|-----------------------------------------------|------------------------------------|-----------------|-----------------------|----------------------|-------------------------|---------------------------------|----------------|------------|----------|-------|--------------|-----|----------------|--------------|---------------------|

|          |                                           |                                               | ±1.25                              | 4 × 4 QFN-16    | 6 RSA                 |                      | ADS7229IRSAT            | Small tape and reel, 250        |                |            |          |       |              |     |                |              |                     |

| ADS72291 | ±0.5                                      | ±0.5                                          |                                    | ±1.25           | ±1.25                 | .1.25                | .1 2E                   | +1 25                           | ±1 25          | +1 25      | .1.25    | .4.05 | 4 X 4 QFN-10 | KSA | -40°C to +85°C | ADS7229IRSAR | Tape and reel, 3000 |

| AD372291 | ±0.5                                      | ±0.5                                          |                                    |                 |                       | TSSOP-16             | PW                      | 40 0 10 100 0                   | ADS7229IPW     | Tube, 90   |          |       |              |     |                |              |                     |

|          |                                           |                                               |                                    | 1330F-16        | 15551-10              |                      | ADS7229IPWR             | Tape and reel, 2000             |                |            |          |       |              |     |                |              |                     |

|          |                                           |                                               | ±1.25                              | 4 × 4 QFN-16    | RSA                   |                      | ADS7230IRSAT            | Small tape and reel, 250        |                |            |          |       |              |     |                |              |                     |

| ADS72301 | ±0.5                                      | ±0.5                                          |                                    |                 |                       | -40°C to +85°C       | ADS7230IRSAR            | Tape and reel, 3000             |                |            |          |       |              |     |                |              |                     |

| AD372301 | ±0.5                                      | ±∪.5                                          |                                    | ±1.25           | ±1.25                 |                      | TSSOP-16                | PW                              | -40 C (0 +85°C | ADS7230IPW | Tube, 90 |       |              |     |                |              |                     |

|          |                                           |                                               |                                    | 1330P-16        | FVV                   |                      | ADS7230IPWR             | Tape and reel, 2000             |                |            |          |       |              |     |                |              |                     |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                       |                       |                                 | ADS7229, ADS7230                 | UNIT |

|-----------------------|-----------------------|---------------------------------|----------------------------------|------|

|                       | Valtana               | +IN to AGND                     | -0.3 to +VA + 0.3                | V    |

|                       | Voltage               | -IN to AGND                     | -0.3 to +VA + 0.3                | V    |

|                       |                       | +VA to AGND                     | -0.3 to 7                        | V    |

|                       | Voltage range         | +REF to AGND                    | -0.3 to +VA + 0.3                | V    |

|                       |                       | -REF to AGND                    | -0.3 to 0.3                      | V    |

|                       |                       | +VBD to BDGND                   | -0.3 to 7                        | V    |

|                       |                       | AGND to BDGND                   | -0.3 to 0.3                      | V    |

|                       | Digital input voltage | ge to BDGND                     | -0.3 to +VBD + 0.3               | V    |

|                       | Digital output volt   | age to BDGND                    | -0.3 to +VBD + 0.3               | V    |

| T <sub>A</sub>        | Operating free-air    | temperature range               | -40 to +85                       | °C   |

| T <sub>STG</sub>      | Storage temperat      | ure range                       | -65 to +150                      | °C   |

| T <sub>J</sub><br>max | Junction tempera      | ure                             | +150                             | °C   |

|                       | 4 × 4 QFN-16          | Power dissipation               | $(T_{J}max - T_{A})/\theta_{JA}$ |      |

|                       | package               | $\theta_{JA}$ thermal impedance | 47                               | °C/W |

|                       | TSSOP-16              | Power dissipation               | $(T_{J}max - T_{A})/\theta_{JA}$ |      |

|                       | package               | $\theta_{JA}$ thermal impedance | 86                               | °C/W |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

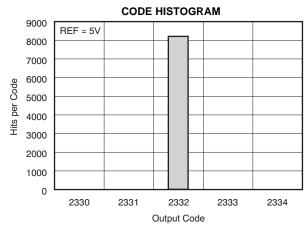

## **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40$ °C to +85°C, +VA = 4.5V to 5.5V, +VBD = +1.65V to +5.5V,  $V_{REF} = 5V$ , and  $f_{SAMPLE} = 1$ MHz, unless otherwise

|                      |                                         |                                     | ADS72      | 229, ADS72 | 230        |                      |

|----------------------|-----------------------------------------|-------------------------------------|------------|------------|------------|----------------------|

|                      | PARAMETER                               | PARAMETER TEST CONDITIONS           |            |            |            | UNIT                 |

| ANALOG               | INPUT                                   |                                     |            |            |            |                      |

| FSR                  | Full-scale input voltage <sup>(1)</sup> | +IN - (-IN) or (+INx - COM)         | 0          |            | $V_{REF}$  | V                    |

|                      | Absolute input voltage                  | +IN, +IN0, +IN1                     | AGND - 0.2 |            | +VA + 0.2  | V                    |

|                      | Absolute input voltage                  | –IN or COM                          | AGND - 0.2 |            | AGND + 0.2 | V                    |

|                      | Input capacitance                       |                                     |            |            | 45         | pF                   |

|                      | Input leakage current                   | No ongoing conversion, dc input     |            | 50         |            | nA                   |

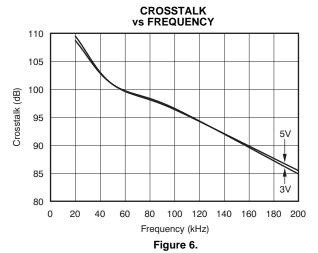

|                      | Input channel isolation, ADS7230 only   | At dc                               |            | 109        |            | dB                   |

|                      | input channel isolation, ADS7230 only   | $V_I = \pm 1.25 V_{PP}$ at 50kHz    |            | 101        |            | uБ                   |

| SYSTEM               | PERFORMANCE                             |                                     |            |            |            |                      |

|                      | Resolution                              |                                     |            | 12         |            | Bits                 |

| NMC                  | No missing codes                        |                                     | 12         |            |            | Bits                 |

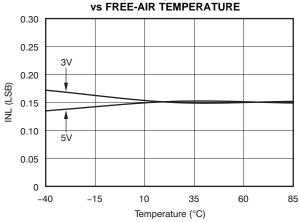

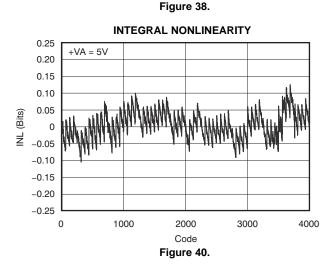

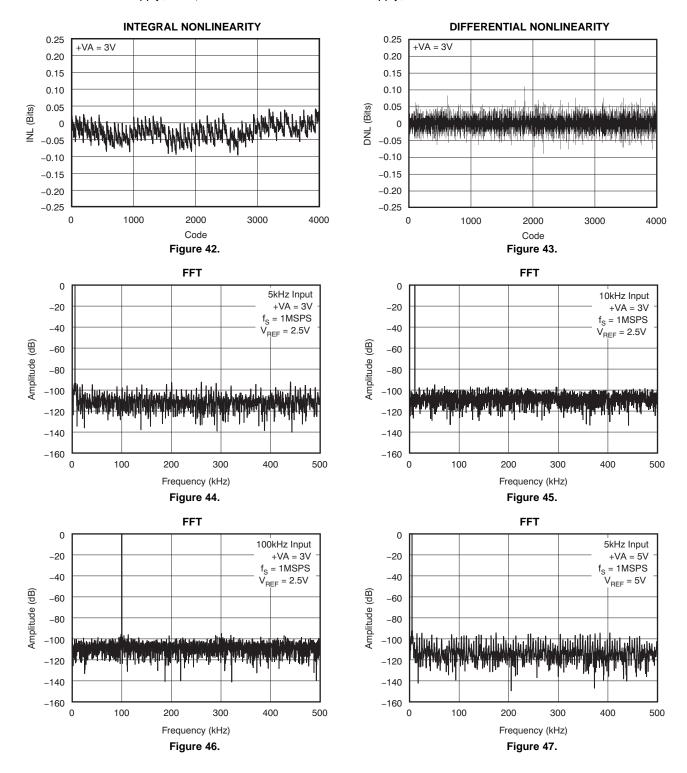

| INL                  | Integral linearity                      |                                     | -0.5       | ±0.15      | 0.5        | LSB <sup>(2)</sup>   |

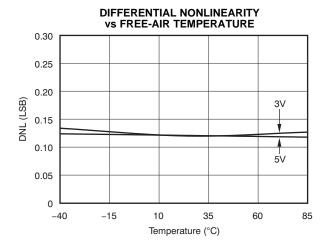

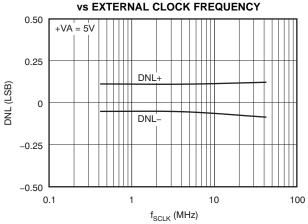

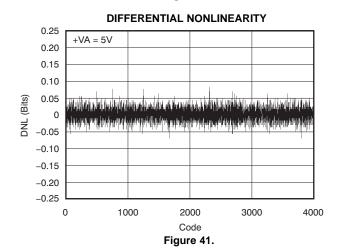

| DNL                  | Differential linearity                  |                                     | -0.5       | ±0.12      | 0.5        | LSB <sup>(2)</sup>   |

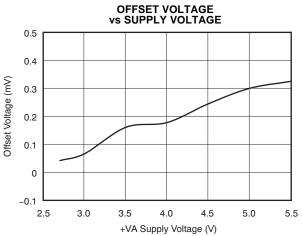

| Eo                   | Offset error <sup>(3)</sup>             |                                     | -1.25      | ±0.3       | 1.25       | mV                   |

|                      | Offset error drift                      | FSR = 5V                            |            | ±0.2       |            | ppm/°C               |

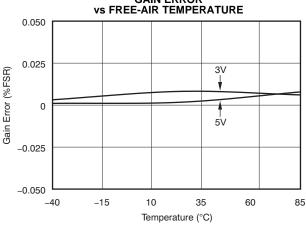

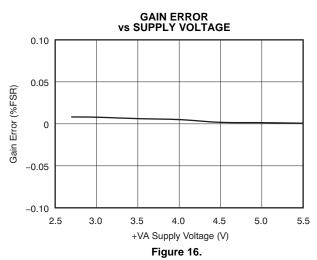

| E <sub>G</sub>       | Gain error                              |                                     | -0.1       | ±0.002     | 0.1        | %FSR                 |

|                      | Gain error drift                        |                                     |            | ±0.5       |            | ppm/°C               |

| CMRR                 | Common-mode rejection ratio             | At dc                               |            | 70         |            | dB                   |

| Civiltit             | Common-mode rejection ratio             | $V_I = 0.4V_{PP}$ at 1MHz           |            | 50         |            | uБ                   |

|                      | Noise                                   |                                     |            | 33         |            | $\mu V_{\text{RMS}}$ |

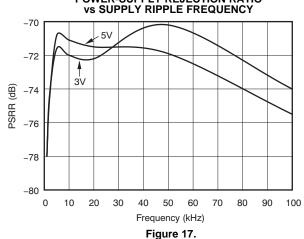

| PSRR                 | Power-supply rejection ratio            | At FFFFh output code <sup>(3)</sup> |            | 78         |            | dB                   |

| SAMPLIN              | NG DYNAMICS                             |                                     |            |            |            |                      |

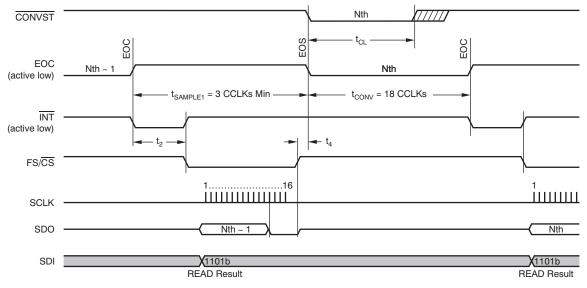

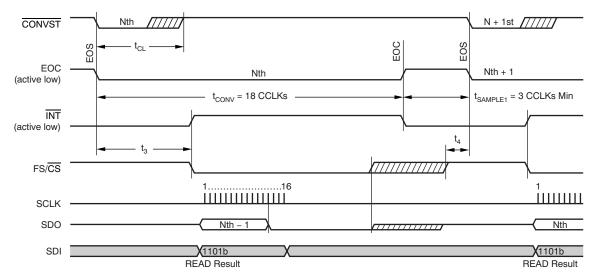

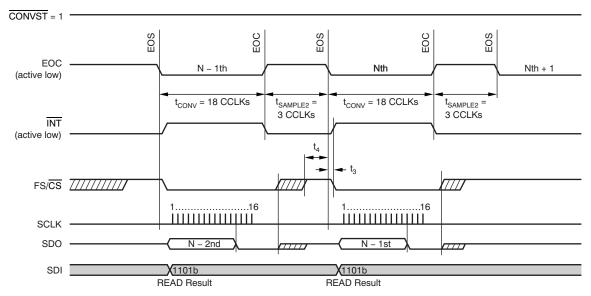

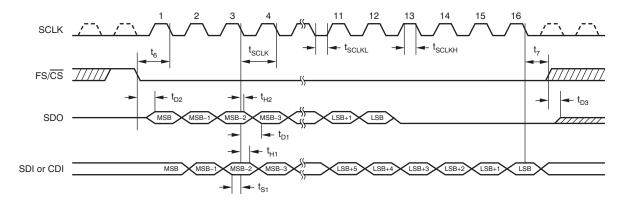

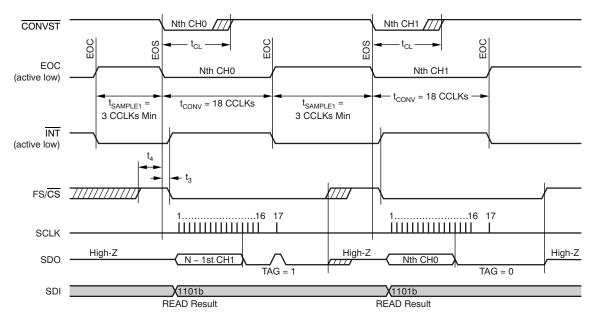

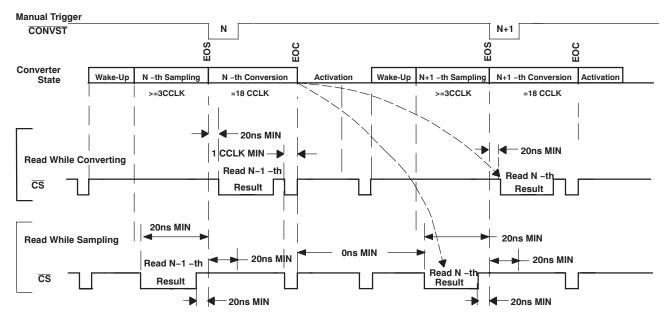

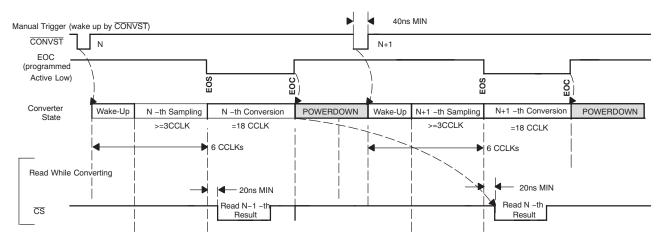

| $t_{\text{CONV}}$    | Conversion time                         |                                     |            | 18         |            | CCLK                 |

| t <sub>SAMPLE1</sub> | - Acquisition time                      | Manual trigger                      | 3          |            |            | CCLK                 |

| t <sub>SAMPLE2</sub> | Acquisition time                        | Auto trigger                        |            | 3          |            | COLK                 |

|                      | Throughput rate                         |                                     |            |            | 1          | MHz                  |

|                      | Aperture delay                          |                                     |            | 5          |            | ns                   |

|                      | Aperture jitter                         |                                     |            | 10         |            | ps                   |

|                      | Step response                           |                                     |            | 100        |            | ns                   |

|                      | Overvoltage recovery                    |                                     |            | 100        |            | ns                   |

Ideal input span; does not include gain or offset error. LSB means least significant bit.

Measured relative to an ideal full-scale input [(+IN) - (-IN)] of 4.096V when +VA = 5V.

At  $T_A = -40$ °C to +85°C, +VA = 4.5V to 5.5V, +VBD = +1.65V to +5.5V,  $V_{REF} = 5V$ , and  $f_{SAMPLE} = 1MHz$ , unless otherwise noted.

|                  |                           |                                    |                                               |               | 29, ADS72 |                  |        |

|------------------|---------------------------|------------------------------------|-----------------------------------------------|---------------|-----------|------------------|--------|

|                  | PARAI                     | METER                              | TEST CONDITIONS                               | MIN           | TYP       | MAX              | UNIT   |

| DYNAMI           | C CHARACTERIS             | STICS                              |                                               |               |           | 1                |        |

| THD              | Total harmonic            | distortion (4)                     | $V_{IN} = 5V_{PP}$ at 10kHz                   |               | -88.5     |                  | dB     |

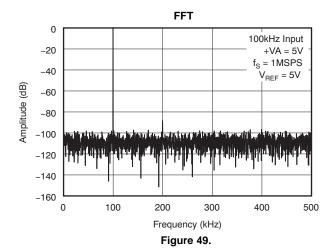

|                  |                           | 4.0.0.1.0.1.                       | $V_{IN} = 5V_{PP}$ at 100kHz                  |               | -85.5     |                  |        |

| SNR              | Signal-to-noise           | ratio                              | $V_{IN} = 5V_{PP}$ at $10kHz$                 |               | 73.9      |                  | dB     |

| OIVIX            | Oignar to noise           | Tatio                              | $V_{IN} = 5V_{PP}$ at 100kHz                  | 72            | 73.8      |                  | uD     |

| SINAD            | Signal-to-noise           | + distortion                       | $V_{IN} = 5V_{PP}$ at $10kHz$                 |               | 73.7      |                  | dB     |

| SINAD            | Signal-to-noise           | + distortion                       | $V_{IN} = 5V_{PP}$ at 100kHz                  |               | 73.3      |                  | ub     |

| SFDR             | Spurious fros             | lynamia ranga                      | $V_{IN} = 5V_{PP}$ at $10kHz$                 |               | 93.4      |                  | dB     |

| SFDK             | Spurious-free d           | iynamic range                      | $V_{IN} = 5V_{PP}$ at 100kHz                  |               | 90.5      |                  | uБ     |

|                  | –3dB small-sigi           | nal bandwidth                      |                                               |               | 30        |                  | MHz    |

| CLOCK            |                           |                                    |                                               |               |           | <u> </u>         |        |

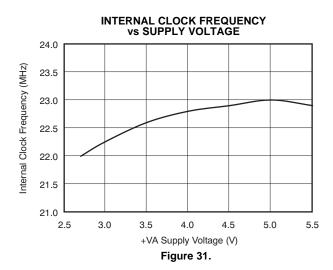

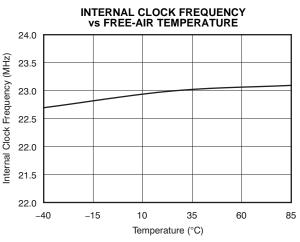

|                  | Internal conver           | sion clock frequency               |                                               | 21            | 23        | 24.5             | MHz    |

|                  | 001 K                     | and alone                          | Used as I/O clock only                        |               |           | 50               | B 41.1 |

|                  | SCLK external             | Serial Clock                       | As I/O clock and conversion clock             | 1             |           | 42               | MHz    |

| EXTERN           | IAL VOLTAGE RI            | EFERENCE INPUT                     |                                               |               |           |                  |        |

|                  | Input                     | V <sub>REF</sub> [(REF+) – (REF–)] |                                               | 0.3           |           | +VA              |        |

| V <sub>REF</sub> | reference<br>range        | (REF-) - AGND                      |                                               | -0.1          |           | 0.1              | V      |

|                  | Resistance <sup>(5)</sup> |                                    | Reference input                               |               | 40        |                  | kΩ     |

| DIGITAL          | . INPUT/OUTPUT            |                                    | ·                                             |               |           | <u> </u>         |        |

|                  | Logic family—C            | CMOS                               |                                               |               |           |                  |        |

| V <sub>IH</sub>  | High-level inpu           | t voltage                          | 5.5V ≥ +VBD ≥ 4.5V                            | 0.65 × (+VBD) |           | +VBD + 0.3       | V      |

| V <sub>IL</sub>  | Low-level input           | voltage                            | 5.5V ≥ +VBD ≥ 4.5V                            | -0.3          |           | 0.35 ×<br>(+VBD) | V      |

| l <sub>l</sub>   | Input current             |                                    | V <sub>I</sub> = +VBD or BDGND                | -50           |           | 50               | nA     |

| Cı               | Input capacitan           | се                                 |                                               |               | 5         |                  | pF     |

| V <sub>OH</sub>  | High-level outp           | ut voltage                         | 5.5V ≥ +VBD ≥ 4.5V,<br>I <sub>O</sub> = 100µA | +VBD - 0.6    |           | +VBD             | V      |

| V <sub>OL</sub>  | Low-level outpu           | ut voltage                         | 5.5V ≥ +VBD ≥ 4.5V,<br>I <sub>O</sub> = 100µA | 0             |           | 0.4              | V      |

| Co               | Output capacita           | ance                               |                                               |               | 5         |                  | pF     |

| C <sub>L</sub>   | Load capacitan            | се                                 |                                               |               |           | 30               | pF     |

|                  | Data format—s             | traight binary                     |                                               |               |           |                  |        |

| POWER-           | -SUPPLY REQUII            | REMENTS                            |                                               |               |           |                  |        |

|                  | Power-supply              | +VBD                               |                                               | 1.65          | 3.3       | 5.5              | V      |

|                  | voltage                   | +VA                                |                                               | 4.5           | 5         | 5.5              | V      |

|                  |                           | ı                                  | 1MHz sample rate                              |               | 5.7       | 7.0              |        |

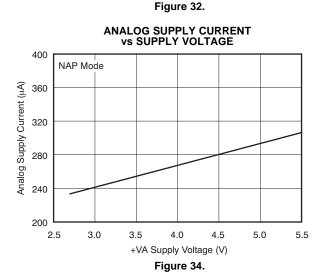

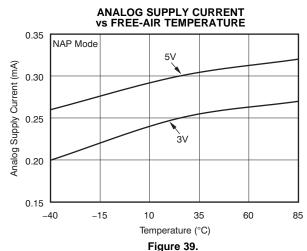

|                  | Supply current            |                                    | Nap or Auto Nap mode                          |               | 0.3       | 0.5              | mA     |

| ,                |                           |                                    | Deep power-down mode                          |               | 4         | 1                | μΑ     |

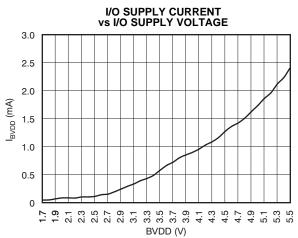

|                  |                           |                                    | 1MSPS, BVDD = 1.8V                            |               | 0.1       | 0.5              |        |

|                  | Buffer I/O supply current |                                    | 1MSPS, BVDD = 3V                              |               | 0.5       | 1.2              | mA     |

|                  |                           |                                    | AVDD = 5V, BVDD = 1.8V                        |               | 28.8      | 36.5             |        |

|                  | Power dissipati           | on                                 | AVDD = 5V, BVDD = 3V                          |               | 30.0      | 38.6             | mW     |

| TEMPER           | RATURE RANGE              |                                    |                                               |               | 50.0      | 50.5             |        |

|                  | ALONE KANGE               |                                    |                                               |               |           |                  |        |

<sup>(4)</sup> Calculated on the first nine harmonics of the input frequency.

<sup>(5)</sup> Can vary ±30%.

## **ELECTRICAL CHARACTERISTICS**

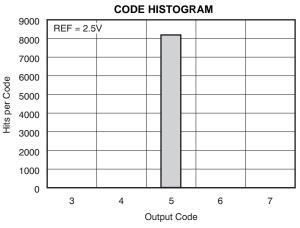

At  $T_A = -40$ °C to +85°C, +VA = 2.7V to 3.6V, +VBD = 1.65V to 1.5 x (+VA),  $V_{REF} = 2.5V$ ,  $f_{SAMPLE} = 1$ MHz for 3V ≤ +VA ≤ 3.6V, and  $f_{SAMPLE} = 900$ kHz for 3V < +VA ≤ 2.7V using external clock, unless otherwise noted.

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     | ADS7       | 229, ADS72 | 30         |                    |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------|------------|------------|--------------------|

|                      | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                     | MIN        | TYP        | MAX        | UNIT               |

| ANALOG               | INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ·                                   |            |            |            |                    |

| FSR                  | Full-scale input voltage <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | +IN - (-IN) or (+INx - COM)         | 0          |            | $V_{REF}$  | V                  |

|                      | Ab a shirts in more transfer ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | +IN, +IN0, +IN1                     | AGND - 0.2 |            | +VA + 0.2  | V                  |

|                      | Absolute input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | –IN or COM                          | AGND - 0.2 |            | AGND + 0.2 | V                  |

|                      | Input capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |            |            | 45         | pF                 |

|                      | Input leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No ongoing conversion, dc Input     |            | 50         |            | nA                 |

|                      | Input channel inelation, ADC7220 only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | At dc                               |            | 108        |            | dB                 |

|                      | Input channel isolation, ADS7230 only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $V_I = \pm 1.25 V_{PP}$ at $50 kHz$ |            | 101        |            | αв                 |

| SYSTEM               | PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                     |            |            |            |                    |

|                      | Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |            | 12         |            | Bits               |

|                      | No missing codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     | 12         |            |            | Bits               |

| INL                  | Integral linearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     | -0.5       | ±0.15      | 0.5        | LSB <sup>(2)</sup> |

| DNL                  | Differential linearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                     | -0.5       | ±0.12      | 0.5        | LSB <sup>(2)</sup> |

| Eo                   | Offset error <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                     | -0.8       | ±0.07      | 0.8        | mV                 |

|                      | Offset error drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FSR = 2.5V                          |            | ±0.1       |            | ppm/°C             |

| E <sub>G</sub>       | Gain error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     | -0.1       | ±0.008     | 0.1        | %FSR               |

|                      | Gain error drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |            | ±0.3       |            | ppm/°C             |

| OMDD                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | At dc                               | 70         |            |            | -ID                |

| CMRR                 | Common-mode rejection ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_I = 0.4V_{PP}$ at 1MHz           | 50         |            |            | dB                 |

|                      | Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |            | 33         |            | $\mu V_{RMS}$      |

| PSRR                 | Power-supply rejection ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | At FFFFh output code (3)            |            | 78         |            | dB                 |