并行/串行选择

可使用并行或串行接口进行控制,PE43711的P/S引脚提供此选择功能。P/S=LOW时选择并行接口,P/S=HIGH时选择串行接口。

并行模式接口

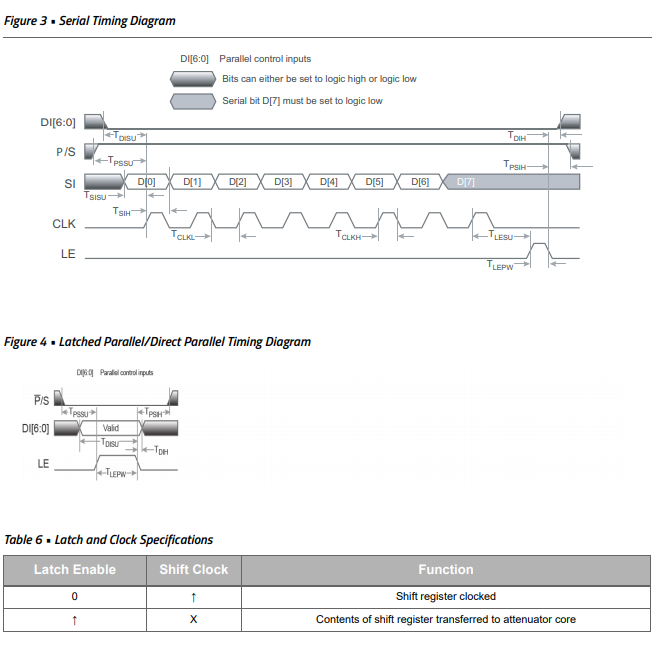

并行接口由七条CMOS兼容的控制线组成,用于选择所需的衰减状态,如表4所示。并行接口的时序要求在表8(并行接口时序图)、表4(并行接口直流特性)和开关时间(表3)中定义。

对于锁存并行编程,锁存使能(LE)在更改衰减状态控制值时应保持为低电平,然后将LE从高电平脉冲至低电平(见表4)以锁存新值。

在直接并行编程中,LE线应拉高。更改衰减状态控制值将直接使器件状态变为新的衰减值。直接模式适用于手动控制器件(使用硬件、开关或跳线)。

串行接口

串行接口是一个8位移位寄存器,后接一个透明锁存器。这8位构成一个衰减字,用于控制DSA。图3中的时序图示例说明了编程一个状态的时序。

串行接口使用三条CMOS兼容的信号进行控制:时钟(CLK)、串行输入(SI)和LE。SI和CLK输入允许串行数据被移入。数据应在时钟的上升沿串行锁存,先输入最高位。

在加载移位寄存器时,必须将LE保持为低电平,以防止衰减值在数据输入期间发生变化。当所有数据输入完成后,应将LE拉高,然后再拉低,将新数据锁存并送入DSA。表5中列出了串行寄存器的编程示例。图2为串行寄存器的逻辑真值表,图3为串行时序图示例。当DSA工作在串行模式时,所有并行控制输入必须接地。

上电控制设置

PE43711在上电时将始终初始化为衰减设置(31.75 dB)和下一个编程字。在直接并行模式下,该设置将保持不变,直到用户重新编程该字。在DSA上电期间,可通过在电源接通前预设并行控制引脚的状态,将衰减范围预设为31.75 dB以内的任何状态。在此模式下,DSA有400 μs的上电时间延迟,器件在此期间完成初始化。在上电期间,衰减设置(31.75 dB)在默认为用户定义状态之前有效。如果控制引脚悬空,器件在上电时将默认为动态衰减状态(插入损耗)。

串行和并行编程模式之间可以动态切换。

如果DSA在上电时工作在串行模式(P/S=HIGH),所有并行控制输入(DI[6:0])必须设置为逻辑低电平。在切换至并行模式之前,必须通过串行编程将DI[7]设置为逻辑低电平。

如果DSA在上电时工作在并行模式(无论是锁存模式还是直接模式),所有并行引脚(DI[6:0])必须设置为逻辑低电平,并保持低电平,直到DSA通过串行编程确保DI[7]被设置为逻辑低电平(P/S=HIGH)。

此序列仅在上电时需要执行一次。完成后,可随时在串行和并行编程模式之间切换DSA。