一、布局

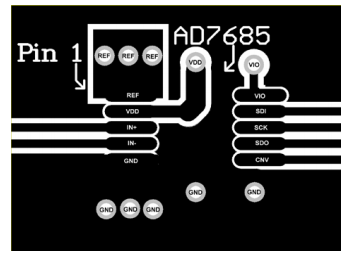

容纳 AD7685 的印刷电路板(PCB)应设计为将模拟部分和数字部分分开,并限制在电路板的特定区域。AD7685 模数的引脚排列将所有模拟信号放在左侧,所有数字信号放在右侧,便于此任务。

避免在器件下方走数字线,除非 AD7685 下方的地平面用作屏蔽,否则这些线会将噪声耦合到芯片上。快速开关信号(如 CNV 或时钟)不应靠近模拟信号路径运行。应避免数字和模拟信号交叉。

至少应使用一个地平面。它可以是公共地平面,或在数字和模拟部分之间分割。在后一种情况下,地平面应在 AD7685 下方连接。

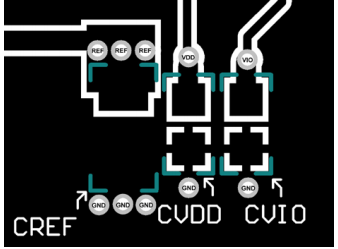

AD7685 的电压基准输入 REF 具有动态输入阻抗,应使用最小寄生电感进行去耦。这是通过将参考去耦陶瓷电容放置在靠近(理想情况下直接紧贴)REF 和 GND 引脚的位置,并使用宽而低阻抗的走线连接来实现的。

最后,电源 VDD 和 VIO 应使用陶瓷电容(通常为 100 nF)进行去耦,放置在靠近 AD7685 的位置,并使用短而宽的走线连接,以提供低阻抗路径并减少电源线上的毛刺效应。

遵循这些规则的布局示例如下面两张图片所示。

二、真正的 16 位隔离应用示例

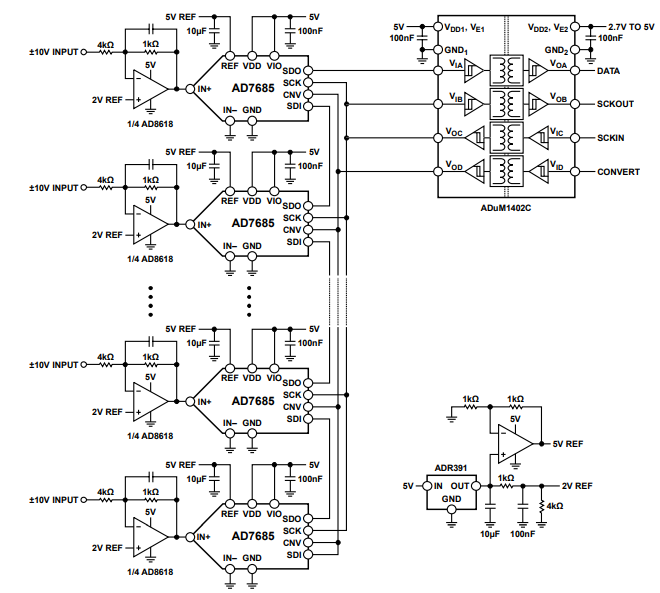

在需要高精度和隔离的应用中,例如电力监控、电机控制和一些医疗设备,下图所示的电路使用 AD7685 和 ADuM1402C 数字隔离器,提供了一个紧凑且高性能的解决方案。

多个 AD7685 以菊花链方式连接,以减少需要隔离的信号数量。需要注意的是,SCKOUT(AD7685 时钟的数据回读)与 DATA 信号具有非常短的偏斜。此偏斜是数字隔离器的通道间匹配传播延迟(t_PSKCD)。这允许串行接口以数字隔离器的最大速度运行(ADuM1402C 为 45 Mbps),否则这将受到数字隔离器传播延迟级联的限制。

完整的模拟链使用 ADR391 低压降基准电压和轨到轨 CMOS AD8618 放大器在 5 V 单电源上运行,同时提供真正的双极性输入范围。

上述就是关于AD7685模数芯片的布局及真正的 16 位隔离应用示例分析,希望对你在电子元器件选型、采购过程中有所帮助。