在为高速接口设计ESD箝位电路时,必须考虑布局因素,如封装选择、迹线布线等。困难的布线可能会导致设计人员在电路板迹线中使用通孔或短截线,这会对高速信号路径中的线路阻抗产生重大干扰。糟糕的封装选择会迫使设计人员以不相等的长度布线差分迹线,并在信号中增加偏斜。TI建议将差分迹线紧密耦合,以减少EMI干扰。

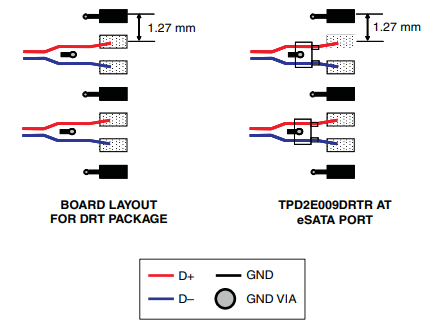

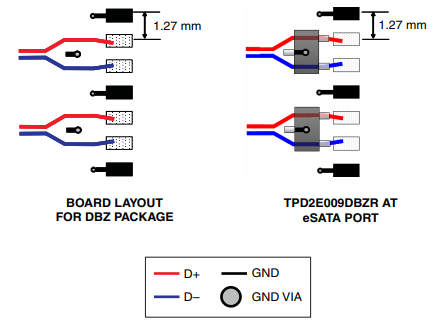

TPD2E009可以为高速差分端口(高达6-Gbps数据速率)提供系统级ESD保护。流通封装为电路板布线提供了灵活性,迹线宽度可达15密耳(0.38毫米)。下面两张图片显示了单个差分对的D+和D-线的电路板布局方案,该方案允许差分信号对在接触TPD2E009的ESD端口(引脚1和引脚2)后立即耦合在一起。

布局示例

eSATA连接器接口处的TPD2E009DRTR

eSATA连接器接口处的TPD2E009DBZR