LT1761 系列是 100mA 低压差线性稳压器,具有微功耗静态电流和关断功能。

该器件可在 300mV 的压差下提供 100mA 的输出电流。通过在参考引脚(REF)与地之间添加一个 0.01μF 的旁路电容,可以将输出电压噪声降低至 20μVRMS(在 10Hz 到 100kHz 的带宽范围内)。此外,参考旁路电容还能改善稳压器的瞬态响应,缩短负载瞬变时的稳定时间。

该器件的低静态工作电流为 20μA,在关断模式下可降至 1μA 以下。除了低静态电流外,LT1761 还集成了多种保护功能,使其非常适合用于电池供电系统。器件可防止反向输入和反向输出电压。

在电池备份应用中,当输入被拉低时,输出可能由备份电池维持电压,此时 LT1761-X 表现得如同在输出端串联了一个二极管,可防止反向电流流动。此外,在双电源供电应用中,如果稳压器负载返回至负电源,输出可以被拉低至地以下 20V,器件仍能正常启动和运行。

可调输出操作

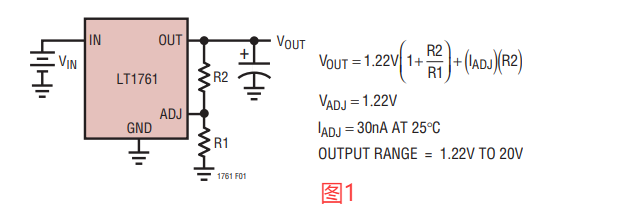

LT1761 的可调版本输出电压范围为 1.22V 至 20V。输出电压由两个外部电阻的比值设定,如图 1 所示。器件通过调节输出电压,使 ADJ 引脚电压维持在 1.22V(相对于地)。R1 中的电流等于 1.22V/R1,而 R2 中的电流等于 R1 中的电流加上 ADJ 引脚的偏置电流。ADJ 引脚的偏置电流在 25°C 时为 30nA,从 R2 流入 ADJ 引脚。

输出电压可通过图 1 中的公式计算。为了减小因 ADJ 引脚偏置电流引起的输出电压误差,R1 的阻值不应超过 250kΩ。请注意,在关断状态下,输出被关闭,分压器电流为零。

可调版本在测试和规格验证时,将 ADJ 引脚连接至 OUT 引脚,输出电压为 1.22V。对于大于 1.22V 的输出电压,其规格参数将按比例缩放,缩放比例为所需输出电压与 1.22V 的比值(Vout / 1.22V)。

例如,当输出电流从 1mA 变化到 100mA 时,负载调整率为典型值 -1mV(Vout = 1.22V)。当 Vout = 12V 时,负载调整率为:

(12V / 1.22V) × (-1mV) = -9.8mV

旁路电容与低噪声性能

通过在 OUT 引脚与 BYP 引脚之间添加一个旁路电容,可以进一步降低 LT1761 的输出电压噪声。推荐使用质量高、漏电流低的电容。该电容将旁路稳压器的参考电压,提供一个低频噪声极点。使用 0.01μF 的旁路电容可将输出电压噪声降低至最低 20μVRMS。

使用旁路电容的另一个好处是改善瞬态响应。在没有旁路电容的情况下,若输出电容为 10μF,当负载从 10mA 跳变至 100mA 时,输出将在 100μs 内稳定到最终值的 1% 以内。而添加 0.01μF 的旁路电容后,输出在同样的负载跳变下可保持在 1% 的误差范围内 。

然而,稳压器芯片的启动时间与旁路电容的大小成正比。使用 0.01μF 旁路电容和 10μF 输出电容时,启动时间将延长至约 15ms。