2023年2月16日,致力于亚太地区市场的领先半导体元器件分销商---大联大控股宣布,其旗下世平推出基于恩智浦(NXP)LPC5528芯片的3D打印机方案。

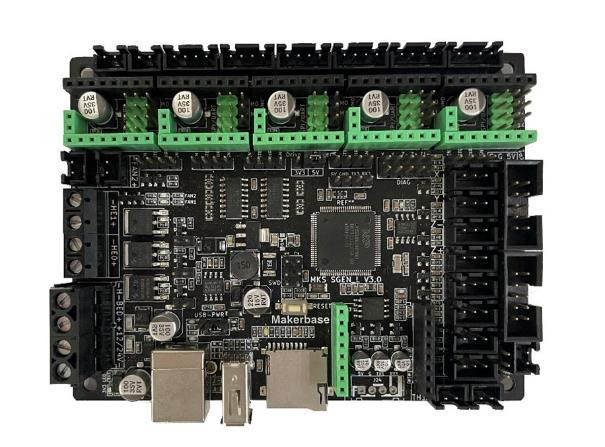

图示1-大联大世平基于NXP产品的3D打印机方案的展示板图

3D打印是目前最具生命力的快速成型技术之一,凭借着无需机械加工或任何模具就能直接从计算机图形数据中生成立体模型的特点,成为了产品创新竞争中强劲有力的工具。通过快速成型工艺,3D打印技术不仅在创客市场也掀起了一番热浪,也被广泛用于工业机械、医疗健康、汽车、建筑、消费等领域的生产设计中。由大联大世平基于NXP LPC5528芯片推出的3D打印机方案具有操作简单、工作稳定的特点,可帮助企业或个人创造者提高生产效率和经济效益。

图示2-大联大世平基于NXP产品的3D打印机方案的场景应用图

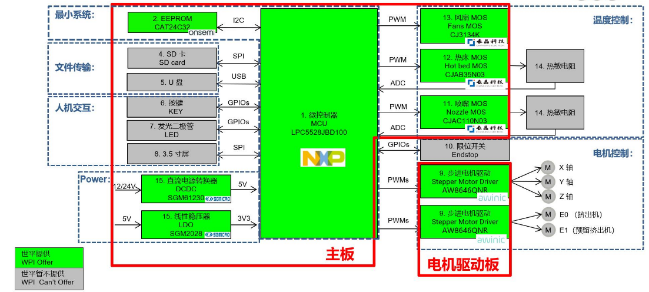

本方案核心主控采用的LPC5528是NXP旗下的一款主流MCU,其搭载Cortex-M33内核,主频可达150MHz。在内存选项上,该MCU拥有512KB片上Flash和256KB RAM。此外,LPC5528外设资源丰富,内嵌有多个Timer,多路PWM和多种通信接口,支持16位的ADC,可扩展多种功能。

在整体功能方面,本方案支持3.5寸触摸屏显示,分辨率为480*320。在打印资料传输中,方案支持以SD卡、U盘两种方式将文件传输至打印机,打印精度为±0.1mm。在电机设计上,方案支持5轴电机控制和静音驱动。当打印机结束工作时,将开启进入待机功能,以降低功耗。

图示3-大联大世平基于NXP产品的3D打印机方案的方块图

除了高性能的MCU外,大联大世平还为本方案提供了步进电机驱动、喷嘴MOS、风扇MOS、热床MOS、线性稳压器等多种产品。得益于这些产品的出色性能,本方案可为各种创新设计提供3D打印功能。

核心技术优势:

● LPC5528是一颗Cortex-M33内核的高性能MCU,主频达到150MHz,拥有512KB片上Flash,256KB RAM;

● 开发环境易于搭建,软件基于Marlin2.0固件开发;

● 操作简单,可直接替换其他同样接口主板使用。

方案规格:

● 3.5寸触摸屏显示,480*320分辨率;

● 支持SD卡、U盘传输资料给打印机;

● 支持5轴(X/Y/Z/E0(挤出机)/E1(预留挤出机))电机控制;

● 支持打完进入待机功能;

● 支持静音驱动;

● 打印精度±0.1mm;

● 电源输入:12/24V DC。