理论上,功分器又名功率分配器,是一种将一路输入信号能量分成两路或多路输出相等或不相等能量的器件,也可以将功率分配器输入端口作为输出端口,输出端口作为输入端口,作为合路器来使用。但是有一次有一个朋友使用一款一分二功分器作为合路器,将输出端的射频连接器当作为输入端口来使用,结果导致了器件被烧坏,几千人民币的一个小器件从此不能再工作,甚是可惜了。那么小编今天就带大家来探讨探讨功分器究竟能不能用作合路器。

实际上,我们中文翻译的功率分配器,有对应两个英文翻译:Power Divider 和Power Splitter,有的比较严谨的文章中,将两款器件对应翻译为功分器和分流器。

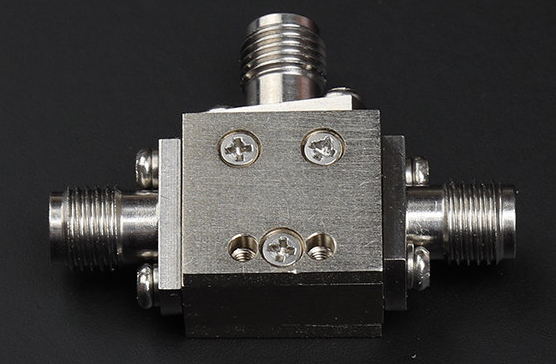

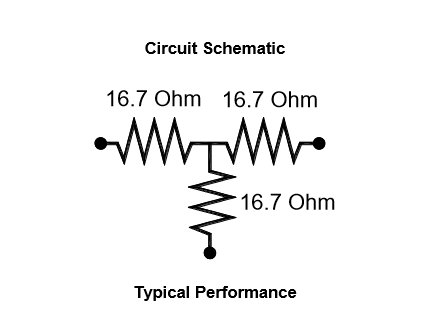

功分器(Power Divider)的结构原理图为:

在三端口网络中,其中任何一个端口作为输入端并匹配50欧姆负载,另外两个端口同时也均被匹配50欧姆负载的情况下,两两端口之间的插入损耗为6dB。该微波网络由放在三个传导触点的陶瓷基片的对称电阻膜组成,每点都被连接到同轴连接器的中心导体上。与利用频率限制技术的反射式和电桥式相比,电阻式在超宽带工作可提供幅度和相位几乎一致的良好匹配信号。该双向型器件完美应适用于独立输出信号应用,例如频率和功率同时检测。

1 宽带独立信号采样-用于系统同时测量一个信号的两个不同的特性,如频率和功率;

2将低功率信号分配给两个或多个天线;

3需要精确跟踪基准信号的实验室测量;

4电阻式功率分配器由于是双向的,因此可以用作功率合成器。但是因为3;1失配的情况存在,所以不适于比率系统或水准回路;

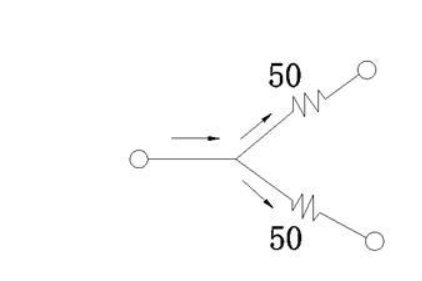

分流器(Power Splitter)的结构原理如下:

该器件可以提供完美的幅度跟踪和超低驻波输出,适用于:

1双通道插入损耗测量系统,其中电阻分流器提供参考和信号信道;

2已知功率计典型值,通过比例或水准来提供校准输出的信号功率精密测量;

3用于对信号源电平提供采样输出测量,如单通道衰减测量。

4 由于该器件为非双向型,所以不能用于功率合成,只适用用于比率系统或水准

由此可见,power divider是可以用做合路器的,而power splitter不可以。