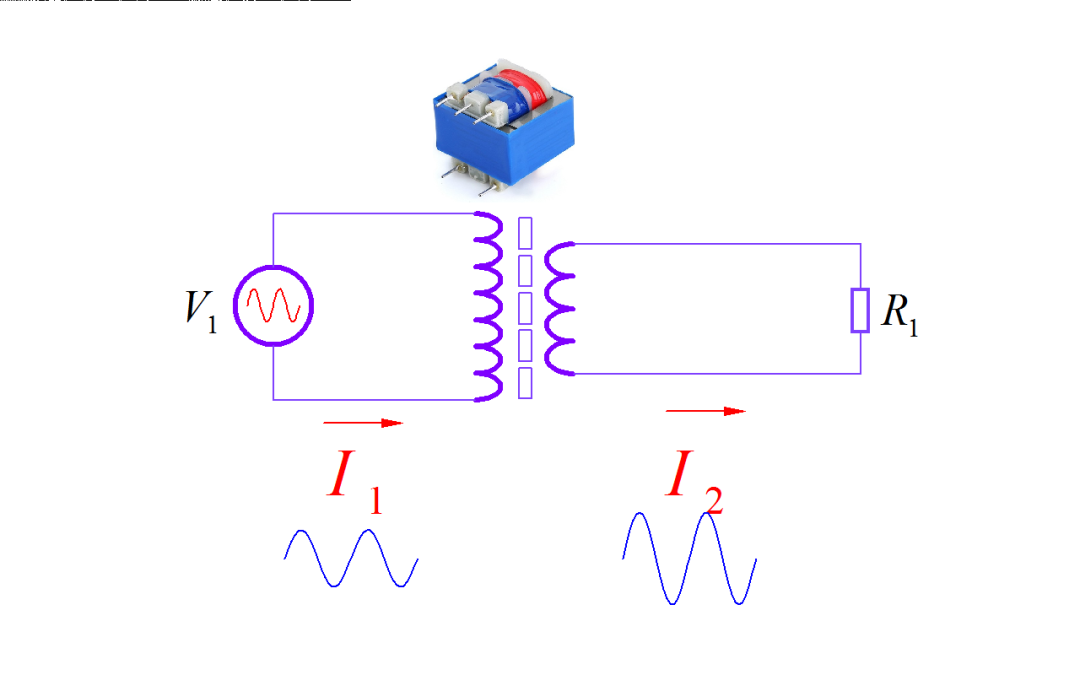

对于一个变压器,它的原边和副边绕制在同一磁路上,在原边施加正弦交流电,副边连接负载。两边的电压比值等于匝数之比。根据功率守恒,负载电流与匝数成反比。波形都是正弦波,只是幅值有所不同。

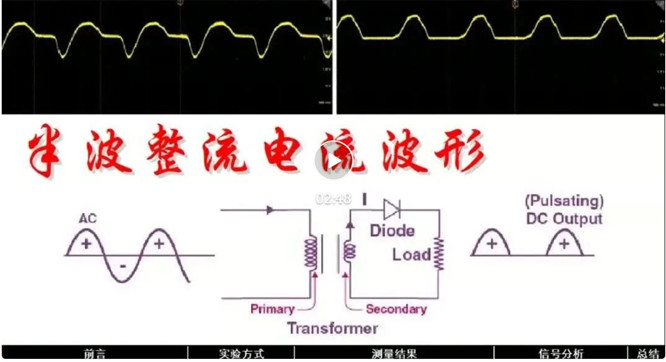

整流波形

一、前言

对于一个变压器,它的原边和副边绕制在同一磁路上,在原边施加正弦交流电,副边连接负载。两边的电压比值等于匝数之比。根据功率守恒,负载电流与匝数成反比。波形都是正弦波,只是幅值有所不同。

下面有一个问题,如果在副边增加一个二极管,对输出电流进行半波整流,副边的电流形成半波整流电压波形。那么原边的电流波形将会变成什么模样呢?下面我们先通实验来测试一下。

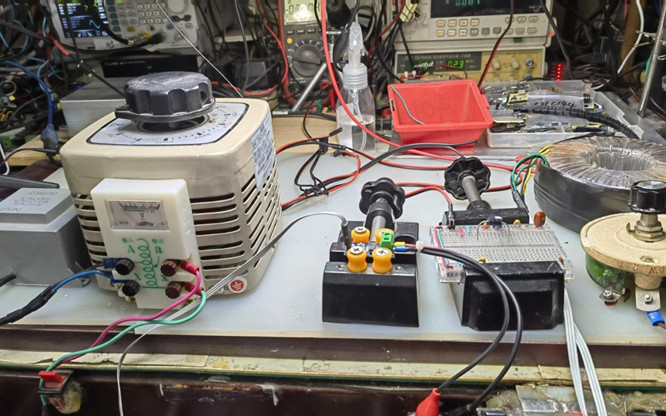

二、实验方式

这里给出了测试整流电流波形的器件。原边的交流电是由隔离变压器以及自耦变压器提供。利用了一个环形变压器副边两个绕组作为实验中输入输出绕组,原副边匝数比大约为 2 比 1。采用一个 20 欧姆可调电阻作为负载, 使用一个大功率整流二极管对复变电压进行整流。

使用一个半导体霍尔模块测量绕组中的电流。下面利用这些器件测量半波整流情况下输入输出电流波形。

▲ 图1.2.1 实验测试器材

三、测量结果

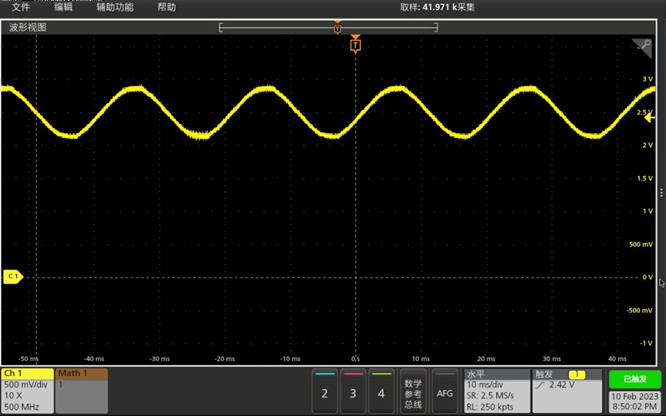

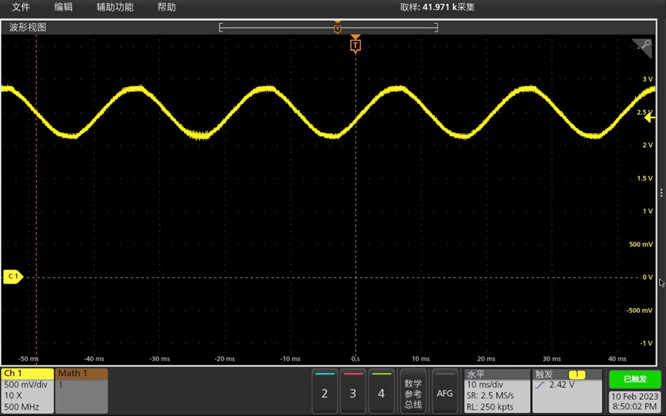

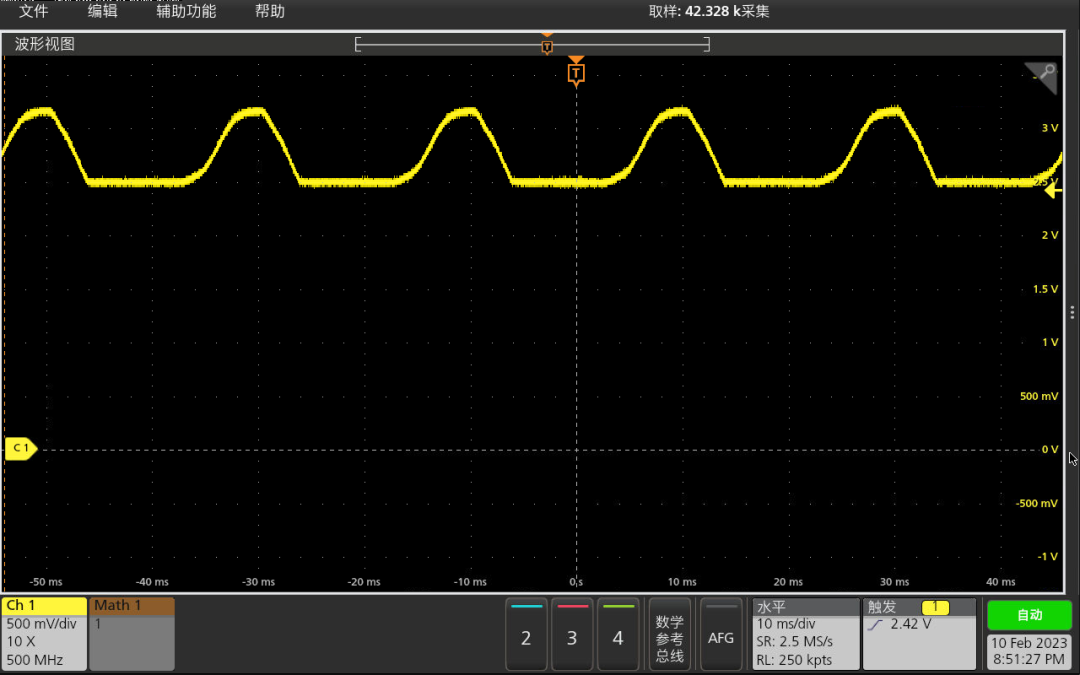

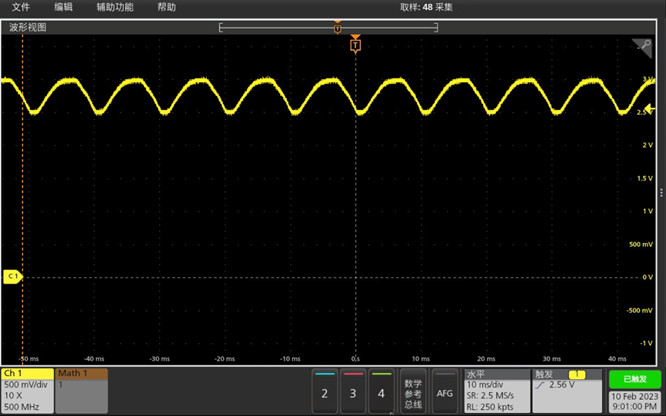

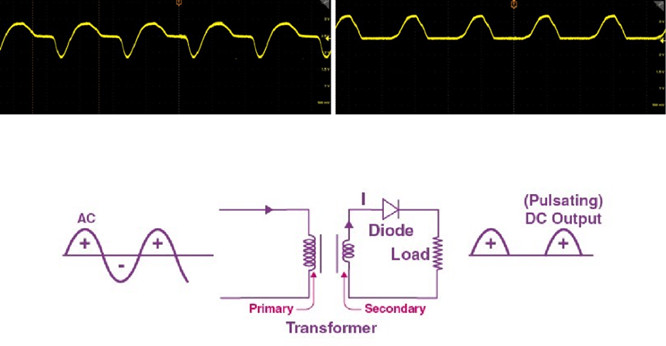

这是在副边为纯电阻的情况下,原边的电流波形。可以看到它是一个正弦波。需要注意的是,电流霍尔传感器输出零点电压为2.5V。在副边电阻上串联半波整流二极管。这是测量到副边的半波整流电流信号波形。可以看到它是半波直流脉动信号。这是变压器原边电流信号, 它的波形与输出电流信号波形不同, 是一个纯交流信号。如果在副边使用整流桥电路, 可以测量到负载上的全波整流信号。原边的电流波形则恢复到正弦信号。那么问题来了, 为什么副边半波整流时,原边的电流信号变成了这个样子呢?

▲ 图1.1 电阻负载电流波形

▲ 半波整流电流波形

▲ 半波整流原边电流波形

▲ 图1.4 全波整流副边电流波形

▲ 图1.5 全波整流原边电流波形

四、信号分析

由于半波整流在实际应用中比较少,其缺点也比较多。整流呈现非线性, 对于输入输出的电流、电压信号建模分析比较困难,所以大部分情况都是分析输入输出电压波形,对于输入电流波形很少分析。所以观察到的电流波形, 之所以为什么是这样, 我现在还没有一个比较简便明确的答案, 不知道谁能够给出解释。

▲ 图1.4.1 半波整流输入输出电流波形

总结

本文实验分析了普通小型变压器在半波整流负载下, 输入输出电流波形。尚缺乏对于这个波形的理论分析。