智能手机功能愈发强大,设计起来也愈发复杂,但尺寸通常不会增加。设计人员需要将新的功能加入到与前几代产品大小一样的空间里。在本文中,我们将探讨一些设计技巧,帮助智能手机设计人员通过创造性的方式腾出更多空间。

如今的智能手机,虽然个头没有变大,但所含功能却越来越丰富。为了适应目前的新功能,摄像头、传感器和组件的数量在不断增加,可用的布局空间越来越小。天线的使用区域同样如此。

尤其是 5G 新无线电 (NR) 频段需要更多的天线功能,这一状况愈发明显。所幸,设计人员可以使用新的组件和应用技术来应对空间受限的挑战。使用天线复用器就是其中一个设计方案。

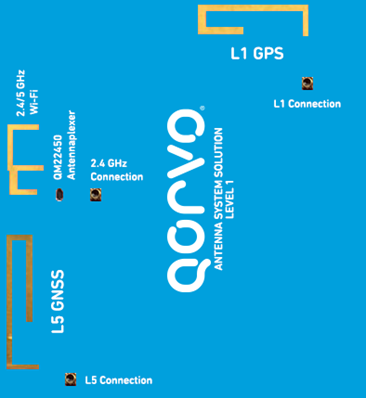

利用天线复用器,设计工程师可以压缩天线区域,从而节约空间。我们举例来说明两种设计场景——在设计 GPS 和 Wi-Fi 天线布局时一种使用 QM28005 天线复用器,一种不使用。在图 1 中,我们看到一个普通的 GPS、GNSS(全球导航卫星系统)和 Wi-Fi 天线布局设计。我们将此设计布局称为场景 1。

图 1:普通 GPS、GNSS 和 Wi-Fi (2.4/5 GHz) 天线布局——设计场景 1。

如图所示,为了能容纳所有与这些频段相关的天线,该设计占用了大量的印刷电路板空间。

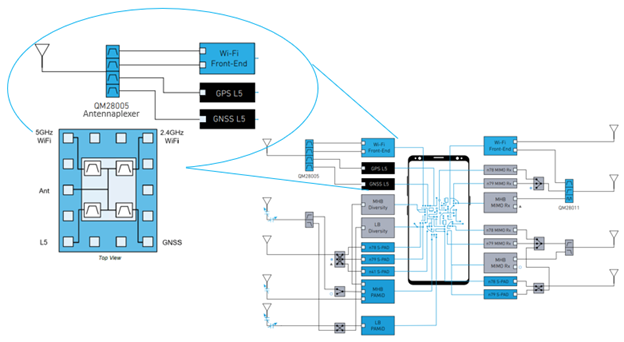

为了整合这些频段,我们使用了QM28005 天线复用器。QM28005 是一个紧凑型滤波器模块,旨在满足频段外衰减的严格要求,同时还对 L5 GPS、L1、2.4G Wi-Fi 和 5G Wi-Fi 的插入损耗进行了优化。参见图 2。

图 2:QM28005 的功能框图。

GPS 和 Wi-Fi 天线的设计使单根天线 (ANT) 的几何结构可以辐射 L1、L5 和 2.4/5G Wi-Fi 频段,以便与 QM28005 连接。图 3 说明了该天线的设计。

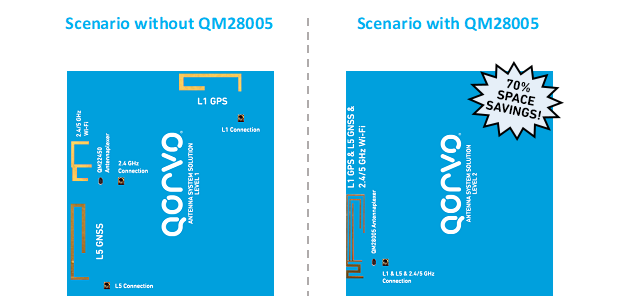

我们来比较一下使用和不使用QM28005 天线复用器的 GPS 和 Wi-Fi 天线设计。在图 3 中,使用 QM28005 天线复用器有利于设计时将 GPS 和 Wi-Fi 频段压缩到同一区域——如图右侧所示。而左侧——没有使用 QM28005 天线复用器的天线设计就做不到这一点。

图 3:使用和不使用 QM28005 的 GPS 和 Wi-Fi 天线布局设计

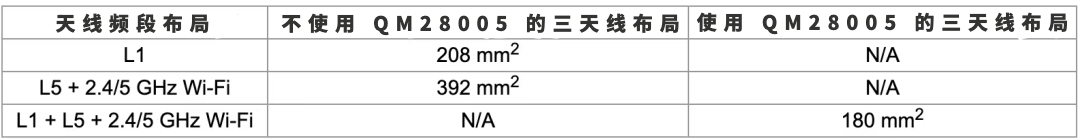

表 1:使用 QM28005 天线复用器的布局尺寸比较。

对比两个天线设计场景,我们可以看到,与不使用天线复用器的600mm2 天线区域相比,使用 QM28005 的 180mm2 解决方案,其空间节约了 70% 以上。

此外,使用 QM28005 天线复用器后,之前与所有天线连接的组件可以降低 BOM 成本,这是因为与单根天线连接所需的组件数量要比与之前单独的多根天线连接的数量有所减少。

来源:Nick Fields,Qorvo