ADF4382A是一款高性能、超低抖动、分数N锁相环(PLL),带有集成压控振荡器(VCO),非常适合5G应用或数据转换器时钟应用的本地振荡器(LO)生成。高性能PLL的品质因数为-239 dBc/Hz,低1/f噪声,整数模式下的高PFD频率为625 MHz,可以实现超低带内噪声和集成抖动。ADF4382A可以产生11.5 GHz至21 GHz基本倍频程范围内的频率,从而消除了对亚谐波滤波器的需求。ADF4382A上的除2和除4输出分频器分别允许产生5.75 GHz至10.5 GHz和2.875 GHz至5.25 GHz的频率。

对于多个数据转换器时钟应用,ADF4382A通过在PLL反馈环路中包含输出分频器,自动将其输出与输入参考边沿对齐。对于需要确定性延迟或延迟调整能力的应用,提供了一个分辨率<1ps的可编程输出延迟参考。跨多个设备和超温输出延迟匹配的参考允许可预测和精确的多芯片时钟和系统参考(SYSREF)对齐。

ADF4382A框图的简单性通过简化的串行外围接口(SPI)寄存器映射、可重复的多芯片时钟对齐以及允许片外SYSREF生成来限制不需要的时钟杂散,从而缩短了开发时间。

规格参数

最大输入频率:4.5 GHz

最小输入频率:10 MHz

输出频率范围:11.5 GHz to 21 GHz

电源电压-最大:5.25 V

电源电压-最小:3.15 V

最小工作温度:- 40 C

最大工作温度:+ 105 C

安装风格:SMD/SMT

封装 / 箱体:LGA-48

封装:Tray

商标:Analog Devices

开发套件:EVAL-ADF4382A

输入电平:LVDS

湿度敏感性:Yes

工作电源电流:340 mA

工作电源电压:3.15 V to 5.25 V

输出电平:PLL

特性

•基本输出频率范围:11.5 GHz至21 GHz

•除以2输出频率范围:5.75 GHz至10.5 GHz

•除以4输出频率范围:2.875 GHz至5.25 GHz

•20 GHz时的集成RMS抖动=20 fs(集成带宽:100 Hz至100 MHz)

•20 GHz时的集成RMS抖动=31 fs(ADC SNR方法)

•VCO自动校准时间<100μs

•相位噪声基底:20 GHz时为-156 dBc/Hz

•PLL规格

•−239 dBc/Hz:归一化带内相位本底噪声

•−287 dBc/Hz:归一化1/f相位噪声基底

•625 MHz最大相位/频率检测器输入频率

•4.5 GHz参考输入频率

•典型杂散fPFD:-90 dBc

应用

高性能数据转换器时钟

无线基础设施(MC-GSM、5G、6G)

测试和测量

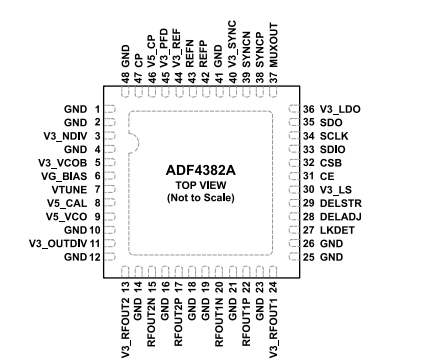

引脚图