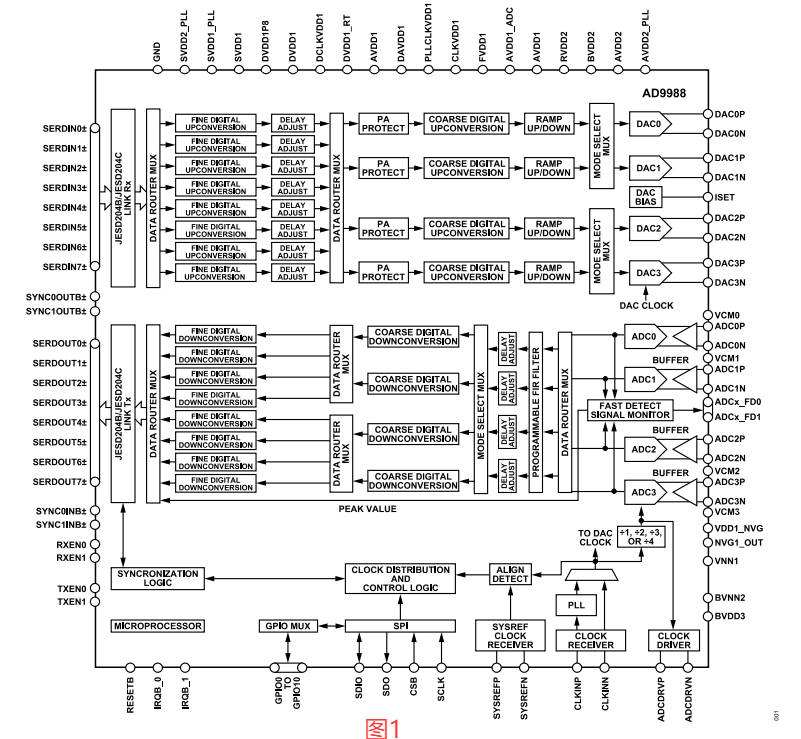

AD9988是一款高度集成的混合信号直接射频采样收发器,提供四个发射器和四个接收器(4T4R)以及数字信号处理(DSP)功能(参见图1)。该器件旨在满足无线基础设施应用(如多频段宏基站5G和毫米波5G基站无线电)所要求的高性能、可配置性和低功耗。AD9988还提供支持时分双工(TDD)和频分双工(FDD)技术的功能。

接收路径由四个流水线式12位、4吉采样率的射频模数转换器(ADC)内核组成。发射路径由四个16位、12吉采样率最大采样率的射频数模转换器(DAC)内核组成。接收和发射路径均设计为对高达7.5 GHz的信号进行采样和合成,最大瞬时带宽高达1.2 GHz,采样分辨率为16位。该器件还支持12位和8位等较低分辨率,以降低JESD204B/C链路的比特率,适用于不需要16位分辨率所提供的更高动态范围的应用。16位分辨率的宽瞬时带宽允许芯片在单个器件内支持多个载波频段和单个宽频段。与传统的中频(IF)接收器相比,直接射频转换架构放宽了对射频滤波器的要求。该器件还集成了若干辅助功能,如快速检测和信号监控、可编程有限脉冲响应(FIR)滤波器、发射机下游功率放大器保护以及通用输入/输出(GPIO)控制。

DAC和ADC内核使用的采样时钟源自外部时钟源或片上时钟乘法器,该乘法器由整数PLL电路和压控振荡器(VCO)组成。

该器件具有八个发射 lanes 和八个接收 lanes,每个 lane 支持高达24.75 Gbps的JESD204C或高达15.5 Gbps的JESD204B,作为单链路或双链路。根据JESD204B/C子类别1,支持多芯片同步和确定性延迟。JESD204B/C接口支持广泛的设置,具体取决于定制应用专用集成电路(ASIC)或现场可编程门阵列(FPGA)的接口带宽要求。有关器件功能和操作的更多信息,请参考器件用户指南UG-1578。

AD9988具有片上热管理单元(TMU),可用于测量芯片结温,作为热管理解决方案的一部分,以确保系统在运行期间的热稳定性。该器件通过支持三线SPI通信的标准四线串行端口接口(SPI)进行配置。器件还包括一套全面的断电模式,以在系统停机期间最小化功耗。AD9988采用15 mm×15 mm、324球、热增强型球栅阵列(BGA-ED)封装。