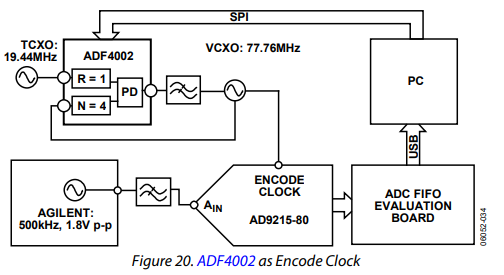

图20显示了ADF4002与VCXO配合,为高速模数转换器(ADC)提供编码时钟。该转换器采用AD9215-80,一款12位转换器,在本应用中接受80 MHz的编码时钟。为实现稳定的低抖动时钟,使用77.76 MHz窄带VCXO。本设计假设参考时钟为19.44 MHz。

为最大限度降低ADF4002的相位噪声贡献,采用最小倍频系数4。因此,参考分频器(R)编程为1,N分频器编程为4。ADF4002的电荷泵输出(引脚2)驱动环路滤波器。环路滤波器带宽经过优化,以获得最佳的均方根抖动,这是信号噪声比(SNR)的关键因素。带宽过窄会使载波频率附近的VCXO噪声占主导地位;带宽过宽则会使ADF4002在VCXO噪声低于ADF4002噪声的频率偏移处占主导地位。因此,环路滤波器的最佳带宽对应VCXO噪声与ADF4002带内噪声的交点。

环路滤波器的设计使用ADIsimPLL(3.0版)。测得的均方根抖动为1.2 ps。该抖动水平低于此转换器要求的理论最小允许6 ps均方根抖动。

图20所示的设置使用ADF4002、AD9215和评估板,可快速有效地确定转换器与编码时钟的兼容性。SPI®接口用于控制ADF4002,USB接口帮助控制AD9215 PC板。控制器板发送回操作信息至PC,PC通过ADC分析仪提供ADC的所有转换结果。