电流限制(Current Limit)

当检测电阻 Rs(VIN 到 SENSE)两端的电压达到 55mV 时,电流限制阈值被触发。在电流限制状态下,GATE 引脚的电压被控制,以限制 MOSFET Q1 中的电流。当电流限制电路激活时,故障定时器也开始工作。如果在故障超时结束前,负载电流降至电流限制阈值以下,LM5069 将恢复正常工作。为确保正常工作,Rs 电阻的值不得超过 100mΩ。

断路器(Circuit Breaker)

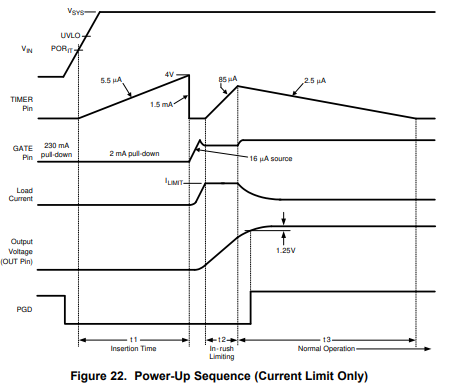

如果负载电流迅速上升(例如负载短路),在电流限制控制环路响应之前,检测电阻 Rs 中的电流可能会超过电流限制阈值。如果电流超过电流限制阈值的两倍(即 105mV/Rs),Q1 将通过 GATE 引脚的 230mA 下拉电流迅速关闭,同时开始故障超时计时。当 Rs 两端电压降至 105mV 以下时,GATE 引脚的 230mA 下拉电流关闭,Q1 的栅极电压将由电流限制或功率限制功能决定。如果在电流限制或功率限制条件解除之前,TIMER 引脚电压达到 4V,Q1 将通过 GATE 引脚的 2mA 下拉电流关闭。

功率限制(Power Limit)

LM5069 的一个重要特性是 MOSFET 功率限制功能。该功能可用于将 MOSFET Q1 的最大功耗保持在其安全工作区(SOA)额定值内。LM5069 通过监测 Q1 的漏源电压(SENSE 到 OUT)和通过检测电阻(VIN 到 SENSE)的漏电流来计算其功耗。电流与电压的乘积将与通过 PWR 引脚电阻设定的功率限制阈值进行比较。如果功耗达到限制阈值,GATE 电压将被调节,以减少 Q1 中的电流。当功率限制电路激活时,故障定时器也开始工作。

欠压锁定(UVLO)

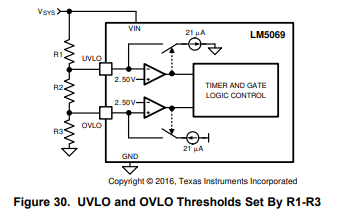

当输入电源电压(Vsys)处于可编程的欠压锁定(UVLO)和过压锁定(OVLO)设定范围内时,串联 MOSFET(Q1)被启用。通常,UVLO 阈值通过电阻分压器(R1-R3)设定,如图30所示。当 Vsys 低于 UVLO 阈值时,UVLO 引脚内部的 21μA 电流源启用,OVLO 引脚的电流源关闭,Q1 通过 GATE 引脚的 2mA 下拉电流保持关闭状态。

随着 Vsys 升高,UVLO 引脚电压超过 2.5V 时,UVLO 引脚的 21μA 电流源关闭,UVLO 引脚电压上升,为该阈值提供迟滞。当 UVLO 引脚电压高于 2.5V 且插入延时已结束时,Q1 将通过 GATE 引脚的 16μA 电流源开启(见图22)。

最小的 UVLO 阈值可通过将 UVLO 引脚连接到 VIN 来设定。在这种情况下,当 VIN 电压达到上电复位阈值(POR)时,Q1 被启用。

过压锁定(OVLO)

当输入电源电压(Vsys)处于设定范围内时,串联 MOSFET(Q1)被启用。当 OVLO 引脚电压高于 2.5V 时,Q1 将通过 GATE 引脚的 2mA 下拉电流关闭,切断对负载的供电。当 OVLO 引脚电压高于 2.5V 时,OVLO 引脚内部的 21μA 电流源开启,提高 OVLO 引脚电压,以提供阈值迟滞。当 Vsys 降低到 OVLO 阈值以下时,Q1 被重新启用。

电源正常引脚(Power Good Pin)

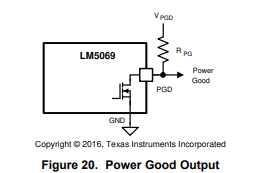

在启动过程中,电源正常引脚(PGD)保持高电平,直到 VIN 电压升高至约 5V。随后 PGD 变为低电平,并在 VIN 继续升高时保持低电平。当 OUT 引脚电压升高至距离 SENSE 引脚电压 1.25V 以内(即 Vos < 1.25V)时,PGD 变为高电平。如果 Q1 的 Vos 升高至 2.5V 以上,PGD 将变为低电平。

PGD 引脚需要外接上拉电阻,如图20所示。上拉电压(VpeD)最高可达 80V。

如果浪涌限制状态持续存在,GATE 引脚将被 2 mA 下拉电流拉低。随后,GATE 引脚将保持低电平,直到满足以下任一条件:启动上电序列(LM5069-1),或重启序列结束(LM5069-2)。如果系统输入电压低于 UVLO 阈值,或高于 OVLO 阈值,GATE 引脚也会被 2 mA 下拉电流拉低,从而关闭 Q1。