片内 VCO

AD9522 内置一只片内 VCO,其频率覆盖范围见表 2。校准程序可确保 VCO 的工作电压针对所需频率居中。

在首次配置 VCO 环路,以及每次更改标称 VCO 频率时,都必须执行一次 VCO 校准;但一旦完成校准,VCO 便具备足够的调节范围,可在温度和电压极端条件下保持锁定,无需再次校准。

为覆盖 VCO 的宽调谐范围,器件内部划分了多个调谐区段。校准过程会自动选择对应所需频率的区段。

片内 VCO 由一只片内低压差(LDO)线性稳压器供电。该 LDO 可在一定程度上隔离 VCO,使其不受电源电压波动影响。BYPASS 引脚需通过一只 220 nF 电容接地,以保证 LDO 稳定工作。此 LDO 采用与 ADI anyCAP® 系列稳压器相同的技术,对电容类型不敏感。不允许利用 BYPASS 引脚向外供电。

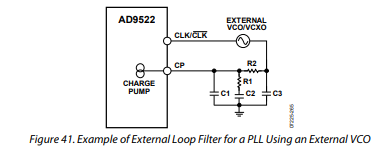

若使用外部 VCO/VCXO,请将 BYPASS 和 LF 引脚悬空,配置见图 41。

数字锁定检测(DLD)

通过在各引脚的多路复用器中选择正确输出,即可在 LD、STATUS 和 REFMON 引脚获得 DLD 功能。

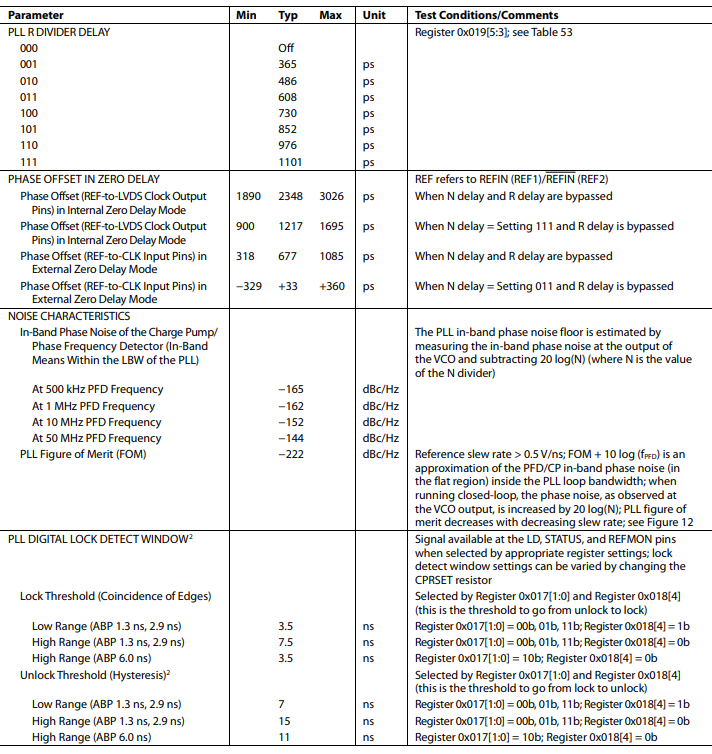

数字锁定检测电路的工作原理:当 PFD 输入上升沿之间的时间差小于设定值(锁定门限)时,指示“锁定”;当该时间差大于另一设定值(失锁门限)时,指示“失锁”。失锁门限宽于锁定门限,从而允许在锁定窗口外存在一定相位误差,而不会使锁定指示产生抖动。

锁定检测窗口的时长取决于 CPRSET 电阻值,以及三个寄存器位:

数字锁定检测窗口位(寄存器 0x018[4])

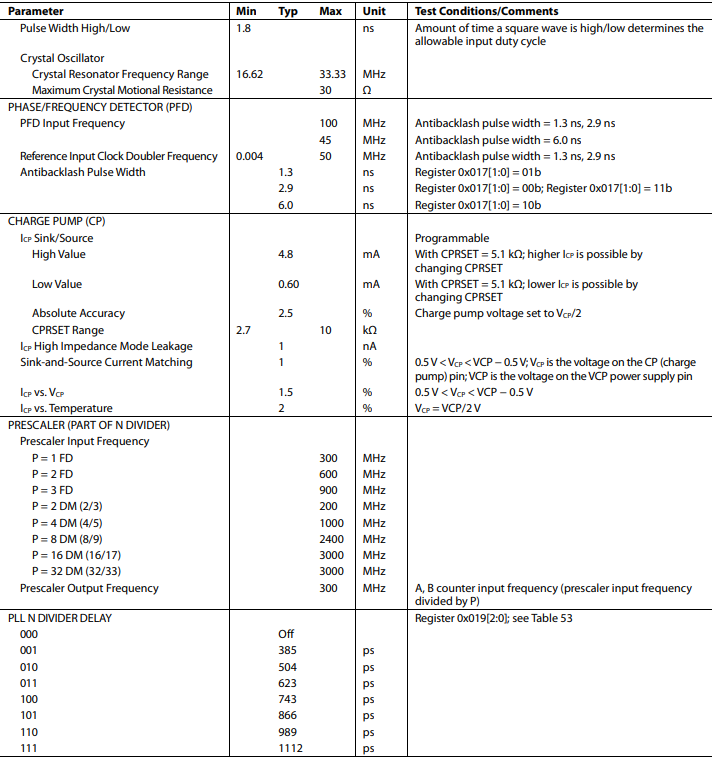

反回差脉冲宽度位(寄存器 0x017[1:0],见表 2)

锁定检测计数器(寄存器 0x018[6:5])

表 2 中的锁定/失锁数值基于 CPRSET = 5.11 kΩ;若将 CPRSET 加倍至 10 kΩ,则表中数值亦相应加倍。

只有当连续若干个 PFD 周期的时间差均小于锁定门限时,才会给出锁定指示;而一旦后续某个周期的时间差大于失锁门限,锁定指示即被撤销。连续周期数可通过寄存器 0x018[6:5] 设置。

注意:在某些环路带宽极低(<500 Hz)且相位裕量很大的情况下,DLD 在捕获过程中可能出现抖动,导致 AD9522 自动反复进出保持状态。为避免此问题,建议在 LD 引脚对地预留一只电容,以便使用“电流源数字锁定检测(CSDLD)”模式。

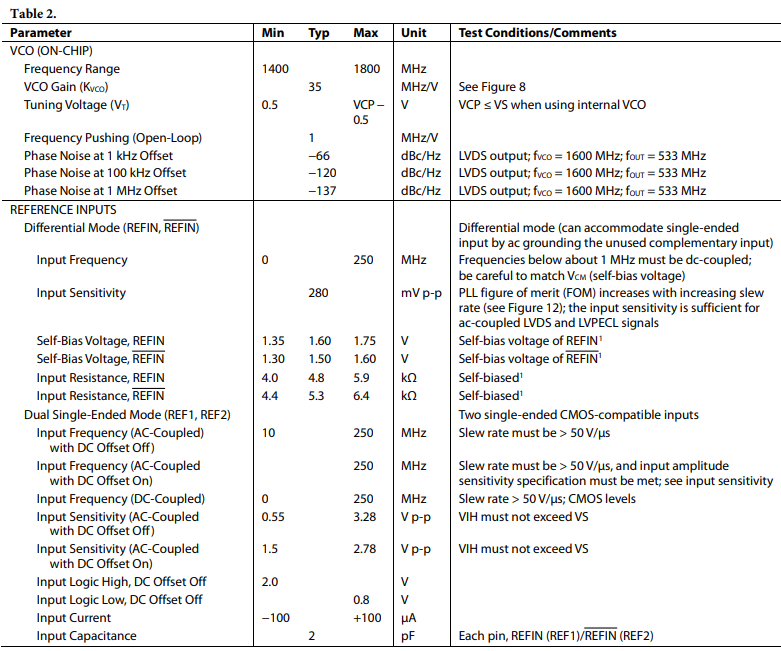

表2