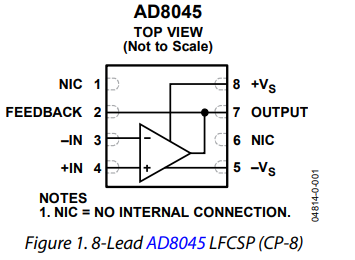

低失真引脚排列

AD8045 的 LFCSP 封装采用了 Analog Devices 的新型低失真引脚排列。这种新引脚排列相比传统引脚排列有两个优势:

改善了二次谐波失真性能,这是通过物理上分离非反相输入引脚与负电源引脚实现的;

简化了布局设计,得益于专用的反馈引脚,增益设定电阻可方便地布回反相输入引脚,从而实现紧凑布局,有助于减小寄生参数并提高稳定性。

传统的 SOIC 引脚排列也稍作修改,增加了一个专用反馈引脚。引脚 1 原本是一个空引脚(NC),现在被用作专用反馈引脚。新引脚排列有助于减少寄生参数并简化 PCB 布局。

对于使用传统 SOIC 引脚排列的现有应用,仍可充分利用 AD8045 的卓越性能。如果 SOIC 封装放置在接地层或其他金属走线上,可能需要使用电绝缘垫片,详情可参考数据手册中的“裸露焊盘”部分。

在现有设计中,如果引脚 1 被接地或连接到其他电位,只需将 AD8045 的引脚 1 抬起或清除该引脚焊盘上的电位即可。设计者并不一定要使用专用反馈引脚来为 AD8045 提供反馈,仍可通过输出引脚将反馈信号送至反相输入端。

高速 ADC 驱动器

AD8045 作为 ADC 驱动器使用时,其失真性能可与变压器相媲美。

许多 ADC 应用要求模拟输入信号为直流耦合,并在宽频率范围内工作。在这些要求下,运算放大器是连接 ADC 的理想接口。运放接口可对输入信号进行放大和电平移位,使其适配 ADC 的输入范围。与变压器不同,运算放大器可在从直流开始的宽频率范围内工作。

图 67 展示了 AD8045 作为 AD9244(14 位、65 MSPS ADC)的直流耦合差分驱动器。两个放大器分别配置为非反相和反相模式。两个放大器的噪声增益均设为 +2,以获得更好的带宽匹配。反相放大器增益为 -1,非反相放大器增益为 +2。非反相输入端被除以 2,以使其输出归一化,与反相输出相等。

该直流耦合差分驱动器最适合于 ±5V 供电、要求最佳失真性能且输入信号为地参考的应用。

AD8045 的输出以 AD9244 的 2.5V 共模电压为中心。AD9244 提供的共模参考电压通过 OP27 缓冲和滤波后,馈入用于电平移位的非反相电阻网络。

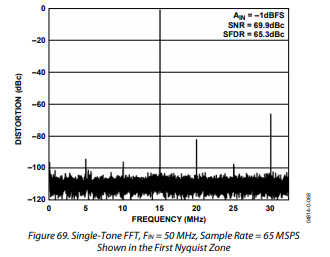

图 68 显示了无杂散动态范围(SFDR)性能,图 69 展示了 50 MHz 单音信号的 FFT 性能。