奇偶校验错误检测

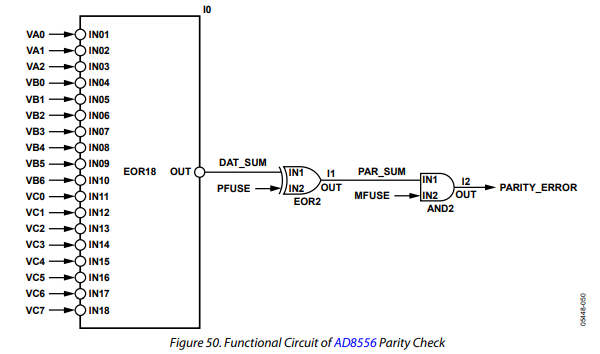

AD8556 利用奇偶校验来判断已写入的数据是否有效,或判断非易失存储器中的数据是否已损坏。图 50 给出了芯片内部实现该功能的原理图。

VA0~VA2:第二级增益的 3 位控制信号

VB0~VB6:第一级增益的 7 位控制信号

VC0~VC7:输出失调的 8 位控制信号

PFUSE:来自“奇偶熔丝”的信号

MFUSE:来自“主熔丝”的信号

二输入与门(Cell AND2)的作用是:当主熔丝未烧断(MFUSE = 0)时,忽略奇偶电路的输出(PAR_SUM),此时 PARITY_ERROR 被强制为 0。例如在仿真模式下,奇偶校验被禁用。只有在主熔丝烧断(即芯片完成编程)后,PAR_SUM 才会被送到 PARITY_ERROR。

若 PARITY_ERROR = 0:芯片按已编程的增益/失调正常工作

若 PARITY_ERROR = 1:检测到奇偶错误,输出 VOUT 被拉至 VSS(地)

18 位数据信号(VA0~VA2、VB0~VB6、VC0~VC7)送入一个 18 输入异或门(Cell EOR18),其输出为 DAT_SUM。

若 18 位数据中“1”的个数为偶数 → DAT_SUM = 0

若为奇数 → DAT_SUM = 1(示例见表 13)

完成第二级增益、第一级增益和输出失调的编程后,计算 DAT_SUM 并将其值写入“奇偶位”:

如果 DAT_SUM = 0,则不烧断奇偶熔丝,使 PFUSE = 0

如果 DAT_SUM = 1,则烧断奇偶熔丝,使 PFUSE = 1

烧断奇偶熔丝的指令码:

1000 0000 0001 10 11 10 0000 0100 0111 1111 1110

奇偶位设置完毕后,可烧断主熔丝以禁止再次编程,指令码:

1000 0000 0001 10 11 10 0000 0001 0111 1111 1110

信号 PAR_SUM 来自二输入异或门(Cell EOR2,输入为 DAT_SUM 与 PFUSE)。主熔丝烧断后,PARITY_ERROR = PAR_SUM。

PARITY_ERROR = 0:无校验错误,芯片按设定参数正常工作

PARITY_ERROR = 1:校验错误,VOUT 被强制连接到 VSS

如有型号采购及选型需求,可直接联系兆亿微波电子元件商城。