AD8351差分放大器的传输线效应

杂散传输线电容与封装寄生参数组合后,可能在高频下形成谐振电路,导致增益出现尖峰。因此,连接输入/输出网络的传输线必须设计成最小杂散电容。AD8351 的单端输出源阻抗被动态设定为标称 75 Ω;若负载端需要匹配,则应把输出传输线的特性阻抗设计为 75 Ω。在许多情况下,最终负载阻抗可能较高(>1 kΩ),此时建议按图 45 的方式设计 PCB:走线宽度做得较窄(约 5 mil),并把下方及相邻的地平面远离信号线,以减小电容。

通常,驱动源阻抗低于器件输入阻抗,因此需加终端电阻防止输入反射。传输线必须在“低阻抗区”内保持正确的特性阻抗;而在终端电阻与器件引脚之间的“高阻抗区”,信号线下方及附近不得放置地平面。为进一步抑制由键合线与周围板级寄生电容引起的谐振,可在器件输入引脚端串小电阻“降 Q”。一般 25 Ω、0402 尺寸的串联电阻即可在几乎不牺牲交流性能的前提下,有效降低输入系统的 Q 值。

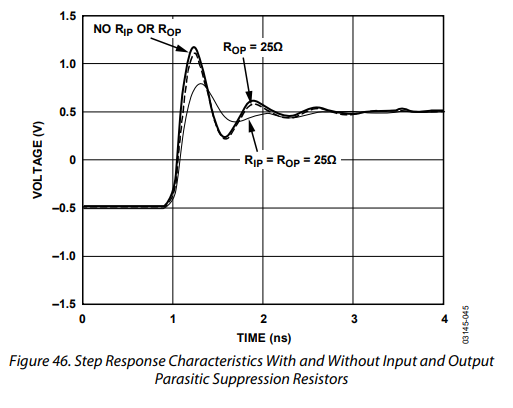

图 46 展示了在输入、输出端串接小电阻(Rip、Rop)带来的好处:可显著削弱因板级寄生参数引起的过冲与下冲。

如有型号采购及选型需求,可直接联系兆亿微波电子元件商城。