AD9260 采用一种全新的模数转换器架构,将 Σ-Δ(sigma-delta)技术与高速流水线型 ADC 相结合。该拓扑使 AD9260 在仅 8 倍过采样比的条件下,兼具 Σ-Δ 转换器的高动态范围与 1.25 MHz 的宽输入信号带宽。

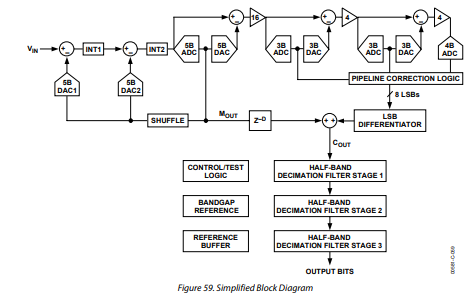

图 59 给出了 AD9260 的框图。差分模拟输入首先送入一个二阶、多位 Σ-Δ 调制器。该调制器内置 5 位 Flash 量化器与 5 位反馈。同时,一个 12 位流水线 ADC 对输入信号进行更高精度的量化。特殊的数字调制环路将 12 位流水线 ADC 的输出与经延迟的 5 位 Flash 输出相结合,等效实现“二阶环路 + 12 位量化器 + 12 位反馈”的响应。二阶环路配合多位反馈带来固有稳定性,使 AD9260 不会出现高阶单比特 Σ-Δ 调制器常见的空闲音或满量程异常现象。

12 位调制器的输出送入数字抽取滤波器。MODE 引脚的电平决定滤波器的工作模式:用户可选择不抽取(时钟速率输出),或 2×、4×、8× 抽取。

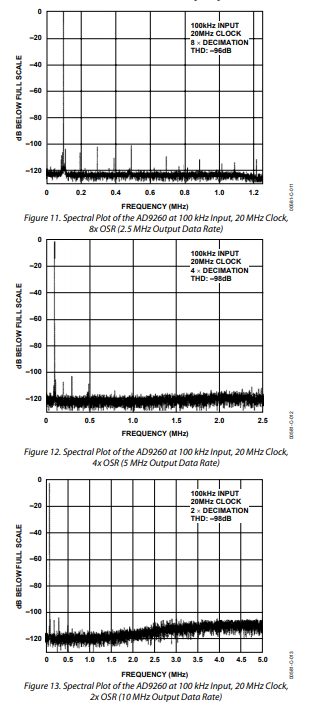

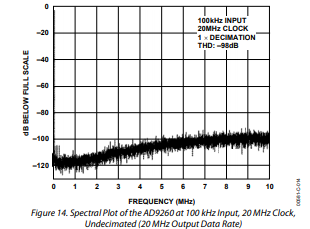

图 11~图 14 给出了在 100 kHz 满幅输入、20 MHz 时钟下的输出频谱。未抽取输出的频谱可清晰看到量化噪声的二阶整形特性:频率高于 1.25 MHz 后噪声迅速上升。

片内抽取滤波器对 1.25 MHz~18.75 MHz 之间的杂散信号提供优异的阻带抑制,大幅放宽模拟输入端抗混叠滤波器的设计要求。抽取滤波器采用对称 FIR 结构,具有线性相位响应和极佳的通带平坦度。

AD9260 的数字输出驱动寄存器配有 READ 和 CHIP SELECT 引脚,便于接口连接。数字电源可在 2.7 V~5.25 V 范围内工作,建议使用 3 V 电源以最小化板级数字噪声。DATA AVAILABLE 引脚方便用户与转换器的抽取后数据速率同步。当流水线 ADC 或数字滤波器出现溢出时,OUT-OF-RANGE(OTR)引脚给出指示。RESETB 功能可同步抽取数据并清除模拟积分器中的溢出状态。

片内集成基准及基准缓冲器,可配置为:

2.5 V 模式(差分满量程 4 Vpp)

1 V 模式(差分满量程 1.6 Vpp)

通过外接电阻分压,在 1 V~2.5 V 之间任意设定

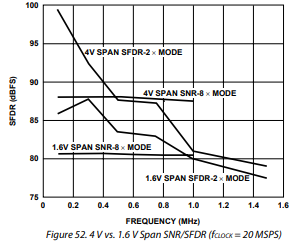

然而,如图 52 所示,只有使用 2.5 V 基准时,AD9260 才能取得最佳的噪声与失真性能。

对于需要降低时钟频率的应用,AD9260 的偏置电流支持按比例缩放:在 BIAS 引脚外接合适电阻,即可随时钟频率线性降低功耗,最高可节省约 75 %(时钟降至 5 MHz 时)。

如有型号采购及选型需求,可联系兆亿微波电子元件商城。