LT®8640/LT8640-1降压稳压器采用静音切换器架构,旨在最大限度地减少EMI排放,同时在高达3MHz的频率下提供高效率。

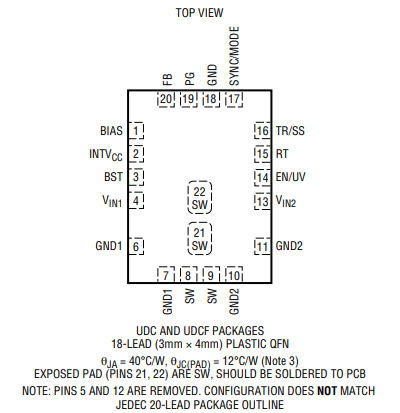

引脚配置图

关于其引脚配置功能详解如下所示:

BIAS(引脚 1)

当 BIAS 被置于高于 3.1 V 的电压时,内部稳压器改从 BIAS 而非 Vin 取电。若输出电压为 3.3 V–25 V,应把此脚直接接至 Vout。若接其它电源,须在该脚就近加 1 µF 旁路电容;若无合适电源,则接 GND。

INTVcc(引脚 2)

内部 3.4 V 稳压器旁路脚。内部功率驱动器与控制电路均由此供电,最大输出电流 20 mA,禁止外接负载。当 BIAS>3.1 V 时由 BIAS 供电,否则由 Vin 抽取电流;BIAS 在 3.0 V–3.6 V 区间时,INTVcc 电压介于 2.8 V–3.4 V。须在该脚对功率地就近接 ≥1 µF 低 ESR 陶瓷电容。

BST(引脚 3)

为顶侧功率开关提供高于输入电压的驱动电压。务必在 IC 旁边就近放置 0.1 µF 自举电容。

Vin1(引脚 4)

LT8640/LT8640-1 需要两只 1 µF 输入旁路电容:一只接在 Vin1 与 GND1 之间,另一只接在 Vin2 与 GND2 之间,均须尽量靠近芯片。此外,还需在芯片附近放一只 ≥2.2 µF 的较大电容,其正端同时接 Vin1、Vin2,负端接地。

GND1(引脚 6、7)

功率开关地,为内部底侧功率开关的回流路径,两脚必须互连。输入电容负端应尽可能靠近 GND1,并与完整地平面相连。

SW(引脚 8、9)

内部功率开关输出节点。两 SW 脚互连后接电感与自举电容,该节点在 PCB 上面积应尽可能小,以获得最佳性能并降低 EMI。

GND2(引脚 10、11)

功率开关地,同 GND1 说明:两脚互连,输入电容负端尽量靠近,并与地平面相接。

Vin2(引脚 13)

输入旁路要求与 Vin1 相同,见上文。

EN/UV(引脚 14)

低电平关断,高电平使能。上升阈值为 1.00 V,下降阈值为 0.96 V。若不用关断功能,直接接 Vin;亦可通过外部电阻分压设定欠压锁定阈值。

RT(引脚 15)

在该脚与地之间接电阻,用于设定开关频率。

TR/SS(引脚 16)

输出跟踪与软启动脚。启动过程中,若 TR/SS 电压低于 0.97 V,芯片强制 FB 脚电压等于 TR/SS 电压;高于 0.97 V 后跟踪功能关闭,内部基准重新接管误差放大器。该脚内部由 INTVcc 提供 1.9 µA 上拉电流,外接电容即可编程输出电压上升斜率。关断或故障时,内部 2 kΩ MOSFET 将其拉低;若由低阻抗源驱动,需串电阻。若不用跟踪功能,可悬空。

SYNC/MODE(引脚 17,仅 LT8640)

四种工作模式:

Burst Mode——接地,轻载时静态电流超低;

跳脉冲模式——悬空,负载降至较低时才开始跳脉冲(悬空时引脚漏电流需 <1 µA);

扩频模式——接 INTVcc(≈3.4 V)或 3 V–4 V 外部电源,在跳脉冲基础上加入扩频调制;

同步模式——外接时钟,器件以跳脉冲模式同步至外部频率。

SYNC/MODE(引脚 17,仅 LT8640-1)

四种模式:

Burst Mode——接地;

强制连续模式(FCM)——悬空,全负载范围内保持固定频率,瞬态响应快;

扩频模式——接 INTVcc 或 3 V–4 V 外部电源,在强制连续模式下加扩频;

同步模式——外接时钟,器件以强制连续模式同步至外部频率。

GND(引脚 18)

LT8640/LT8640-1 系统地,须与系统完整地平面相连。

PG(引脚 19)

电源良好开漏输出。当 FB 电压落在最终稳压值 ±8 % 以内且无故障时,PG 变高;只要 Vin>3.4 V,PG 即有效,不受 EN/UV 状态影响。

FB(引脚 20)

LT8640/LT8640-1 把 FB 脚稳压在 0.970 V。将反馈分压器抽头接至此脚,并在 FB 与 Vout 之间接一只相位超前电容(典型 4.7 pF–22 pF)。

SW(裸露焊盘引脚 21、22)

两裸露焊盘应与 SW 铜箔相连并焊牢,以获得最佳热性能。若受工艺限制无法连接,可悬空,但热性能会下降。

如有型号采购及选型需求,可直接联系兆亿微波电子元件商城。