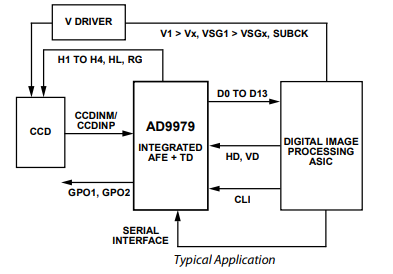

上图是AD9979的典型应用。CCD输出由AD9979的模拟前端(AFE)电路处理,该电路包括相关双采样(CDS)、可变增益放大器(VGA)、黑电平钳位和ADC。数字化后的像素数据被送至数字图像处理器芯片,进行后期处理与压缩。为使CCD正常工作,系统ASIC通过3线串行接口将所有CCD时序参数写入AD9979。AD9979以图像处理器或外部晶振提供的系统主时钟CLI为基准,产生CCD所需的水平时钟以及内部AFE的所有时钟。

AD9979的所有时钟均与VD和HD输入同步。其所有水平脉冲(CLPOB、PBLK和HBLK)均由内部编程并生成。

AD9979内部集成了H1~H4及RG的H驱动器,因此这些时钟可直接连接至CCD。AD9979支持3 V的H驱动电压。

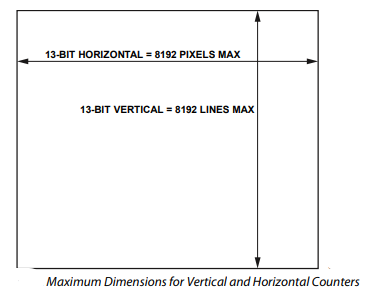

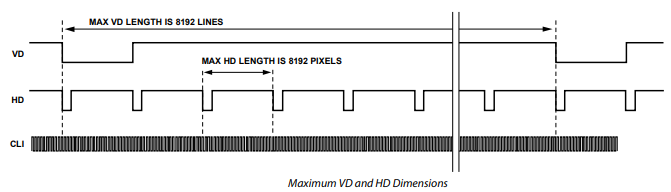

下图给出了AD9979的最大水平与垂直计数器尺寸。这些计数器控制所有内部水平与垂直时钟,用于指定行与像素位置。最大HD长度为每行8191像素,最大VD长度为每帧8192行。

如有型号采购及选型需求,可直接联系兆亿微波电子元件商城。