FM33LE0 支持以下 Flash 编程方法:

•在系统编程(ISP):通过 FMSH 专用编程器或者 KEIL 用户界面实施芯片编程,使用 SWD 接口

•在应用编程(IAP):通过 bootloader 代码实现芯片自编程,用户可定义任意串口,可用于实现程序在线升级

编程前必须对 Flash 进行擦除。Flash 支持三种擦除操作:全擦、扇区擦、页擦

一、Flash 擦写时钟

执行 Flash 擦写时使用校准后的 RCHF 时钟,但是系统时钟可以是任意时钟。NVMIF 根据当前RCHF 实际频率设置,来产生相应的计时长度。需要支持的 RCHF 频率为 8M、16M 和 24M。

擦写时钟独立于 CPU 时钟,两者之间作为异步时钟处理。

二、Flash 擦写方法

FM33LE0 支持 Flash 擦除操作,以及单次编程和连续编程。

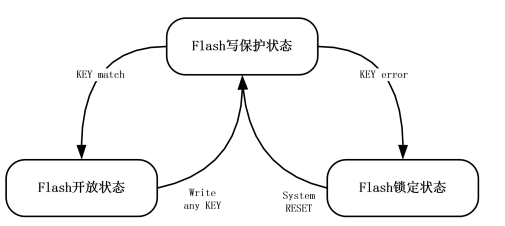

Flash 擦写前须进行 Key 校验,写入顺序错误或写入值错误,或者在 Flash Key 验证正确之前就进行擦除或编程 Flash 操作将会进入错误状态,并产生相应中断。Flash Key 认证错误之后将禁止擦写

Flash 直到下一次复位。而在正常擦写完成后,向 KEY 寄存器写入任意值都会使状态机返回初始的写保护状态。状态转换如下图:

软件可以通过查询 FLSIF.KEYSTA 来确认当前 Key 输入状态。

三、全擦操作(Matrix Erase)

全擦操作只能由 SWD 接口启动,软件禁止进行全擦。全擦操作仅擦除 main array,不会擦除特殊信息扇区。SWD 可以在制造商或用户模式下启动全擦,操作流程如下:

•编程器通过 SWD 配置 ERTYPE 寄存器为 10

•编程器通过 SWD 清除 PREQ 寄存器,置位 EREQ 寄存器

•编程器通过 SWD 写入 Flash 全擦 Key:0x9696_9696 和 0x7D7D_7D7D

•SWD 向 Flash 任意地址写擦除请求 0x1234_ABCD

•芯片启动对 Flash 的全擦,并暂停任何 Master 对 Flash 的访问

•全擦完成后置位中断标志和全擦标志(全擦标志表示 main array 全部擦除,任何对 main array的编程将清除此标志)

•在全擦标志有效的情况下,SWD 可以任意擦写 NVR0,否则擦写 NVR0 被禁止并触发错误中断

•软件确认擦除结束后向 FlashKEY 寄存器写任意值恢复写保护

四、扇区擦操作(Sector Erase)

SWD 和应用代码都可以执行扇区擦。操作流程如下:

•配置 ERTYPE 寄存器为 00

•清除 PREQ 寄存器,置位 EREQ 寄存器

•写入 Flash 块擦 Key:0x9696_9696 和 0xEAEA_EAEA

•向需要擦除的 Page 内任意地址写擦除请求 0x1234_ABCD

•芯片检查目标扇区是否属于被 ACLOCK 锁定的 Block,如果没有锁定则启动对目标扇区的擦除,如果被锁定则触发错误标志

•扇区擦完成后置位中断标志

•软件确认擦除结束后向 FlashKEY 寄存器写任意值恢复写保护

五、页擦操作(Pgae Erase)

SWD 和应用代码都可以执行页擦。操作流程如下:

•配置 ERTYPE 寄存器为 00 或 11

•清除 PREQ 寄存器,置位 EREQ 寄存器

•写入 Flash 块擦 Key:0x9696_9696 和 0xEAEA_EAEA

•向需要擦除的扇区内任意地址写擦除请求 0x1234_ABCD

•芯片检查目标扇区是否属于被 ACLOCK 锁定的 Block,如果没有锁定则启动对目标扇区的擦除,如果被锁定则触发错误标志

•扇区擦完成后置位中断标志

•软件确认擦除结束后向 FlashKEY 寄存器写任意值恢复写保护

六、单次编程

单次编程由软件发起,通过总线直接写 Flash,每次操作只能执行 word 编程,操作流程如下:

•清除 EREQ 寄存器,置位 PREQ 寄存器

•清除连续编程使能寄存器

•写入 Flash 编程 Key:0xA5A5_A5A5 和 0xF1F1_F1F1

•向 Flash 目标地址写数据,如果目标地址被 ACLOCK 锁定,则触发错误标志,如果没有锁定,则执行编程

•编程完成后置位中断标志

•软件确认编程结束后向 FlashKEY 寄存器写任意值恢复写保护

七、连续编程

连续编程指通过 DMA 的 Memory 通道一次向 Flash 写入 half-sector(256 字节)。连续编程时 DMA从 RAM 指定地址读取数据,Flash 目标编程地址必须是 half-sector 对齐的,也就是 Flash 地址低 6位为 0。采用这种方式时一次编程的数据长度是固定的,主要用于快速大数据量写入。

在启动连续编程期间,DMA 完全占据 Flash 总线,暂停 CPU 对 Flash 的一切访问。连续编程的操作流程如下:

•清除 EREQ 寄存器,置位 PREQ 寄存器

•置位连续编程使能寄存器(DMA 模式使能)

•向 RAM 中写入 256 字节待编程数据

•配置 DMA 存储器通道,设定传输方向、读地址和写地址

•使能 DMA 存储器通道

•写入 Flash 编程 Key:0xA5A5_A5A5 和 0xF1F1_F1F1

•软件触发 DMA 存储器通道,DMA 连续 64 次读取 RAM 并对 Flash 编程,芯片每收到 1 个 word自动完成 4 次 byte program

•芯片检查被编程扇区是否被 ACLOCK 锁定,如果锁定则触发错误中断并通知 DMA 停止编程

•256 字节完全编程结束后产生中断,释放 Flash 总线

•软件确认编程结束后向 FlashKEY 寄存器写任意值恢复写保护

注意:如果 CPU 在 Flash 中取指时进行 Flash 擦写,则 CPU 取指将被暂停,直到擦写操作完成。如果 CPU 跳转到 RAM 中取指运行,则 Flash 擦写不会暂停 CPU 的执行。Flash 擦写过程中,若用户希望在 RAM 中执行代码时仍然能够实时响应中断,应将中断向量表重新映射到 RAM 中。

八、启动区交换(BootSwap)

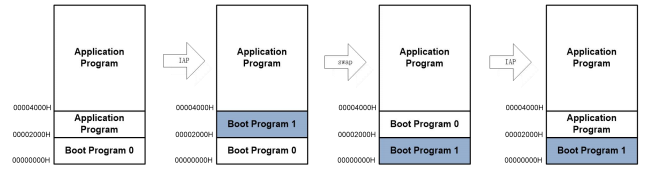

BootSwap主要目的是,防止在系统更新启动代码时出现意外中断(停电、异常复位等),如果此时原来的启动代码已经被擦除,将导致芯片重启后无法正常运行。BootSwap功能通过编程informationpage3最低地址word实现。

BootSwap示意图如下:

实现BootSwap功能后,假设启动代码占据0000~1FFF共8KB空间,系统升级时应先将新的启动代码写入2000~3FFF地址,然后使能BootSwap。此时有几种可能性:

•芯片擦写2000~3FFF地址时掉电,由于原来的启动代码还在,不会影响重启

•芯片成功写入boot program1,然后使能bootswap并执行软复位,芯片重启后将执行bootprogram1

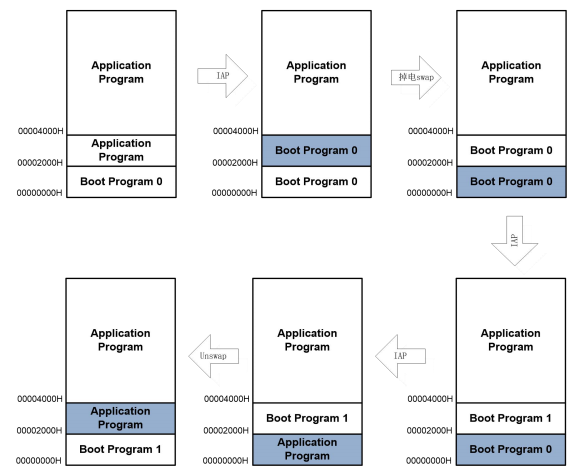

•芯片擦写boot program0时掉电,由于boot program1已经写入,将不影响后续运行另一种BootSwap应用方法如下图,为了保证可靠的更新启动代码,使用2nd 8KB物理空间作为原来Boot程序的备份,如果编程期间发生异常掉电,则触发BootSwap:

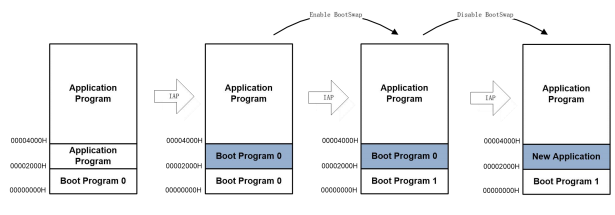

如果启动程序更新期间没有发生异常掉电,则可以不执行软复位,无需真正Swap,仅需在更新原来的Boot程序前使能BootSwap,成功更新后撤销BootSwap即可:

推荐应用按照如下步骤升级:

•更新application program

•如需升级boot,先将新的boot程序写入第二个8KB空间

•配置information block,使能BootSwap

•执行软复位,重启后执行新的boot程序

•将第二个8KB空间改写为新的应用程序

逻辑地址对Flash物理地址的重映射由NVMIF模块完成,不论程序还是DEBUG都以逻辑地址进行访问。

寄存器标志(FLSIF.BTSF)来表示当前的Boot区是1st 8KB物理地址、还是2nd 8KB物理地址,用于给用户代码查询当前启动情况。

以上是关于其的一些相关信息,如有采购及选型需求,可联系兆亿微波电子元件商城。