AD7714 的灵活串行接口使其能够轻松与大多数微计算机和微处理器相连。

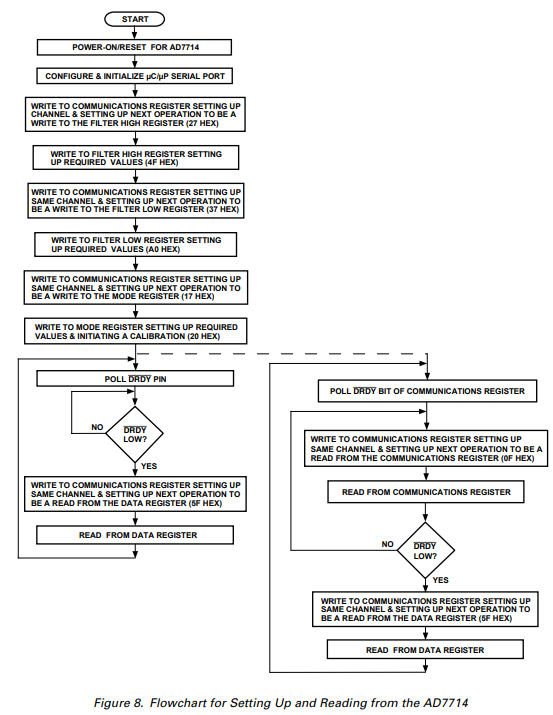

图 8 的流程图列出了将微控制器或微处理器连接到 AD7714 时应遵循的步骤;

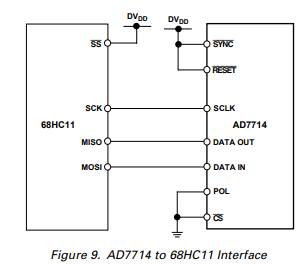

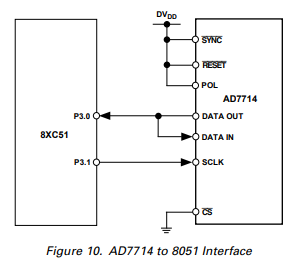

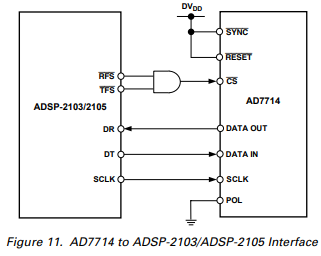

图 9、10 和 11 给出了几种典型接口电路。

AD7714 的串行接口最少只需三根线即可工作,兼容 SPI 协议。三线操作使该器件特别适合隔离系统——接口线越少,所需的光耦数量也越少。

AD7714 数字输入(尤其是 SCLK)的上升/下降时间应 ≤ 1 µs。

器件内大部分寄存器为 8 位宽,便于与微控制器的 8 位串行口对接。部分寄存器长达 24 位,但数据可按一次 24 位或分三次 8 位的方式传输。DSP 或微处理器通常一次串行传输 16 位数据;某些处理器(如 ADSP-2105)可编程串行传输的位数,从而灵活匹配 AD7714 各寄存器的长度。

尽管有些寄存器仅 8 位,但若需要,可把连续两次写操作合并成一次 16 位传输。例如,更新模式寄存器时,须先写通信寄存器(告知下一步将写模式寄存器),再写 8 位数据到模式寄存器;若愿意,这两步可合并成一次 16 位传输——一旦写完通信寄存器的 8 个时钟周期,器件立即准备好接收模式寄存器的 8 位数据。

AD7714 与 68HC11 的接口

图 9 展示了 AD7714 与 68HC11 微控制器之间的接口方案。图中给出了最少仅需三根线的接法:将 AD7714 的 CS 引脚直接硬接地(保持低电平)。在此方式下,通过查询通信寄存器中的 DRDY 位来判断数据寄存器是否已更新。

另一种方案把接口线增加到四条,即直接监视 AD7714 的 DRDY 输出引脚。具体又可分两种做法:

将 DRDY 接到 68HC11 的某个端口位(如 PC0),并配置为输入,然后轮询该端口位以获取 DRDY 状态。

采用中断方式:把 DRDY 输出连接到 68HC11 的 IRQ 中断输入引脚,实现中断驱动。

若需要由 68HC11 控制 AD7714 的 CS,可用另一个端口位(如 PC1)配置为输出,来驱动 CS 引脚。

68HC11 配置为主机模式,CPOL 位清零、CPHA 位置一。此时 68HC11 的 SCLK 在空闲时保持低电平,因此 AD7714 的 POL 引脚应直接接地。若希望 SCLK 空闲时为高,则须将 68HC11 的 CPOL 置 1,并把 AD7714 的 POL 引脚接高。

AD7714 不支持全双工。若配置为写操作,即使 SCLK 有效,DATA OUT 也不会输出数据;若配置为读操作,即使 SCLK 有效,DATA IN 上的数据也会被忽略。

AD7714 与 8XC51 的接口

图 10 展示了 AD7714 与 8XC51 微控制器的接口电路。图中给出最少连线方案:AD7714 的 CS 直接接地。对于 8XC51,最少只需两根线即可工作:通过查询通信寄存器的 DRDY 位来判断数据寄存器是否更新。若把 AD7714 的 DRDY 输出引脚也用上,则接口线增至三根,有两种监测方式:

将 DRDY 接到 8XC51 的某个输入端口位(如 P1.0),然后轮询该位;

采用中断方式,把 DRDY 接到 8XC51 的 INT1 引脚。

若需要 8XC51 控制 AD7714 的 CS,可用另一个输出端口位(如 P1.1)来驱动 CS。

8XC51 使用其模式 0 串行接口,该接口只有一条数据线,因此须把 AD7714 的 DATA OUT 与 DATA IN 短接。8XC51 的串行时钟在空闲时为高,故 AD7714 的 POL 应接高电平。

8XC51 写操作时先输出最低位(LSB),而 AD7714 要求最高位(MSB)在前,因此数据在写入输出寄存器前必须重新排列;读操作时 AD7714 先输出 MSB,而 8XC51 期望 LSB 在前,故读入的数据也需重新整理,才能在累加器中得到正确字序。

AD7714 与 ADSP-2103/ADSP-2105 的接口

图 11 给出了 AD7714 与 ADSP-2103/ADSP-2105 DSP 处理器的接口。图中仍通过查询通信寄存器的 DRDY 位来判断数据寄存器更新;也可改用中断方式,将 DRDY 接到 DSP 的 IRQ2 引脚。

ADSP-2103/2105 的 RFS、TFS 引脚配置为低有效输出,串行时钟 SCLK 也配置为输出。AD7714 的 POL 引脚接地。由于 ADSP 的 SCLK 是连续时钟,传输结束后必须用 CS 信号把时钟门控掉。CS 在 RFS 或 TFS 任一有效时即为有效。ADSP-2103/2105 的串行时钟频率应限制在 3 MHz 以内,以确保与 AD7714 正常通信。

如有型号采购及选型需求,可直接联系兆亿微波电子元件商城。