串行控制接口

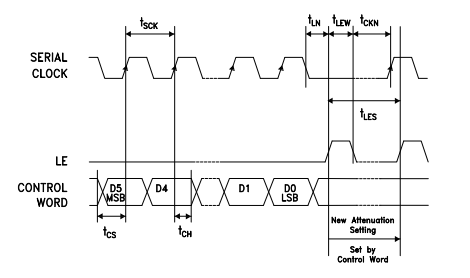

HMC792ALP4E 内置一个 3 线 SPI 兼容数字接口(SERIN、CLK、LE)。当引脚 P/S 保持高电平时,串行控制接口被激活。6 位串行字必须先送最高位(MSB)。CLK 和 LE 对上升沿敏感,需要干净无抖动的跳变;若使用机械开关,应做好去抖处理。

当 LE 为高时,串行输入寄存器中的 6 位数据被传送至衰减器。

在 LE 为高期间,CLK 被屏蔽,防止在输出加载过程中发生数据翻转。

当 P/S 为低时,3 线 SPI 接口输入(SERIN、CLK、LE)被禁用,输入寄存器改为由并行数字输入 D0–D5 加载。当 LE 为高时,这 6 位并行数据按照真值表改变芯片状态。

无论哪种工作模式,只要 LE 保持低电平,衰减状态就会保持不变。

并行模式

(直接并行模式 & 锁存并行模式)

注意:将 P/S 置低即可启用并行模式。

1.直接并行模式

衰减状态由控制电压输入 D0–D5 直接决定。此时 LE(锁存使能)必须始终保持逻辑高,才能用这种方式控制衰减器。

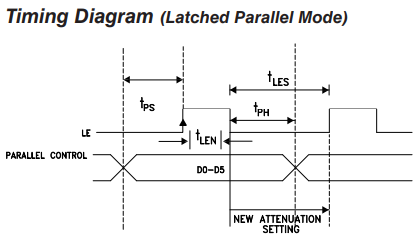

2.锁存并行模式

先用 D0–D5 选定所需的衰减状态,但此时 LE 处于低电平,衰减器并不会立即改变状态。待所有控制电压输入稳定后,再给 LE 一个脉冲,即可将新状态锁存进衰减器。时序请参考上方的时序图。

上电状态与上电顺序

1.上电状态

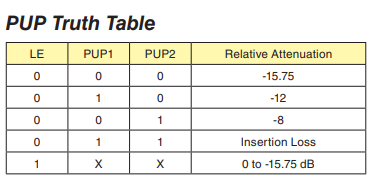

若上电时 LE 为低,则 PUP1、PUP2 的逻辑电平决定芯片的上电初始状态(见 PUP 真值表)。

若上电时 LE 为高,则由 D0–D5 的逻辑电平决定上电初始状态(见真值表)。

芯片会在上电后约 200 ms 锁存所需的上电状态。

2.推荐上电顺序

地(GND)

电源(VDD)

数字输入

RF 输入

只要保证数字输入在 VDD/GND 之后上电,其内部先后顺序并不重要。

上述则是关于HMC792ALP4E数字衰减器芯片的相关接口及操作信息,如有型号采购及选型需求,可直接联系兆亿微波电子元件商城。