ADRF6755 支持 2 线、I²C 兼容串行总线,可挂接多个外设。串行数据 (SDA) 与串行时钟 (SCL) 在两台设备之间传递信息,每个从机靠唯一地址识别。

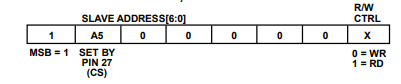

芯片提供 2 组 7 位从机地址,均支持读/写。

– 地址高 7 位的 MSB 固定为 1;Bit A5 由 CS 引脚(27 脚)电平决定;Bit[4:0] 固定为全 0。

– 7 位从机地址占据 8 位字的高 7 位,最低位 (LSB) 决定操作方向:1=读,0=写(见下图)。

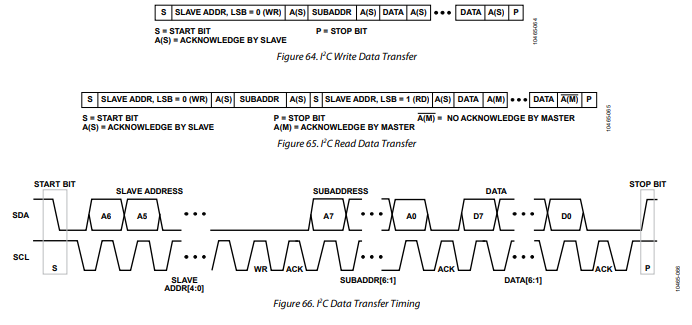

总线协议

主机发出“起始条件”:SCL 为高时 SDA 由高→低跳变,表示即将传输地址/数据。

所有外设收到起始条件后,依次接收 8 位(7 位地址+R/W 位),MSB 在前。

地址匹配的从机在第 9 个时钟周期把 SDA 拉低作为应答 (ACK),其余设备退出并保持空闲。

R/W 位决定数据方向:

– 0:主机→从机(写)

– 1:从机→主机(读)

ADRF6755 作为标准从机

SDA(29 脚)数据帧为 8 位:7 位地址+1 位 R/W。

片内共有 34 个用户寄存器(子地址)。

– 第一字节:器件地址

– 第二字节:起始子地址

支持自动递增:读写起始子地址后,地址指针自动 +1,无需再次写入子地址。

任何传输均以“停止条件”结束;也可单独访问任意子地址,而不必更新全部寄存器。

若在传输过程中检测到异常的起始/停止条件,芯片立即返回空闲状态。

若用户发出无效子地址,ADRF6755 不拉低 SDA(无应答),并返回空闲。

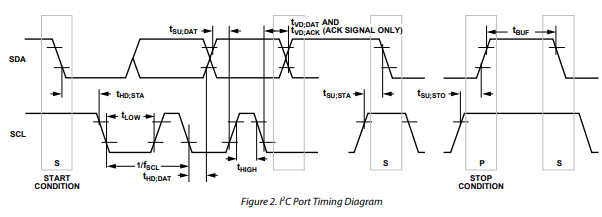

图 64、65 的读写时序示例,图 66 的协议概要,以及图 2 的详细时序图可供参考。

上述就是关于ADRF6755可编程衰减器的I²C 接口分析,希望对你在选型及使用过程中有所帮助。