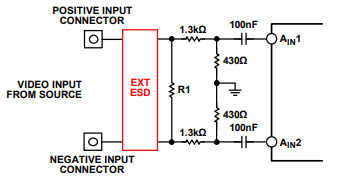

差分输入网络

当差分 CVBS 视频信号接入 ADV7182 的 AIN 引脚时,请使用上图所示的输入网络。

建议将该输入网络尽可能靠近 ADV7182 的 AIN 引脚放置。

差分视频传输通过发送两路互补的 CVBS 信号实现,与单端传输相比具有多项显著优势:

天然抑制小信号与大信号噪声

改善 EMI 性能

能够吸收地弹干扰

电阻 R1 为差分 CVBS 输入线提供射频终端匹配:

伪差分 CVBS 输入时,R1 建议取 75 Ω

全差分 CVBS 输入时,R1 建议取 150 Ω

1.3 kΩ 与 430 Ω 电阻构成分压器,增益为 0.25,在衰减输入模拟视频幅度的同时,把 ADV7182 的输入共模范围扩展至最高 4 V(峰峰值)。

注意:ADV7182 内部放大器会恢复信号幅度,因此信噪比性能不受影响。

100 nF 交流耦合电容在信号进入 ADV7182 模拟输入引脚前去除直流偏置;片内钳位电路在信号送入 ADC 前将其直流偏置恢复至最优电平。

1.3 kΩ、430 Ω 电阻与 100 nF 电容的组合还可在“对电池短路”(STB)事件中限制流入 ADV7182 的电流。

为获得最佳性能,1.3 kΩ 与 430 Ω 电阻应严格匹配:所有对应电阻需采用相同且尽可能低的阻值容差。