同步串行接口(SSI)

AD9864 可通过 SSI 高度定制输出数据格式、控制信号与时序参数,以适配不同数字接口。

3 线模式:提供帧同步 FS、时钟 CLKOUT、串行数据 DOUTA。

2 线模式:帧同步信息嵌入数据流,仅输出 CLKOUT 与 DOUTA。

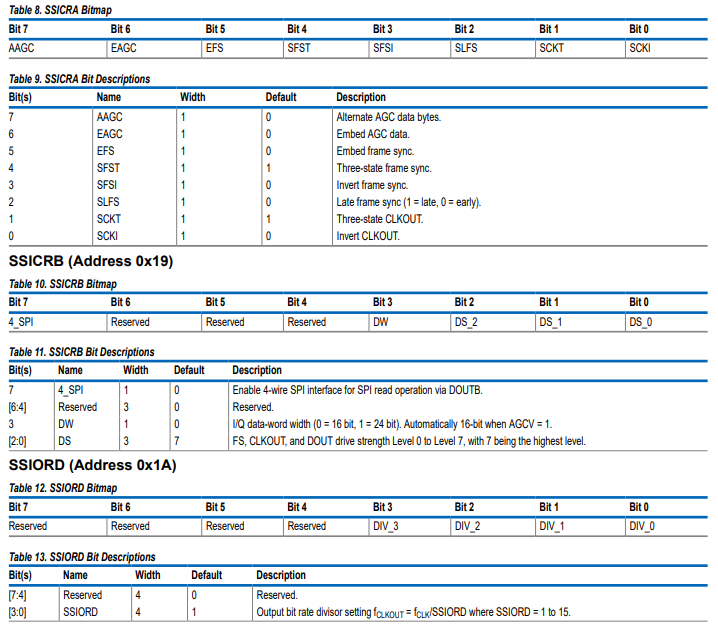

相关寄存器:SSICRA、SSICRB、SSIORD(位定义见表 8–13,见文末附件图)。

芯片主输出为经数字下变频后的 I/Q 基带信号,以串行帧形式从 SSI 端口送出。帧速率 = 调制时钟 fCK ÷ 抽取因子(寄存器 0x07)。

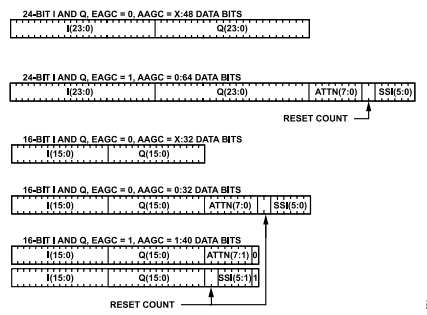

帧格式:先 I 字后 Q 字,每字 24 bit 或 16 bit,二进制补码,MSB 在前。

帧尾可附加两个字节:

字节 1:8 bit AGC 衰减量(0=0 dB,255=24 dB)

字节 2:2 bit 复位计数 + 6 bit 接收信号强度估计(RSSIL)

下图给出了多种 SSI 模式下的帧结构。

可选字节细节

仅当 SSICRA 的 EAGC 位置 1 时附加字节才输出。

首字节:8 bit 衰减值

次字节:2 bit 自上次报告以来的调制器复位事件数(饱和值 3),6 bit RSSIL(线性估计,60 对应满幅信号)

若 SSICRA 的 AAGC 位为 0,两字节合并为 16 bit 字紧随 Q 字之后;若 AAGC=1,则进入“交替 AGC 数据模式”:

含衰减字节 LSB=0

含复位/RSSI 字节 LSB=1

两字节交替出现。

2 线模式

将 SSICRA 的 EFS 位置 1 即启用嵌入式帧同步。每 8 bit 数据前后分别插入 1 bit 起始(低)与 1 bit 停止(高),帧尾至少 10 个高电平。FS 引脚根据 SFST 位决定保持低电平或高阻(默认)。

其它控制位:

SFSI:帧同步极性反转

SLFS:帧同步延迟 1 时钟周期(EFS=1 时无效)

SCKI:时钟极性反转

SCKT:时钟高阻使能

速率设置

SSIORD 寄存器设定串行比特率 fCLKOUT:

fCLKOUT = fCK ÷ SSIORD

须保证该速率在目标信号通带内不引入有害杂散,且能满足当前字长与抽取因子对应的每帧总 bit 数;不足部分用空闲高电平 bit 填充。

附件图(表8-13)