VCO

ADF4372 的 VCO 由四个独立的 VCO 内核组成:内核 A、内核 B、内核 C 和内核 D。每个内核使用 256 个重叠频带,使器件在具备较大 VCO 灵敏度(Kv)的同时,能够覆盖宽广的频率范围,且不会导致相位噪声和杂散性能恶化。

每当寄存器地址 0x10 被更新且自动校准使能时,VCO 及频带选择逻辑会自动选定合适的 VCO 与频带。此时,VCO 调谐电压将与环路滤波器输出断开,转而连接至内部基准电压。

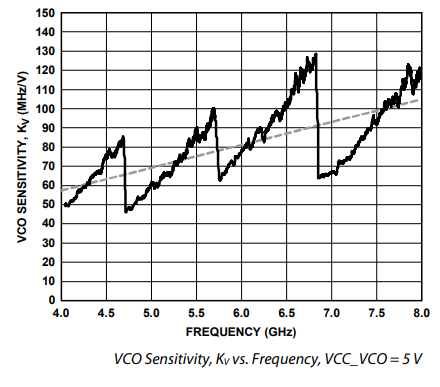

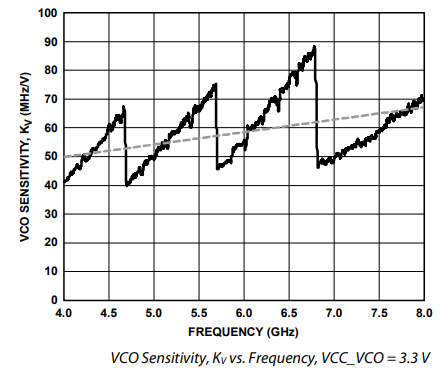

R 计数器输出用作频带选择逻辑的时钟。频带选择完成后,PLL 恢复正常工作。当 N 分频器由 VCO 输出直接驱动时,Kv 的标称值为 50 MHz/V;若 N 分频器由射频输出分频器驱动,则 Kv 值需除以输出分频系数 D。

随着调谐电压 VTUNE 在频带内变化以及在不同频带间切换,Kv 值亦会随之改变。对于覆盖宽频率范围(并切换输出分频器)的宽带应用,采用 50 MHz/V 的数值可获得最准确的 Kv,因为该值最接近平均值。图 33 和图 34 展示了 Kv 随 VCO 基频的变化情况,以及各频带的平均值。在进行窄带设计时,建议参考下面两张图。