SPI 模式

标准 SPI

GD25Q128E 采用 4 线串行外设接口总线:串行时钟(SCLK)、片选(CS#)、串行数据输入(SI)和串行数据输出(SO)。支持 SPI 总线模式 0 和模式 3。输入数据在 SCLK 的上升沿被锁存,数据在 SCLK 的下降沿移出。

双线 SPI

GD25Q128E 在使用"双线输出快速读取"和"双线 I/O 快速读取"命令(3BH 和 BBH)时支持双线 SPI 操作。这些命令允许以标准 SPI 两倍的速度与器件进行数据传输。使用双线 SPI 命令时,SI 和 SO 引脚变为双向 I/O 引脚:IO0 和 IO1。

四线 SPI

GD25Q128E 在使用"四线输出快速读取"、"四线 I/O 快速读取"命令(6BH、EBH)时支持四线 SPI 操作。这些命令允许以标准 SPI 四倍的速度与器件进行数据传输。使用四线 SPI 命令时,SI 和 SO 引脚变为双向 I/O 引脚 IO0 和 IO1,WP# 和 HOLD#/RESET# 引脚变为双向 I/O 引脚 IO2 和 IO3。四线 SPI 命令要求状态寄存器中的非易失性四线使能位(QE)设置为 1。

HOLD 功能

HOLD/RST 位用于确定在 8 引脚封装的硬件引脚上应实现 HOLD 功能还是 RESET 功能。当 HOLD/RST=0 时,HOLD#/RESET# 引脚作为 HOLD# 引脚。当 QE=0 时,HOLD 功能可用。如果 QE=1,HOLD 功能被禁用,HOLD#/RESET# 引脚作为专用数据 I/O 引脚。

HOLD# 信号变为低电平可停止与器件的任何串行通信,但正在进行的写状态寄存器、编程或擦除操作除外。

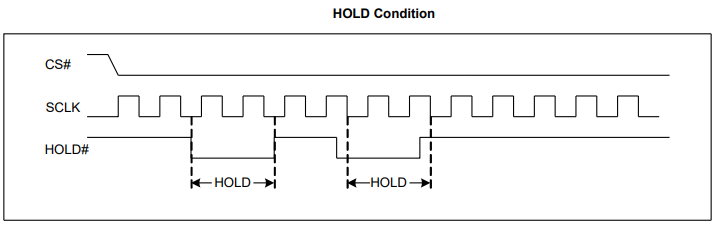

HOLD 操作需要 CS# 保持低电平,在 HOLD# 信号下降沿且 SCLK 信号为低电平时启动。如果 SCLK 不为低电平,HOLD 操作直到 SCLK 为低电平时才会启动。HOLD 状态在 HOLD# 信号上升沿且 SCLK 为低电平时结束。如果 SCLK 不为低电平,HOLD 操作直到 SCLK 为低电平时才会结束。

在 HOLD 操作期间,SO 为高阻态,SI 和 SCLK 在此期间无关。如果在 HOLD 操作期间 CS# 被拉高,将复位器件内部逻辑。要重新启动与芯片的通信,HOLD# 必须先变为高电平,然后 CS# 必须变为低电平。