设计高频、快速开关、大电流电路时,必须仔细考虑 PCB 布局。以下是针对这些考虑因素的一些建议:

A3941 的接地(GND)和外部 FET 的大电流返回端应分别连接到电机供电滤波电容负端的两侧。这将最小化开关噪声对器件逻辑和模拟基准的影响。

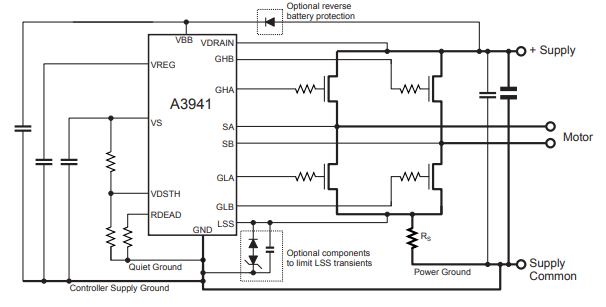

裸露散热焊盘应连接到 GND 引脚,并可构成控制器供电接地的一部分(见下图)。

在所有功率 FET 的漏极和源极端使用短而宽的铜走线,以最小化杂散电感。这包括电机引线连接、输入电源母线以及低端功率 FET 的公共源极。这将最小化大负载电流快速开关引起的感应电压。

考虑在功率 FET 的源极和漏极之间使用小型(100 nF)陶瓷去耦电容,以限制电路走线电感引起的快速瞬态电压尖峰。

保持栅极放电返回连接 Sx 和 LSS 尽可能短。这些走线上的任何电感都将在相应的 A3941 引脚上引起负向瞬变,可能超过绝对最大额定值。如果可能,考虑使用钳位二极管将这些引脚相对于 GND 的负向偏移限制在安全范围内。

敏感连接如 RDEAD 和 VDSTH 具有极小的对地电流,应连接到独立接地(见下图),且应靠近 GND 引脚独立连接。这些敏感元件绝不能直接连接到电源公共端或公共接地平面。它们必须直接以 GND 引脚为基准。

VBB、VREG 和 V5 的电源去耦应连接到控制器供电接地,该接地靠近 GND 引脚独立连接。去耦电容也应尽可能靠近相应的供电引脚连接。

如果布局空间有限,安静接地和控制器供电接地可以合并。在这种情况下,确保死区时间电阻的接地返回端靠近 GND 引脚。

使用靠近地端的探头(尖端和接地弹簧)检查 LSS 引脚上晶体管的峰值电压偏移,以 GND 引脚为参考。如果 LSS 上的电压超过本数据表所示的绝对最大值,在 LSS 引脚和 GND 引脚之间增加额外的钳位和电容,如下图 所示。

栅极充电驱动路径和栅极放电返回路径可能承载大的瞬态电流脉冲。因此,来自 GHx、GLx、Sx 和 LSS 的走线应尽可能短,以减小电路电感。

从 LSS 到功率桥公共点提供独立连接。不建议将 LSS 直接连接到 GND 引脚,因为这可能向死区时间定时器等敏感功能注入噪声。

可在 VBB 连接中放置一个低成本二极管,以提供反向电池保护。在反向电池条件下,可以使用功率 FET 的体二极管将反向电压钳位到约 4V。在这种情况下,VBB 连接中的附加二极管将防止 A3941 损坏,VDRAIN 输入将承受反向电压。

注意:以上仅为建议。每个应用都不同,可能遇到不同的敏感性问题。运行几安培的驱动器比运行 150 A 的驱动器敏感性更低,每个设计都应在最大电流下进行测试,以确保消除任何寄生效应。

下图: