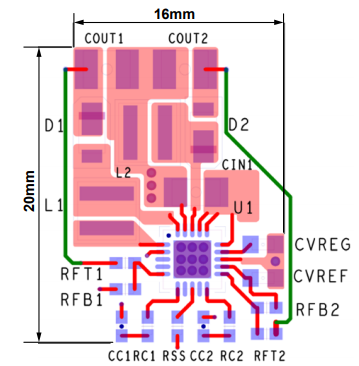

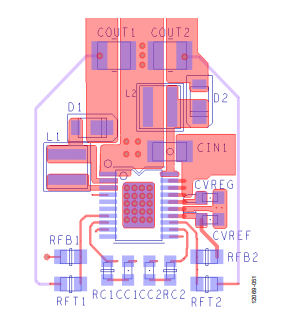

布局对所有开关稳压器都很重要,但对于高开关频率的稳压器尤为重要。为了实现高效率、良好的调节性能、良好的稳定性和低噪声,需要精心设计的 PCB 布局。设计 PCB 时请遵循以下准则:

输入旁路电容

将输入旁路电容 CIN 尽可能靠近 PVIN1 引脚、PVIN2 引脚和 PVINSYS 引脚

将每个引脚单独布线至该电容的焊盘,以最小化功率输入之间的噪声耦合,而不是在器件处将三个引脚连接在一起

可在 PVINSYS 引脚上使用单独的电容以获得最佳噪声性能

高电流路径

使高电流路径尽可能短。这些路径包括:

CIN1、L1、L2、D1、D2、COUT1、COUT2 和 PGND 之间的连接

它们与 ADP5071 的连接

接地处理

在电路板顶层将 AGND 和 PGND 分开。这种分离可避免 AGND 被开关噪声污染

不要将 PGND 连接到顶层布局上的 EPAD

通过过孔将 AGND 和 PGND 都连接到电路板地平面

理想情况下,将 PGND 连接到电路板上输入和输出电容之间的某一点

将其 EPAD 通过过孔单独连接到该接地层,并尽可能靠近 CVREF 和 CVREG 电容之间的位置连接 AGND

其他关键准则

使高电流走线尽可能短而宽,以最小化寄生电感(会导致尖峰和电磁干扰 EMI)

避免在任何连接到 SW1 和 SW2 引脚的节点附近或电感 L1 和 L2 附近布置高阻抗走线,以防止辐射开关噪声注入

将反馈电阻尽可能靠近 FB1 和 FB2 引脚放置,以防止高频开关噪声注入

将上部反馈电阻 RFT1 和 RFT2 的顶端,或从 COUT1 和 COUT2 顶端到它们的走线尽可能靠近布置,以实现最佳输出电压检测

将补偿元件尽可能靠近 COMP1 和 COMP2 放置。不要与反馈电阻共享到过孔地平面的过孔,以避免将高频噪声耦合到敏感的 COMP1 和 COMP2 引脚

将 CVREF 和 CVREG 电容尽可能靠近 VREG 和 VREF 引脚放置。确保 VREF 和 RSET 之间使用短走线