设计容纳 AD7606C-18 的 PCB 时,建议遵循以下布局指南:

接地平面:如果系统中多个器件需要模数地连接,使用完整的接地平面(不在模拟地和数字地之间分割)

接地连接:与接地平面建立稳定连接。避免多个接地引脚共享一个连接。对每个接地引脚使用单个过孔或多个过孔连接到接地平面

避免数字线下穿:避免在器件下方走数字线,因为这会将噪声耦合到芯片上。允许模拟地平面在 AD7606C-18 下方运行以避免噪声耦合

屏蔽快速开关信号:用数字地屏蔽 CONVST 或时钟等快速开关信号,避免向电路板其他部分辐射噪声,并确保它们不靠近模拟信号路径

避免信号交叉:避免数字和模拟信号交叉

正交布线:确保电路板上相邻层的走线相互垂直,以减少贯穿电路板的馈通效应

电源线设计:确保 AD7606C-18 的 AV_CC 和 V_DRIVE 引脚的电源线使用尽可能大的走线,以提供低阻抗路径并减少电源线上的毛刺效应。尽可能使用电源平面,并在 AD7606C-18 电源引脚和电路板电源走线之间建立稳定连接。对每个电源引脚使用单个过孔或多个过孔

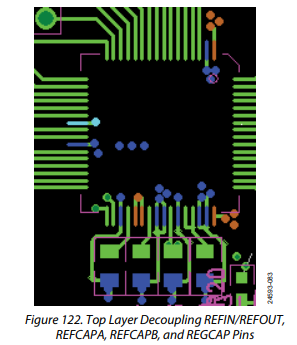

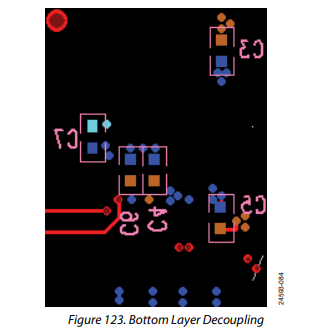

去耦电容放置:将去耦电容放置在靠近(理想情况下直接紧贴)电源引脚及其相应接地引脚的位置。将 REFIN/REFOUT 引脚和 REFCAPA 引脚及 REFCAPB 引脚的去耦电容尽可能靠近各自相应的 AD7606C-18 引脚。尽可能将这些电容放置在 AD7606C-18 器件的同一侧

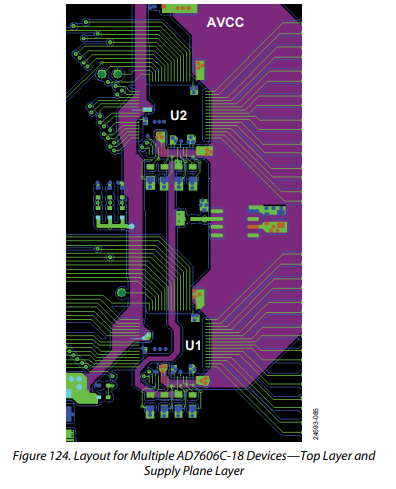

为了确保在包含多个AD7606C-18设备的系统中稳定的设备间性能匹配,AD7606C-118设备之间的对称布局非常重要。

图 122 显示了 AD7606C-18 PCB 顶层推荐的去耦方式。图 123 显示了底层去耦,用于四个 AV_CC 引脚和 V_DRIVE 引脚的去耦。

当 AV_CC 引脚的陶瓷 100 nF 电容放置在靠近各自器件引脚的位置时,引脚 37 和引脚 38 之间可以共享一个 100 nF 电容。

图 124 显示了包含两个 AD7606C-18 器件的布局。AV_CC 电源走线位于两个器件的右侧,V_DRIVE 电源走线位于两个器件的左侧。基准芯片位于两个器件之间,基准电压走线向北至 U1 的引脚 42,向南至 U2 的引脚 42。使用完整的接地平面。

这些对称布局原则也可应用于包含两个以上 AD7606C-18 器件的系统。AD7606C-18 器件可以从北向南放置,基准电压位于器件中间,基准走线从北向南运行,类似于图 124。