串行接口

AD9833 具有标准 3 线串行接口,兼容 SPI、QSPI™、MICROWIRE® 和 DSP 接口标准。

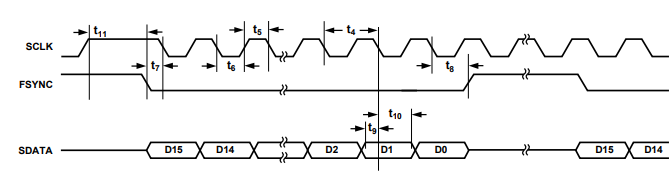

数据以 16 位字的形式在串行时钟输入 SCLK 的控制下加载到器件中。该操作的时序图见下图。

FSYNC 输入是一个电平触发输入,用作帧同步和芯片使能。仅当 FSYNC 为低电平时,数据才能传输到器件中。要开始串行数据传输,应将 FSYNC 拉低,同时遵守最小的 FSYNC 到 SCLK 下降沿建立时间 t₇。FSYNC 变低后,串行数据在 SCLK 的 16 个时钟周期的下降沿移入器件的输入移位寄存器。FSYNC 可在第 16 个 SCLK 下降沿之后拉高,同时遵守最小的 SCLK 下降沿到 FSYNC 上升沿时间 t₈。或者,FSYNC 可保持低电平持续多个 16 个 SCLK 脉冲,然后在数据传输结束时拉高。这样,可以在 FSYNC 保持低电平时连续加载 16 位字流;FSYNC 仅在最后一个字加载的第 16 个 SCLK 下降沿之后拉高。

SCLK 可以是连续的,也可以在写操作之间空闲为高电平或低电平。在任何情况下,当 FSYNC 变低时(t₁₁),SCLK 必须为高电平。