AD8021 采用亚德诺半导体专有高压超快速互补双极型(XFCB)工艺制造,该工艺能够在 3 GHz 区域构建具有相似 fT 的 PNP 和 NPN 晶体管。这些晶体管与衬底(以及彼此之间)是介质隔离的,消除了结隔离引起的寄生效应和闩锁问题。它还减少了非线性电容(失真源),并允许在给定静态电流下获得更高的晶体管 fT,从而减少了器件之间的带宽、压摆率、失真和建立时间的差异。

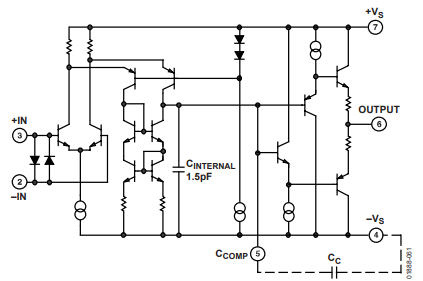

如上图所示,AD8021 的输入级由 NPN 差分对组成,每个晶体管在 0.8 mA 集电极电流下工作。这使得输入器件具有高跨导;因此,AD8021 在 50 kHz 时具有 2.1 nV/√Hz 的低输入噪声。输入级驱动一个由一对 PNP 晶体管组成的折叠共源共栅结构。折叠共源共栅和电流镜提供差分到单端的信号电流转换。该电流然后驱动高阻抗节点(Pin 5),此处连接 Cc 外部电容。输出级保持这种高阻抗,电流增益为 5000,因此 AD8021 即使在驱动重负载时也能保持高开环增益。

两个内部二极管钳位跨接在输入端(Pin 2 和 Pin 3),保护输入晶体管免受可能导致发射极-基极击穿的大电压影响,这将导致失调电压和输入偏置电流的劣化。