SPI 描述

DVGA(可变增益放大器)的衰减控制和功率模式可通过由 CSB、CLK 和 SDI 组成的三线 SPI 接口进行编程。第四个引脚 SDO 是一个串行输出,可用于读取寄存器内容。SDO 引脚还可用于在单个总线上 Daisy-chain(菊花链式连接)多个 SPI 接口。例如,在一个四通道接收机应用中,所有四个 LTC5555 下变频器均可通过一次 32 位加载操作进行编程,同时共享一条公共的 CSB 线路。

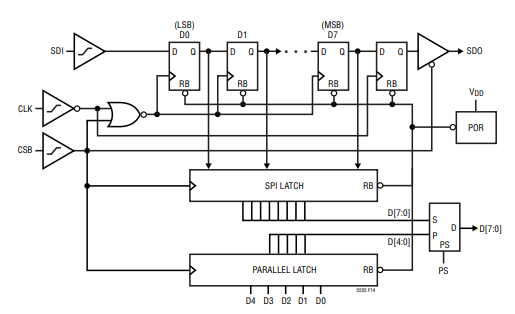

上图显示了 SPI 的框图。如图所示,它是一个 8 位双缓冲 FIFO 从架构。数字输入和 SDO 输出的逻辑电平为 1.8V 至 3.3V CMOS 兼容,具体取决于 VDD 引脚上的供电电压。内部 POR(上电复位)连接到 VDD 引脚,在上电时或当 VDD 降至低于 0.5V 并随后回升至高于 1.2V 时,将所有 8 个比特重置为逻辑 0。POR 需要约 100μs 来重置寄存器。

SPI 编程

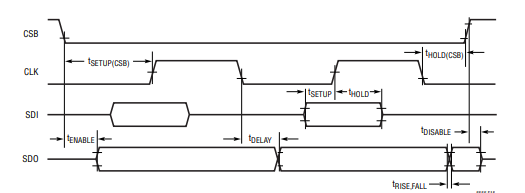

向器件传输数据时,首先将 CSB 拉低以启用端口。然后,在 CLK 上升沿捕获 SDI 上的串行输入数据,并按 MSB(最高有效位)优先顺序移入一个 8 位移位寄存器。来自寄存器的串行数据在时钟下降沿驱动到 SDO。通信突发通过将 CSB 拉高终止。CSB 的上升沿会将移位寄存器的内容锁存到一个 8 位缓冲 D 锁存器中。该缓冲锁存器可防止在下变频器加载数据期间其增益和功率模式发生变化。时序细节请参阅下图。

当 CSB 为高电平时,时钟和数据输入在内部被门控关闭,从而在未选中时最小化电流消耗,且 SDO 输出处于高阻态。然而,建议在数据传输之间保持串行接口信号空闲,以避免数字噪声耦合进 RF 信号路径。