AD8343 电子元器件要求使用差分负载,原因与输入端需要差分源以获得最佳器件性能相同。此外,差分负载可提供最佳的本振(LO)到输出隔离度,以及最佳的输入到输出隔离度。

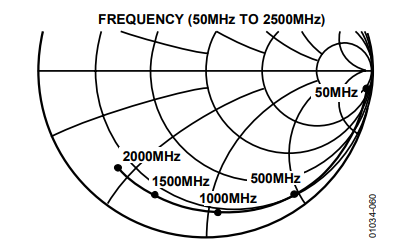

在低输出频率下,通常不建议在器件输出与负载之间安排共轭匹配,即使这样做可以最大化小信号变频增益。这是因为低频时输出阻抗非常高(高电阻与小电容并联)。可参考上图,其中绘制了在器件引脚处测得的差分输出阻抗随频率变化的曲线。

若使用高阻抗负载,则即使在相对较低的输出电平下,也会因足够的输出电压摆幅而导致输出削波,从而造成动态范围损失。每个输出引脚的线性电压摆幅约为 ±1 V(相对于电源电压 VPOS)。一个良好的折衷方案是在所需输出频率下,在两个输出引脚之间提供约 200 Ω 至 500 Ω 的负载阻抗(基于每路 15 mA 至 20 mA 的偏置电流)。在低于 500 MHz 的输出频率下,通过采用较低的负载阻抗,可在出现严重削波前获得更高的输出功率;但此时增益和低端失真性能可能会有所下降。

在镜像频率处,输出负载阻抗也必须保持合理偏低,以避免产生显著的额外电压摆幅,否则会降低动态范围。

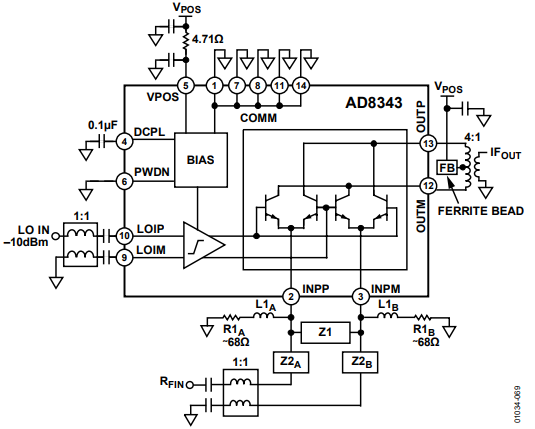

如果不需要维持良好的输出回波损耗,可使用 4:1 至 8:1(阻抗比) 的磁通耦合变压器,为器件呈现合适的负载,并通过中心抽头提供集电极偏置,如图上图所示。除最低输出频率外,通常建议在输出引脚间连接一个电感,以对 AD8343 的输出电容进行调谐。另一方面,若希望获得良好的输出回波损耗,则可通过在输出引脚间并联一个分流电阻来对输出进行阻性加载,从而设定输出阻抗的实部。通过适当选择变压器的阻抗比和所需的分流电阻值,可实现总负载阻抗约 –500 Ω,同时优化信号传输效率和输出回波损耗。

在较高输出频率下,器件的输出电导会升高(参见第一张图片),因此在高于约 900 MHz 时,对负载与 AD8343 输出之间进行共轭匹配变得合适。此时器件自身的输出导纳已足够大,可消除因过大电压摆幅导致的削波风险。正如输入端一样,最好在电路板布局上进行差分输出阻抗测量,以便有效设计良好的匹配网络。