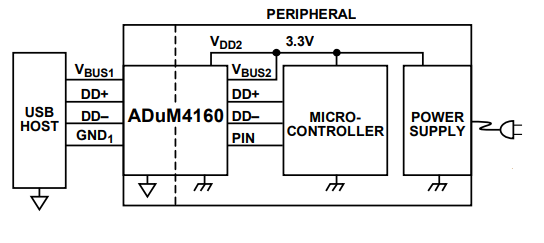

ADuM4160 设计用于集成到具有面向主机(上游)USB 端口的 USB 外设中,如ADuM4160典型应用电路图所示。关键设计要点如下:

USB 主机通过电缆为 ADuM4160 的上游侧供电。

外设电源为 ADuM4160 的下游侧供电。

隔离器的 DD+/DD− 引脚与外设控制器连接;而 UD+/UD− 引脚则连接至电缆或主机。

外设在设计时即已设定固定数据速率。ADuM4160 配有配置引脚 SPU 和 SPD,用于确定每侧的数据速率及逻辑约定。这些引脚必须设置为相同值,并匹配所需的外设速度。

USB 枚举过程始于 UD+ 或 UD− 线路在外设端被拉高——该动作发生在 ADuM4160 的上游侧。此事件的时间控制由耦合器下游侧的 PIN 输入提供。

上拉和下拉电阻已在耦合器内部实现。运行仅需外部串联电阻和旁路电容。

上图为ADuM4160典型应用电路

除上拉电阻存在延迟施加外,ADuM4160 对 USB 流量完全透明,无需对外设设计进行任何修改即可实现隔离。隔离器引入的信号传播延迟相当于一个集线器加一根电缆的长度。因此,在确定数据链中最大集线器数量时,应将隔离外设视为内置了一个集线器。

集线器也可像其他任何外设一样被隔离。只需在集线器芯片的上游端口放置一个 ADuM4160,即可创建隔离型集线器。这种配置可符合“两个集线器”的合规要求。该集线器芯片允许 ADuM4160 在全速模式下运行,同时保持与低速设备的兼容性。