串行端口接口

HMC960LP4E 提供一个四线串行端口,用于与主控制器进行简单通信。典型的串行端口操作可在 SCK 时钟频率高达 30 MHz 下运行。

关于 HMC960LP4E 的 SPI 访问细节将在以下章节中提供。请注意,下述 READ 操作之前必须始终先执行一次对寄存器 0 的 WRITE 操作,以定义要查询的寄存器。此外,请注意每个 READ 周期实际上也是一个 WRITE 周期——在读取数据的同时,发送到 SPI 的数据也会被存储到 HMC960LP4E 中(当 SEN 信号变高时)。如果不需要此行为,建议在 READ 操作期间向寄存器 0 写入数据,以确保器件状态不受影响。

上电复位与软复位

HMC960LP4E 电子元器件内置上电复位(POR)功能和可通过串行端口访问的软复位(SR)功能。

POR 在 HMC960LP4E 电源循环时触发;

SR 则通过 SPI 接口实现:先向寄存器 0h 写入 20h,再写入 00h。所有芯片寄存器将在上电后约 250 微秒内恢复至默认状态。

串行端口写操作

主机在 SCK 的下降沿改变数据,而 HMC960LP4E 在 SCK 的上升沿读取数据。

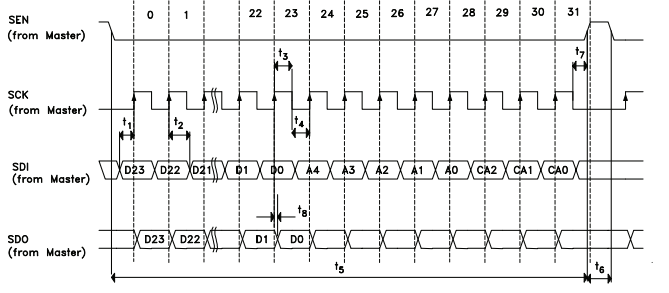

一个典型的 WRITE 周期如下图所示,共包含 32 个时钟周期:

主机同时拉低 SEN(低电平有效的串行端口使能信号),并将数据的最高有效位(MSB)置于 SDI 线上,随后在 SCK 上产生一个上升沿。

HMC960LP4E 在 SEN 之后的第一个 SCK 上升沿读取 SDI 上的 MSB。

HMC960LP4E 在接下来的 23 个 SCK 上升沿中依次接收 D23:D0 数据位(共 24 位数据)。

主机在接下来的 5 个 SCK 下降沿上放置 5 位寄存器地址 A4:A0(从 MSB 到 LSB),HMC960LP4E 在对应的 SCK 上升沿读取这些地址位。

主机在接下来的 3 个 SCK 下降沿上放置 3 位芯片地址 CA2:CA0 = [110](从 MSB 到 LSB)。注意:HMC960LP4E 的芯片地址固定为 “6d” 或 “110b”。

在第 32 个 SCK 上升沿之后,SEN 由低电平变为高电平,标志着 WRITE 周期完成。

HMC960LP4E 还会在 SDO 线上返回数据。