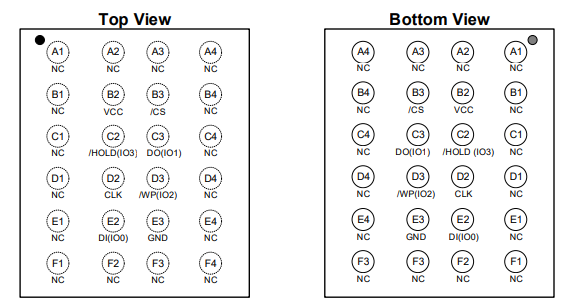

W25Q128JV串行NOR闪存引脚配置主要如下:

片选(CS)

SPI 片选(/CS)引脚用于使能和禁用器件操作。当 /CS 为高电平时,器件处于未选中状态,串行数据输出引脚(DO,或 IO0、IO1、IO2、IO3)呈高阻态。在未选中状态下,除非内部擦除、编程或写入状态寄存器周期正在进行中,否则器件功耗将保持在待机水平。当 /CS 被拉低时,器件被选中,功耗将上升至活动电平,指令可被写入,数据也可从器件读出。上电后,/CS 必须从高到低跳变一次,新指令才会被接受。/CS 输入必须在电源上电和掉电期间跟踪 VCC 供电电平。如有需要,可在 /CS 引脚上加一个上拉电阻以实现此功能。

串行数据输入、输出及 I/O 引脚(DI, DO 和 IO0, IO1, IO2, IO3)

W25Q128JV 支持标准 SPI、双路 SPI 和四路 SPI 操作。标准 SPI 指令使用单向 DI(输入)引脚,在串行时钟(CLK)输入引脚的上升沿将指令、地址或数据串行写入器件;同时使用单向 DO(输出)引脚,在 CLK 的下降沿从器件读取数据或状态。

双路和四路 SPI 指令使用双向 I/O 引脚,在 CLK 上升沿将指令、地址或数据串行写入器件,并在 CLK 下降沿从器件读取数据或状态。四路 SPI 指令需设置状态寄存器-2 中的非易失性四路使能位(QE)。当 QE=1 时,/WP 引脚变为 IO2,/HOLD 引脚变为 IO3。

写保护(/WP)

写保护(/WP)引脚可用于防止状态寄存器被写入。与状态寄存器的块保护位(CMP、SEC、TB、BP2、BP1 和 BP0)以及状态寄存器保护(SRP)位配合使用时,可对小至 4KB 扇区或整个内存阵列进行硬件写保护。/WP 引脚为低电平有效。

保持(/HOLD)

/HOLD 引脚允许器件在被选中时暂停操作。当 /HOLD 被拉低且 /CS 也为低时,DO 引脚呈高阻态,DI 和 CLK 引脚上的信号将被忽略(无关紧要)。当 /HOLD 被拉高时,器件操作恢复。/HOLD 功能在多个器件共享同一组 SPI 信号时非常有用。当状态寄存器-2 中的 QE 位设置为四路 I/O 模式时,/HOLD 引脚功能不可用,因为该引脚此时用作 IO3。

串行时钟(CLK)

SPI 串行时钟输入(CLK)引脚为串行输入和输出操作提供时序。

复位(/RESET)

SOIC-16 和 TFBGA 封装提供专用的硬件 /RESET 引脚。当该引脚被拉低至少约 1μs 时,器件将终止任何外部或内部操作,并返回其上电初始状态。

如有选型及采购需求,可直接联系兆亿微波电子元器件商城。