TPS53353 是一款具有集成 MOSFET 的 D-CAP™ 模式、20A 同步降压转换器。采用了 5mm × 6mm、22 引脚 QFN 封装,额定工作温度范围为 –40°C 至 85°C。在使用 TPS53353 进行 PCB 布局设计之前,必须考虑以下关键点:

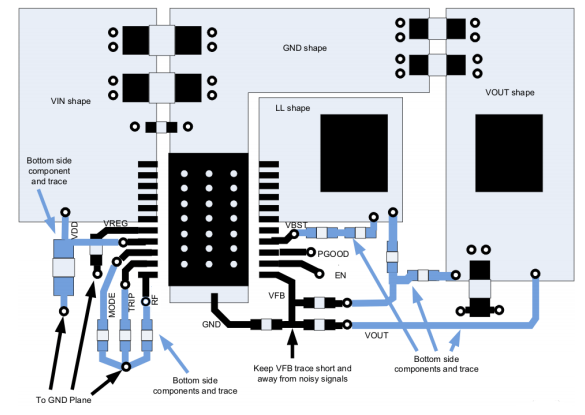

所有功率元件(包括输入/输出电容、电感以及 TPS53353 本身)应放置在 PCB 的同一侧(焊接面)。至少应插入一个内层平面并连接至地,以屏蔽和隔离小信号走线,避免其受到噪声电源线的干扰。

所有敏感模拟走线及元件(如 VFB、PGOOD、TRIP、MODE 和 RF)应远离高压开关节点(如 LL、VBST),以防耦合干扰。建议使用内部层作为接地平面,并将反馈走线从功率走线和元件处屏蔽开来。

VIN 去耦电容应尽可能靠近 VIN 和 PGND 引脚放置,以最小化输入交流电流环路。

由于 TPS53353 是参照 VOUT 电容两端电压来控制输出电压的,因此分压电阻的上端电阻应连接到 VOUT 电容的正极端;下端电阻的地应连接至器件的地。从这些电阻到 VFB 引脚的走线应短而细。

频率设定电阻(RF)、过流保护设定电阻(RTRIP)和模式设定电阻(RMODE)应尽可能靠近器件放置。如有条件,可通过公共地过孔将它们连接至地平面。

VDD 和 VREG 去耦电容应尽可能靠近器件放置。确保为每个去耦电容提供独立的地过孔,并尽量减小回路面积。

定义为开关节点的 PCB 走线(即连接 LL 引脚与电感高压端的走线)应尽可能短且宽。

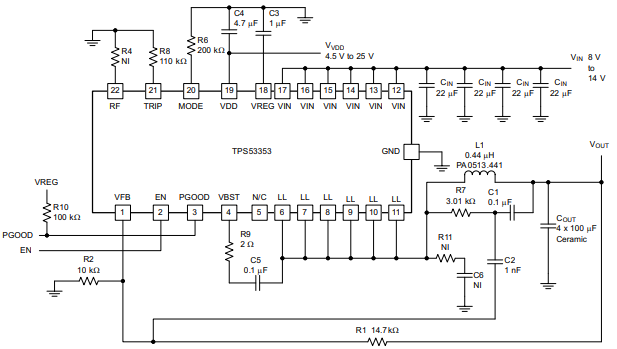

纹波注入 VOUT 信号(来自陶瓷输出电容 C1 的 VOUT 端 见文中图1)应从该电容端子引出。交流耦合电容(C2见文中图1)应靠近器件放置,R7 和 C1 可置于功率级附近。

应使用独立的过孔或走线将 LL 节点分别连接至缓冲电路、自举电容和纹波注入电阻。切勿将这些连接合并共用。

电子元件TPS53353布局示例图