W632GU6NB 是一款 2Gb DDR3L SDRAM,组织方式为 16,777,216 字 × 8 个 Bank × 16 位。

该器件可实现高达 2133 MT/s(DDR3L-2133)的高速数据传输速率,适用于多种应用。

本器件按以下速度等级分类:-09、-11、-12、-15、09I、11I、12I、15I、09J、11J、12J 和 15J。

-09、09I 和 09J 速度等级符合 DDR3-2133L (14-14-14) 规范:

09I 工业级保证支持 -40°C ≤ TCASE ≤ 95°C;

09J 工业增强级保证支持 -40°C ≤ TCASE ≤ 105°C。

-11、11I 和 11J 速度等级符合 DDR3L-1866 (13-13-13) 规范:

11I 工业级保证支持 -40°C ≤ TCASE ≤ 95°C;

11J 工业增强级保证支持 -40°C ≤ TCASE ≤ 105°C。

-12、12I 和 12J 速度等级符合 DDR3L-1600 (11-11-11) 规范:

12I 工业级保证支持 -40°C ≤ TCASE ≤ 95°C;

12J 工业增强级保证支持 -40°C ≤ TCASE ≤ 105°C。

-15、15I 和 15J 速度等级符合 DDR3L-1333 (9-9-9) 规范:

15I 工业级保证支持 -40°C ≤ TCASE ≤ 95°C;

15J 工业增强级保证支持 -40°C ≤ TCASE ≤ 105°C。

W632GU6NB 设计符合以下关键 DDR3L SDRAM 特性:

后置 CAS#;

可编程 CAS# 写入延迟(CWL);

ZQ 校准;

片上终端(ODT);

异步复位。

所有控制与地址输入均同步于一对外部提供的差分时钟。输入在差分时钟的交叉点锁存(CK 上升沿和 CK# 下降沿)。所有 I/O 均以源同步方式与差分 DQS-DQS# 对同步。

W632GU6NB电子元件具备哪些特征?

电源电压:典型值 1.35V(VDD),VDDQ = 1.283V 至 1.45V

向后兼容 VDD、VDDQ = 1.5V ± 0.075V

双倍数据率架构:每个时钟周期两次数据传输

八个内部 Bank,支持并发操作

8 位预取架构

CAS 延迟:5、6、7、8、9、10、11、13 和 14

突发长度 8(BL8)和突发截断 4(BC4)模式:可通过模式寄存器(MRS)固定或通过 On-The-Fly(OTF)选择

可编程读突发排序:交错式或半字节顺序式

双向差分数据选通信号(DQS 和 DQS#)随数据发送/接收

读数据边沿对齐,写数据中心对齐

DLL 使 DQ 和 DQS 转换与时钟对齐

差分时钟输入(CK 和 CK#)

命令在每个 CK 正边沿输入,数据和数据掩码参考差分数据选通对的两个边沿(双倍数据率)

后置 CAS,带可编程附加延迟(AL = 0、CL - 1 和 CL - 2),以提升命令、地址和数据总线效率

读延迟 = 附加延迟 + CAS 延迟(RL = AL + CL)

自动预充电操作,用于读写突发

刷新、自刷新、自动自刷新(ASR)和部分阵列自刷新(PASR)

预充电掉电和主动掉电模式

写数据的数据掩码(DM)

每工作频率可编程 CAS 写入延迟(CWL)

写入延迟 WL = AL + CWL

多用途寄存器(MPR),用于读取预设系统时序校准比特序列

通过写均衡和 MPR 读模式提供系统级时序校准支持

使用外部接地参考电阻进行输出驱动器和 ODT 的 ZQ 校准

异步 RESET# 引脚,用于上电初始化序列和复位功能

可编程片上终端(ODT),用于数据、数据掩码和差分选通对

动态 ODT 模式,提升信号完整性,并在写入期间预选终端阻抗

2K 字节页大小

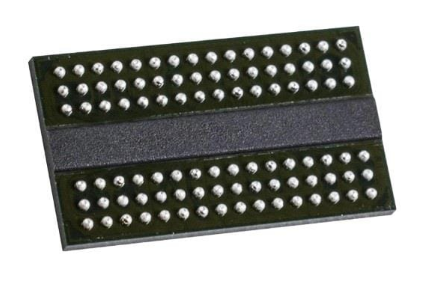

封装形式:VFBGA 96 球(7.5 x 13 mm²,厚度 1.0 mm),采用无铅材料,符合 RoHS 标准