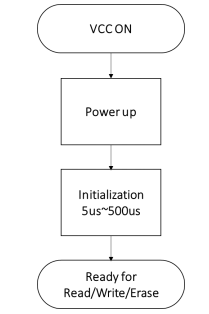

设备操作流程图

标准 SPI 指令

W25N02KV 通过一个兼容 SPI 的总线进行访问,该总线由四个信号组成:串行时钟(CLK)、片选(/CS)、串行数据输入(DI)和串行数据输出(DO)。标准 SPI 指令使用 DI 输入引脚,在 CLK 上升沿将指令、地址或数据串行写入器件;DO 输出引脚则用于在 CLK 下降沿从器件读取数据或状态信息。

支持 SPI 总线操作模式 0(0,0)和模式 3(1,1)。两者的主要区别在于当 SPI 主设备处于待机状态且未向 SpiNAND 传输数据时,CLK 信号的默认电平不同。对于模式 0,CLK 信号在 /CS 的下降沿和上升沿通常为低电平;而对于模式 3,CLK 信号在 /CS 的下降沿和上升沿通常为高电平。

双路 SPI 指令

W25N02KV 在使用如“快速读取双路输出(3Bh)”和“快速读取双路 I/O(BBh)”等指令时,支持双路 SPI 操作。这些指令允许数据以普通 QspiNAND 器件两到三倍的速度传入或传出器件。双路 SPI 读取指令非常适合在上电后快速将代码下载至 RAM(代码影子加载),或直接通过 SPI 总线执行非速度关键型代码(XIP)。在使用双路 SPI 指令时,DI 和 DO 引脚变为双向 I/O 引脚:IO0 和 IO1。

四路 SPI 指令

W25N02KV 电子元器件在使用如“快速读取四路输出(6Bh/6Ch)”、“快速读取四路 I/O(EBh/ECh)”以及“四路编程数据加载(32h/34h)”等指令时,支持四路 SPI 操作。这些指令允许数据以普通 SpiNAND 器件四到六倍的速度传入或传出器件。四路读取指令显著提升了随机访问传输速率,可实现快速的代码影子加载至 RAM 或直接通过 SPI 总线执行代码(XIP)。在使用四路 SPI 指令时,DI 和 DO 引脚变为双向 IO0 和 IO1,而 /WP 和 /HOLD 引脚则分别变为 IO2 和 IO3。

保持功能

在标准 SPI 和双路 SPI 操作中,/HOLD 信号允许 W25N02KV 在被选中期间(即 /CS 为低电平时)暂停操作。/HOLD 功能在 SPI 数据和时钟信号与其他器件共享的情况下非常有用。例如,若页缓冲区仅部分写入时发生需要占用 SPI 总线的高优先级中断,此时 /HOLD 功能可保存当前指令状态及缓冲区中的数据,待总线再次可用时从中断点恢复操作。

请注意:/HOLD 功能仅适用于标准 SPI 和双路 SPI 操作,不适用于四路 SPI 操作。当发出四路 SPI 命令时,/HOLD 引脚将作为专用 I/O 引脚(IO3)使用。

要启动 /HOLD 条件,必须先将器件选中(/CS 拉低)。如果 CLK 信号已为低电平,则 /HOLD 条件将在 /HOLD 信号的下降沿激活;若 CLK 尚未为低,则 /HOLD 条件将在下一个 CLK 下降沿激活。/HOLD 条件将在 /HOLD 信号的上升沿终止(前提是 CLK 已为低);若 CLK 尚未为低,则 /HOLD 条件将在下一个 CLK 下降沿终止。

在 /HOLD 条件下,串行数据输出(DO)呈高阻态,串行数据输入(DI)和串行时钟(CLK)将被忽略。在整个 /HOLD 操作期间,片选(/CS)信号应保持有效(低电平),以避免复位器件内部逻辑状态。