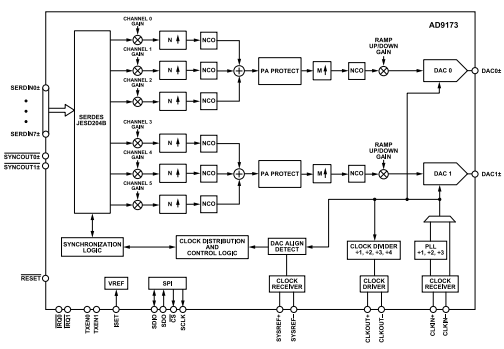

AD9173 是一款 16 位双通道射频数模转换器(DAC)电子元器件,配备高速 JESD204B SERDES 接口,符合子类 0 和子类 1 操作规范。

通过AD9173功能图可以看出:每个 DAC 核心包含三个可独立旁路的通道化器,支持每通道最高 1.54 GSPS 的复数据速率输入。八个高速串行链路以每通道最高 15.4 Gbps 的速率向通道数据路径传输数据。JESD204B 接口支持单链路和双链路工作模式,具体取决于所选模式配置。与 LVDS 或 CMOS 接口相比,SERDES 接口简化了引脚数量、电路板布局及器件输入时钟要求。

上图:AD9173功能图

输入数据的时钟源自 DAC 时钟或由设备时钟(根据 JESD204B 规范)提供。该设备时钟可由片上 PLL 生成的 DAC 参考时钟驱动,也可使用高保真度外部 DAC 采样时钟。器件可配置为每链路 1、2、3、4 或 8 线模式,具体取决于所需输入数据速率。

AD9173 的数字数据路径为通道数据路径和主数据路径均提供可选的 (1×) 插值模式。此外,根据所选模式,通道数据路径还支持 2×、3×、4×、6× 和 8× 插值选项;主数据路径则支持 2×、4×、6×、8× 和 12× 插值选项。

对于每个通道数字数据路径(当未使用 1× 通道插值时),均提供可编程增益级和 NCO 模块。NCO 模块具备 48 位模数 NCO 振荡器,可实现近乎无限精度的数字频率偏移信号处理。

NCO 可在纯 NCO 模式下独立运行,通过 SPI 接口输入可编程直流值,或通过 SERDES 接口与数字数据路径结合数字数据进行控制。在三个通道化数据路径末端,一个求和节点将三路通道数据路径合并,最高可达 1.54 GSPS,随后送入各自主 DAC 数据路径以进行进一步功能处理。

每个主 DAC 数据路径包含一个可选功率放大器(PA)保护模块、一个主数据路径插值模块、一个带可选模数特性的主 NCO,以及一个由 PA 保护模块馈送的斜坡上升/下降门控模块。此外,还提供一个可选校准音调功能,以及四个作为主 NCO 模块一部分的调制器开关模式。

AD9173 支持多芯片同步,既能同步多个 DAC,又能为 DAC 建立恒定且确定的延迟(延迟锁定)路径。每个 DAC 的延迟在链路建立至链路建立之间保持恒定,误差在数个 DAC 时钟周期内。外部对齐信号(SYSREF±)使 AD9173 符合 JESD204B 子类 1 规范。系统中可提供多种 SYSREF± 信号处理方式。

SPI 用于配置各个功能模块并监控其状态。各功能模块和数据接口必须按特定顺序设置以确保正常运行。