前言

围绕如何处理小信号前端这一话题,近期引起了一波讨论热潮。技术型分销商Excelpoint世健的FAE Wolfe Yu就小信号前端、确定测量范围、抑制噪声、提高信噪比等问题进行了介绍和分析。

运算放大器结构探秘

部分工程师强调理想运放的增益无穷大,分析运放,首先注意虚断和虚短,忽略了共模抑制比、失调电压、偏置电流等一些较为重要的概念。

一、运放输入模型

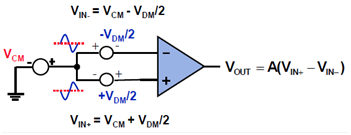

按照运放模型,比较全面的梳理出运放的基本模型:就是差模信号和共模信号的叠加。

二、虚短概念

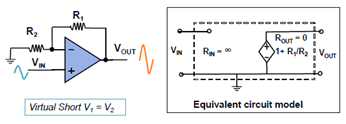

理想运放要注意虚断和虚短。运放的同相端输入和反相端输入相等。

理想运放开环增益无穷大,实际略小,大部分在100dB(100000)倍左右,按这个增益,要让输出变化3V,同相反相输入端只需30uV的压差即可,如果加上纹波、噪声等干扰信号,同相反相端基本上无变化。引入反馈,做闭环,同相反相端的电压差忽略不计。

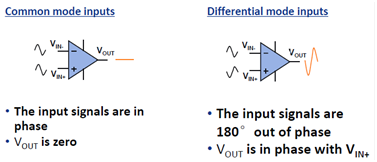

三、差模输入和共模输入

在应用中,运放可以输入差模信号,也可以输入共模信号,共模信号大部分来自噪声,最核心的愿景是:共模被抵消,差模被放大。

四、输入电压范围(Vin或Vcm)

运算放大器输入范围比较复杂,理论上来讲,同相端和反相端模拟输入在电源的正轨到负轨之间都能满足,运放的上下管大致对称,大部分时间,取运放的共模输入电压Vcm为1/2 Vdd。这样,运放主要工作在线性区。

五、小信号检测方法

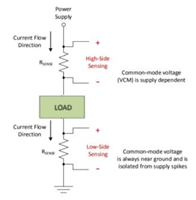

运算放大器用来做电流小信号采集时,往往会面临信号该如何采集、是采用高边电流检测还是采用低边电流检测的问题。

差分放大器介绍

由于传感器信号主要是通过施加电压差做为输出,信号的差值电压很小,而且会产生布局布线引起的EMI和共模干扰、温度漂移等问题。把运放的同相端和反相端当做车厢,只要传感器信号给定在这中间,相对的干扰就会小很多。传感器的信号存在压差,避免运放异常饱和,引入差分放大器。

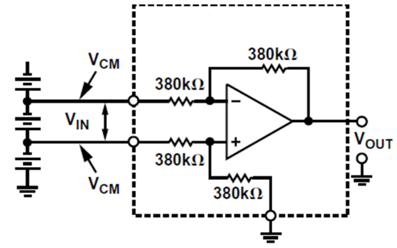

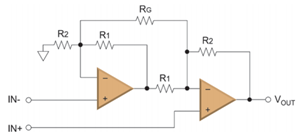

基于成本考虑,行业之内,大部分设计还会采用普通运放,基于减法器的模型,搭建一个差动放大器。

差分放大器的原理就像照镜子,物理学上的说法称作镜像,讲究对称和平衡,只有做到两边一模一样,效果才会最佳。为了这个目的,工程师就需要在模拟前端做阻抗匹配。而由于各点参考源不同,阻抗又有误差,完全阻抗匹配往往非常困难。下图是一个经典的差分运放,通过输出静默电压Uoz,用KCL去求解同相输入和反相输入阻抗,结果差异很大。

下面介绍一下确定上图中各电阻的值的方法:

首先,按照镜像原理,偏置电流也按照相同的倍数放大,即可求出4个电阻之间的关系;确定R1则需要查运放的几个限制条件,阻值需满足:大于瞬时输出电压/最大输出电流、小于输入失调电压/输入偏置电流,还要注意热噪声影响等等。

仪表放大器介绍

差分放大器能处理大部分模拟前端,但由于系统输入阻抗有限,需要加入复杂的匹配电路。当外围电阻精度和PCB线路阻抗,会产生新的问题。

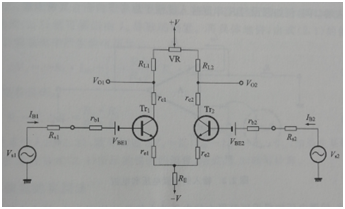

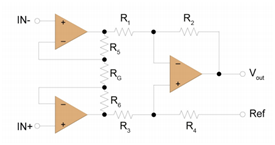

为了解决差分运放输入阻抗较低等问题,各大厂家做了很多优化,有的就采用如下图的双运放方法来实现仪表放大。

双运放有两个弱点:不支持单位增益、不同频率的共模抑制比较差。于是众多厂商采用三运放方法。不少大厂推出的仪表放大器,也都是基于三运放原理来实现的。

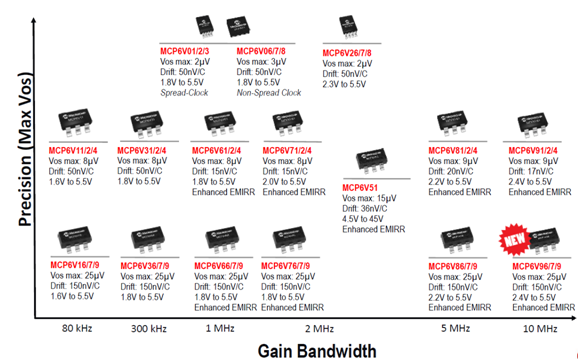

Microchip运放解决方案

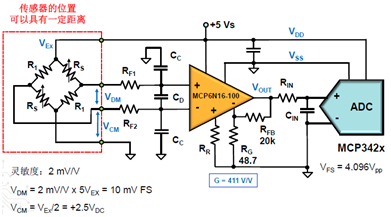

仪表放大器 MCP6N16-100

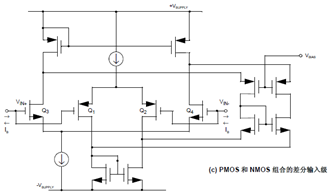

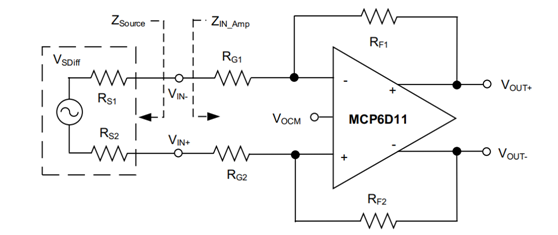

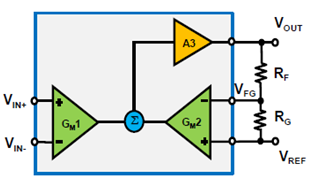

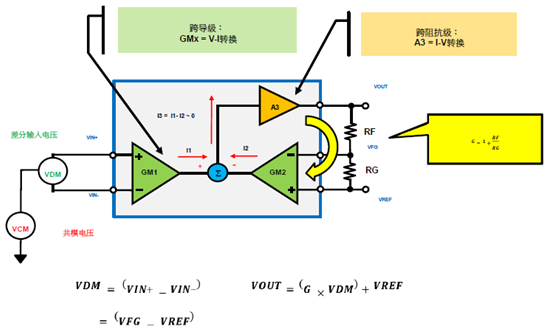

不同于众多厂商推出的三运放仪表放大器方案,Microchip针对工业客户应用提出了自己独特的解决方案——间接电流反馈型仪表放大器,其内部结构如下图所示:

间接电流反馈型仪表放大器前级做跨导放大,实现V-I转换,后级做跨阻放大I-V转换。

间接电流反馈型仪表放大器和三运放仪表放大器存在一些差别,主要优势:

üq在宽Vcm范围内具有高CMRR(轨到轨)

üq工作区域广(Vin和Vout)

üq适合低电压应用

üq无“Hex”图

üq高阻态Vref输入

üq更好的增益温度系数匹配

应用案例——惠斯通桥

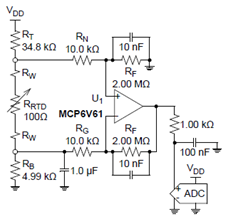

零漂移放大器 MCP6V61

另外,Microchip的零漂移放大器产品,主要针对较低成本应用,主要特点:

高直流精度

- VOS 漂移: ±15 nV/°C

- AOL: 125 dB

- PSRR: 117 dB

- CMRR: 120 dB

- (EMIRR) at 1.8 GHz: 101 dB

- 低功耗

- 静态电流80uA

应用案例——RTD传感器

Wolfe表示,Microchip还推出了多款有特色的运放产品,比如低噪声、高精度、全差分系列的MCP6D11、高边电流检测系列MCP6C04等。