静电放电 (ESD) 现象从一开始就存在。我们第一次接触 ESD 往往是在孩童时代,在干燥的冬日触碰金属门把手时,会有种触电的感觉——这就是静电放电。这种短暂的不适感通常对人类来说不是问题,但是即使是少量的 ESD 也有可能会损毁敏感电路。

手机设计人员一直都面临着何时以及如何解决这一自然现象的挑战。本博客解释了系统级 ESD 保护为何如此重要,同时使大家能够了解提高移动设备中系统级 ESD 保护的测试模型和战略。

ESD 模型和波形的测试

人体和衣服一天可存储 500 V 至 2,500 V 静电电荷,但是人类只能感受到 3,000 至 4,000 V 的 ESD 脉冲。这远高于电子电路受损的水平,即使人类无法检测到。

设计人员必须从多方面解决 ESD 问题,对组件制造商来说,是在其设计阶段和设计工作结束之时。简而言之,ESD 保护需要一种多层面方案。

通常,集成电路 (IC) 制造商按照 ESD 行业标准设计、测试和验证其 IC。这可防止在 IC 生产或在 PC 板上组装时出现物理损坏。针对 ESD,通常进行的两种测试包括:

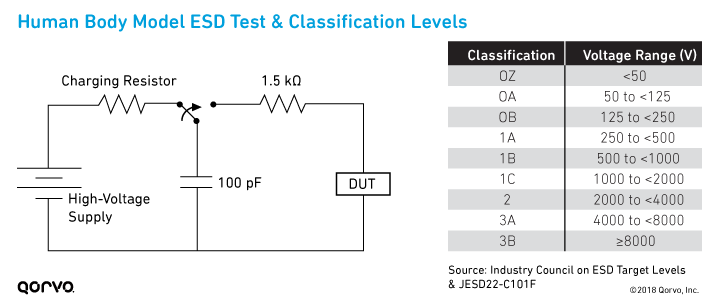

● 人体模型 (HBM)。这种测试模拟人体通过接触 IC 释放所积累的静电的 ESD 事件。采用一个带电的 100 pF 电容和一个 1.5 k? 放电电阻进行模拟。

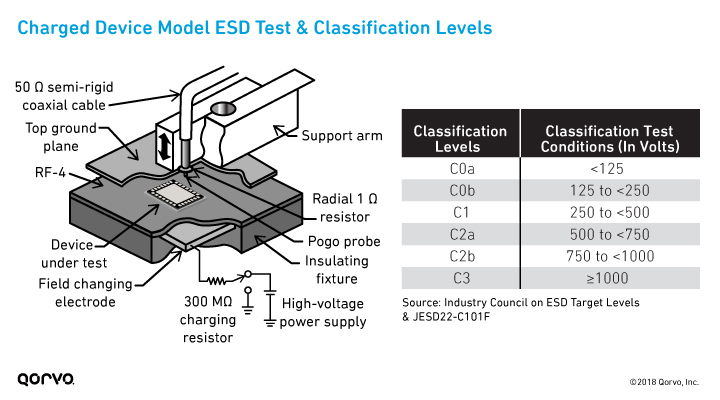

● 带电设备模型 (CDM)。这种测试模拟在生产设备和工艺中发生的充电和放电事件。设备在一些摩擦工艺中或静电感应过程中获得电荷,然后突然接触到一个接地物体或表面。

虽然设备级测试有助于衡量 IC 的 ESD 稳健性,但系统级测试可衡量现场的电子设备保护(即原始设备制造商 [OEM] 设备或终端产品)。

为了更好地了解最终产品所需的 ESD 保护,OEM 应采用系统级 ESD 方法进行设计,然后按照国际电工委员会 (IEC) ESD 标准 61000-4-2 测试最终产品。IEC 61000-4-2 被视为终端产品 ESD 测试和评级的行业标准。该测试可确定系统对现场外部 ESD 事件的易损性。

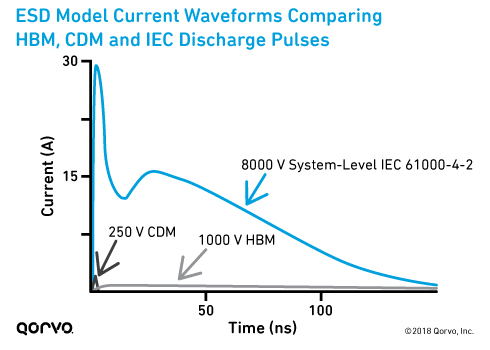

下图比较了三种脉冲的能量和峰值电流:

● 系统级 IEC 61000-4-2

● 设备级 HBM

● 设备级 CDM

IEC ESD 事件脉冲显然更强,因此系统中的设备更加难以通过。尽管设备级测试(HBM 和 CDM)比较有用,且可提供 ESD 稳健性的基准,但在系统级 IEC 测试期间并不总是能够确定生存性。

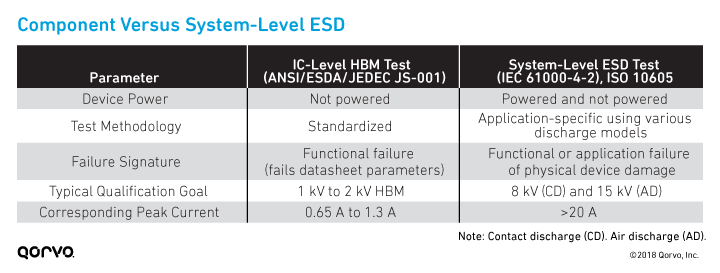

为进一步展示这一概念,下表显示了组件测试和系统级 IEC 测试之间的差异。大家可以看到,差异很大,系统应力水平更高。总而言之:较之于设备级设计,系统设计必须满足更严苛的要求。

测试不充分的问题

在开发阶段进行系统级 ESD 测试可能会是个问题。例如,测试评估/不完整板组件上的 ESD 并不能代表所有情况。这些组件的结果并不保证完整系统的最终结果。

设备级 ESD 测试(即 HBM 和 CDM)旨在通过适当的 ESD 控制在工厂生成适合分立式组件的可重复且可再现的结果。这就是所谓的 ESD 保护区 (EPA)。然而,这些测试并不是为了解决现实世界中 EPA 范围之外的全部产品级 ESD 事件。

实现产品稳健性的关键:系统级 ESD

相反,ESD 稳健型系统设计的关键是要考虑 ESD 在系统中的影响。为了获得系统级视角,设计人员必须了解并解决以下问题:

● 系统级应力事件及其对整个产品的影响。设备级 ESD 测试结果只能为系统 ESD 设计提供非常少的信息,因为它们无法反映电子设备在 IEC ESD 事件期间经历了什么。

● 系统中板级相互作用,以及在 ESD 应力作用下与电子部件外部接触的引脚瞬态行为。

● 高效的表征化方法(如组件级传输线路脉冲 (TLP) 数据),用于分析 IC、板和系统的相互作用。

系统级 ESD 保护战略取决于物理设计、产品要求和产品成本。

最佳方法:系统高效 ESD 设计 (SEED)

系统高效 ESD 设计 (SEED)是一种系统级方法,考虑了系统中所有组件的瞬态响应。SEED 方法还包括对 IC 引脚上 PC 板外部端口施加的 IEC 应力的物理影响。

SEED 是一种实现板载和片上 ESD 保护的协同设计方法。利用 SEED,您可以分析和实现系统级 ESD 稳健性。该方法要求对 ESD 应力事件期间外部 ESD 脉冲之间的相互作用、完整的系统级板设计以及设备引脚特性有一个全面的了解。

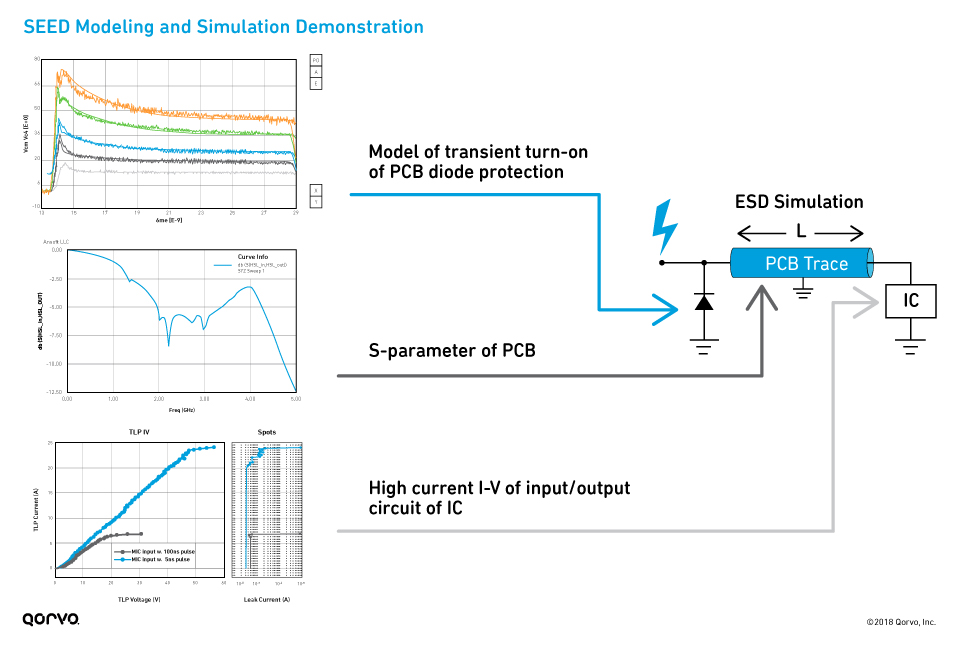

SEED 方法是实现对称且稳健的系统级 ESD 保护的最佳方法。如下图所示,SEED 利用以下信息设计系统级 ESD 保护:

● 准静态 TLP 电流电压 (I-V) 曲线数据

● 瞬态模拟

● S 参数 PC 板数据

● IC I-V 电路测量

我们将在本博客系列的第 2 部分和第 3 部分详细介绍 SEED。这一部分主要是对 SEED 进行概述:

● PC 板的 ESD 保护为一级保护,可防止对 IC 或系统造成物理损坏。

● 片上保护发挥二级保护的作用。

SEED 的基本概念旨在防止具有损坏性质的 ESD 脉冲抵达内部 IC 引脚。通过执行和分析 ESD 系统级模拟可实现适当的系统级 ESD 设计。

接下来:RF 前端设计的 ESD 保护战略

众所周知,在手机设计中战略性地实现 ESD 至关重要。这样做可缩短设计工程周期时间,减少 ESD 故障和研发开支。

在本博客系列的后续博客中,我们将深入探讨 ESD 保护组件以及减少 ESD 对移动 RF 设计影响的不同战略。第 3 部分将解释如何利用模拟和建模确定系统级 ESD 保护。