开关稳压器电路已经存在多年,用户可以选择使用分立式组件来设计自己的产品,也可以购买模块化成品。如今,能够满足最新的效率、EMI和功率密度要求的技术让模块化方案获得更多的青睐。

长期以来,无论是直接用于负载还是作为分布式电源架构的一部分,非隔离式开关稳压器一直是有效地将直流电源轨转换为较低或较高电压的主力。1950年代的第一批设计使用了真空管,与替代的“线性稳压器”相比转换效率显著提高,同时还开辟了提高直流电压的可能性,而这在以前只有靠笨重的机械振动器才能实现。直到1970年代才出现了第一个使用 “电压模式” 控制的开关电源IC控制芯片Silicon General SG1524。它的成功为使用不同控制和转换技术的替代选择开启了新的大门。随着几十年的发展,双极型晶体管和二极管虽然目前还在广泛的应用中,但将来被MOSFET及MOSFET同步整流器取代已成趋势,即使是现在的Si-FET也受到SiC和GaN等宽带隙材料的威胁。

转换效率是衡量开关稳压器发展的一个标准。多年来,这个数字一直在稳步攀升,从80%提高到97%,在最新的设计中转换效率甚至高于97%。更高的效率代表更高的功率密度,以瓦特/cm3为单位,可以得知设计中给定体积的组件能够提供多少功率。规格书中标出的功率密度越来越高,其中某些有一定程度的“创造性”。例如,一些IC稳压器标榜的数据并没有将所有必要的外部组件考虑在内,尤其是体积较大的电感和电容。冷却通常也是一个问题,只有通过几乎不可实现的空气流速或过于复杂的水冷却才能达到惊人的功率密度。环境工作温度范围也同样重要,不仅是散热片温度,如果部件在一定室温以上必须大幅降额工作,这会直接降低有用功率。

最先进的开关稳压器发展现状s

非隔离式开关稳压器的发展也是组件集成在效率和功能性上不断提高和发展的历史。由于负载要求已从5V降到3.3V,之后降至现在的1V以下,因此输出电压不断降低。随着输入电压增加,系统功率也跟着增加,从而需要更高的总线电压以及更低的电流消耗。IC控制芯片简化了分立式组件的设计,其中控制器集成了开关晶体管和磁性组件。外围功能如故障监视、电流共享、同步和排序越来越广泛运用在IC设计中

从早期开关稳压器设计时供应商就已开始销售完整封装的转换器模块,在提供有效解决方案的同时协助客户节省自行设计的工作量和风险。但有时很难推广,因为经验丰富的工程师不愿出高价购买自己就可以设计的产品。对于销售多年的产品而言,即使有来自内部的设计时间问题和相关风险也是可以容忍的,多年的销售足以支付几倍的研发成本。另外从头开始设计开关电源所带来的成就感也是一部分原因。

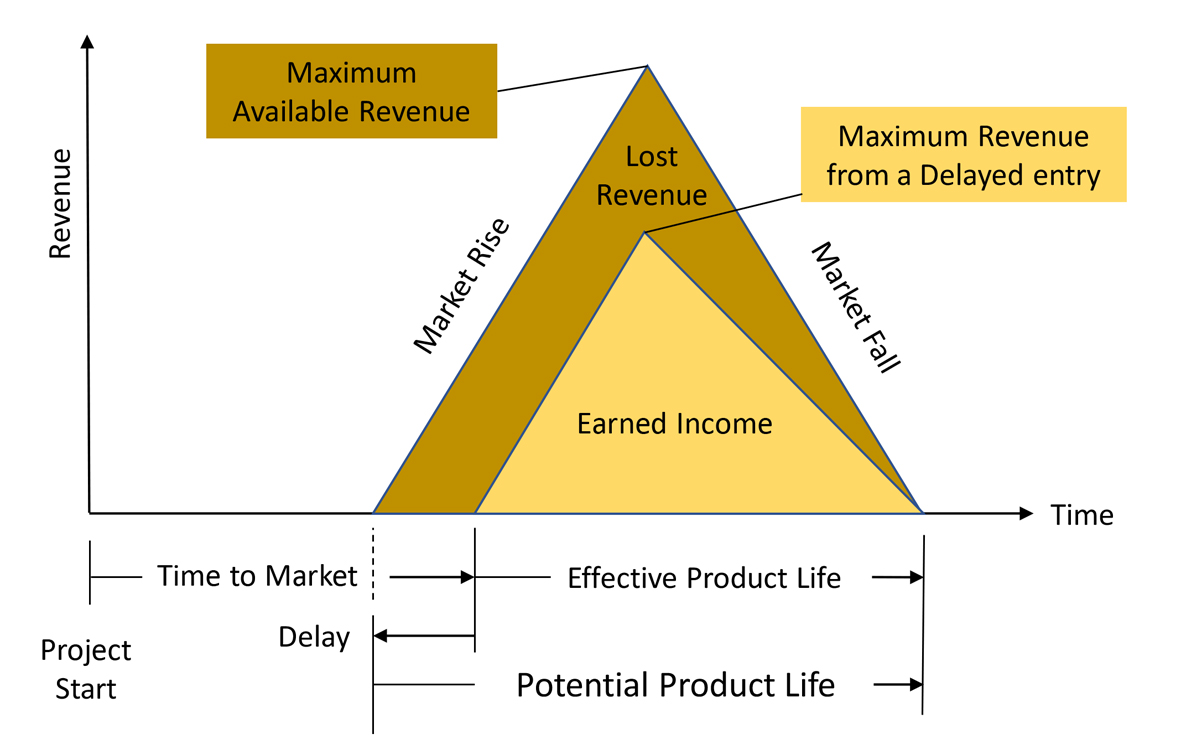

现在的情况有所不同,原始设备制造商(OEM)并不具备电源设计方面的专业知识,而且达到最佳性能所需的技术可能非常专业,甚至涉及到OEM可能无法提供的工艺,例如铁氧体材料的成型。 除此之外,产品生命周期也变的更短,这意味着开发成本以及设计优化或重复的EMC测试导致的延误对投资回报的影响更大(图1)。

图1:产品延迟推出等于损失收入

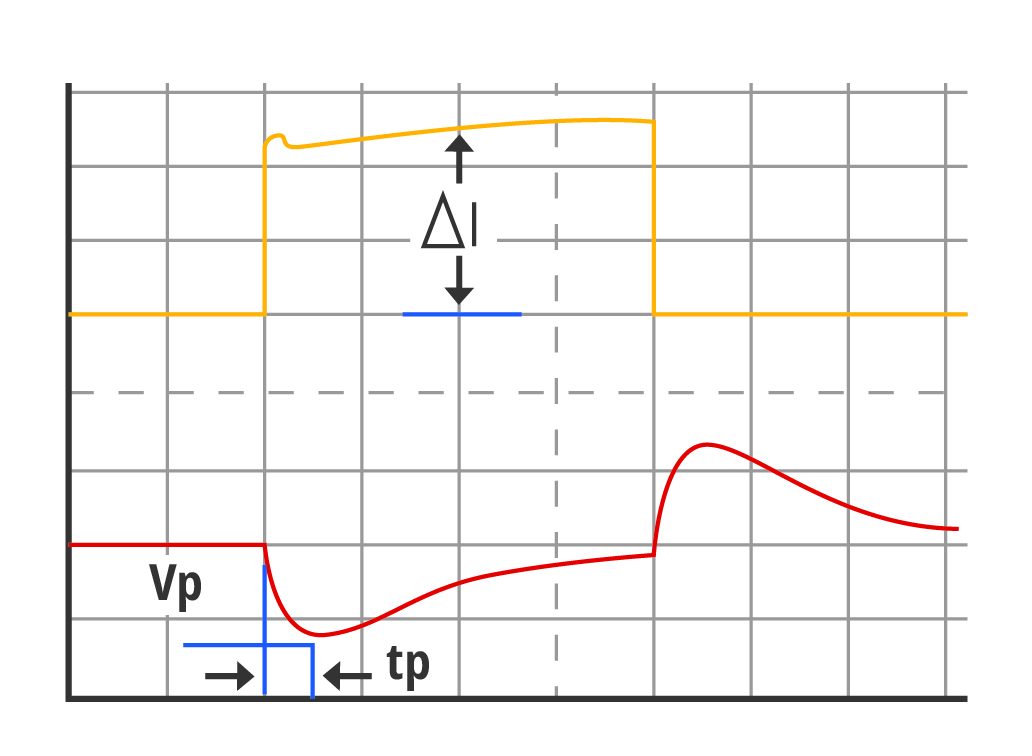

当然,控制IC制造商确实提供了各种方面的应用信息让设计看起来很容易,但是这些简化的设计工具无法预测实际的电路要求。例如,建议的输出电容通常太低不足以应对现实生活中的动态负载,动态负载可能在激活和睡眠状态之间的摆动幅度达到一百万倍,产生不可接受的电压跳变(图2)。

图2:降压转换器的负载阶跃导致电压瞬变

应用指南里的电感器通常也会被加以“粉饰”,建议使用的部件是为了获得最佳性能而不考虑价格和实用性。事实上,选择最佳电感可能需要花费数周来评估温度、频率和负载电流(静态和动态)的性能。其他参数,例如电感的饱和特性和漏磁场在设计中可能非常重要。完整设计的EMC性能是一个 “庞大的未知数” 直到最终PCB布好电路并选择了最终组件才能得知,而此时更改成本会很高。电容器也有类似的情况,通常无法从规格书中获得重要信息来进行评估(如自感),所以很难在错综复杂的性能和成本关系之间选出最佳零件。

目前,最先进的开关稳压器设计是通过控制IC来实现高功率密度,这些控制IC通常是BGA封装,尺寸仅2mm x 2mm,焊盘矩阵的间距只有0.4mm。这可能不适合用户的PCB组装工艺,因为需要精准的印锡和昂贵的X射线成像以检查短路或不良焊点。同样地,转换器控制IC可能需要一个复杂的多层PCB,具有通向接地平面的填孔和埋孔以有效地将热量从封装散发到电路板。即使用户在其他电路中不需使用到这种复杂的PCB,还是需要支付PCB制造成本。

最新的开关稳压器用途广泛

有些人会主张电源模块必须是通用的而不应成为某种应用的最佳方案,RECOM最新一代的产品就能够在各种工作条件下实现高性能。例如RECOM的0.5A RPMH系列,输入电压范围高达65V,输出电压范围2.5V至28V可调。 这些性能全部都整合在12.19mm x 12.19mm x 3.75mm的EMI屏蔽封装之中,无需强制风冷即可在高达105°C的温度下工作(图3)。具有相同封装且较高输出电流3A的RPMB系列产品可在高达36V的输入电压下工作,输出范围1V至24V可调。同类型具有6A输出电流的RPM系列,其最大输入电压较低,并采用相同的封装尺寸。

图3:12.19mm x 12.19mm x 3.75mm封装的6A开关稳压器(RECOM RPM系列)

由于这些模块已高度集成,因此增加一系列控制和监视功能(例如开/关控制、遥感、远端反馈、软启动、电源良好信号和上电排序)也不会增加太多制造成本。这些模块具有常规故障保护功能以防止输入欠压、短路、过电流和过热。在不同的睡眠或满负载条件下,应用程序可以从几乎零电流到额定最大值之间运行,因此模块通常会采用诸如多相转换器拓扑的切相技术来最大程度地降低轻载功耗并提升效率。

RECOM的电源模块将使用先进的生产技术来获得最高的功率密度,例如带有包覆成型的引线框倒装芯片技术。以RECOM RPX系列(图4)为例,采用4.5mm x 4mm x 2mm QFN封装,可达2.5A额定电流,而某些部件无需强制风冷,满载时的额定工作温度高达95°C。以RPX系列为例,该部件需要外部电容才能发挥最大性能。其实这可以帮助提高整体功率密度,例如,电源可能已具有输入电容,因此可以选择输出电容来达到所需的额定电压。如果电容是在内部的,那么尺寸必须增加,额定电压为修调后最大电压。

图4:4.5 x 4 x 2mm QFN封装2.5A开关稳压器(RECOM RPX系列)

板载稳压器通常需要兼具升压和降压的功能。一般应用在电池供电的设备上,需要在电池放电时尽可能长时间的保持电力。如果要从正输入得到正输出电压,传统的解决方法是使用SEPIC、ZETA或Cuk转换器,它们都需要两个磁性组件以及复杂的控制回路。随着集成度的提高,模块化转换器能以低成本实现不同的拓扑结构,例如四开关升降压,事实上这是一组可以“实时”配置为开关或二极管的MOSFET,在降压和升压模式之间无缝切换。以RECOM RBB系列为例,它采用LGA封装,额定电流为3A,半砖封装的3kW模块具有9V至60V的输入以及0V至60V的输出电压。通常应用在48V转24V或12V转24V的电池电源转换、电动汽车、电池稳压器或实验室大功率直流电源。

要模块还是 “DIY” 显而易见

采购一个结合所有工艺和设计技术来达到最佳性能的开关稳压器模块,不但可以降低产品开发风险还能够节省用户宝贵的时间和金钱。同面对不同组件的供应商相比,采购、仓储和处理一种组件,在供应商和库存管理方面将更加节省成本,如果需要最佳性能,甚至可以包括定制的磁性组件。这也可以节省SMD置件以及测试时间;对于某些必要的情况,也能够节省认证机构核准的时间与成本。另外,这还解决了替代产品的问题,因为越来越多模块的功能和引脚排列符合工业标准如DOSA。在计算总成本时,RECOM提供的模块化解决方案定会大获全胜:您不用再做这些工作了,因为我们已经帮您完成!

来源:RECOM