无线服务不断增长的需求不仅对我们有限的频谱资源构成挑战,还让无线电设计人员难以选择正确的无线电架构。合适的无线电架构不仅能提供可靠的性能,而且能简化无线电周围的电路,从而较大幅度地缩减成本、功耗和尺寸。在无线电部署不断增加的时代,满足需求的无线电应能容忍当前和未来的无线共存,否则这些无线共存可能会造成一连串干扰。本文将研究两种常见无线电架构,并且比较每种架构在解决日益增多的无线电站点共存问题这一独特挑战方面的优劣。

日益增长的挑战——新的无线邻居

无线革命开始于大约30年前,当时只有少数几个频段,并且大部分限制在900 MHz以下,通常每个国家和地区有一个频段。随着无线服务需求的增长,新频段不断增加,现在全球单独为5G NR就分配了49个频段,这还不包括毫米波分配。大多数较新的频谱都在2.1 GHz以上,频段覆盖500 MHz (n78)、775 MHz (n46)、900 MHz (n77)和多达1200 MHz (n96)。

随着这些新频段上线,一大挑战是如何在传统频段中有阻塞的情况下确保接收机具有足够的性能。这主要来自部署位置的共站要求,在美国使用频段2、4和7,在其他地区使用频段1和3。这对于服务于n48 (CBRS)以及n77或n78的任何部分中的应用的宽带无线电尤其关键。

未来无线需求将继续增长,共存和干扰的挑战始终存在。

无线电设计与射频保护和选择性

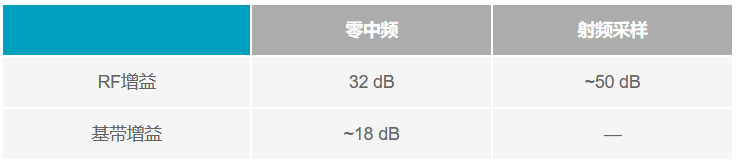

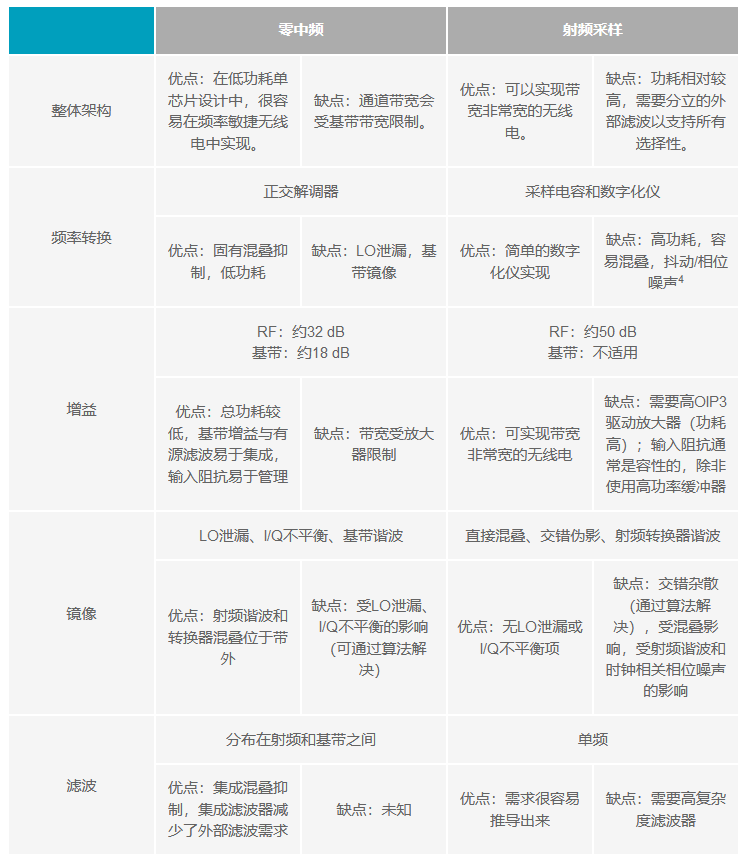

接收机设计的主要挑战之一是保护其不受干扰信号影响。从一开始,无线电工程师就寻求不同的方法来实现这一点,最初是使用简单粗暴的滤波,后来使用各种带分布式滤波的外差技术。经过多年发展,业界开发出三种主要架构来应对这些挑战:直接变频(零中频)、超外差(IF)和直接射频采样。虽然中频采样很流行,但它不是本文的重点。本文将着重比较射频采样和零中频,因为它们是目前无线领域中非常先进的实现方式。每种技术都会引入不同的工程权衡,对周围电路及其要求的影响也不同,这包括频率转换的方法、射频和基带增益的数量、射频镜像的处理方式以及滤波的实现方式和位置。这些权衡的详细信息如表2所示。

增益分布和功耗

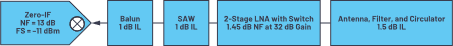

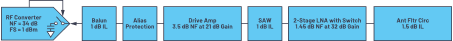

射频采样和零中频在增益分配上有关键区别。如图2所示,射频采样将所有增益都放在射频域中,因为在处理信号时,无线电中的所有频率都保持不变。为了进行比较,图1显示了一个零中频架构。对于此架构,部分增益位于射频频率,但平衡是在频率转换后的基带。

图1. 典型零中频信号链

图2. 典型射频采样信号链

两种架构都需要权衡取舍。从增益角度看,由于需要更高的压摆率,较高频率下的增益比较低频率下需要更多DC,尤其是当信号链中的信号逐渐变大时。这意味着与零中频相比,射频采样架构在线性射频部分(很大一部分增益位于DC)会消耗更多的功率。在较低频率下,压摆率较低,因此待机电流可以相应地减少。

射频采样面临的挑战是需要在高频和相对较高电压(~1 V)下驱动大部分是容性的输入(采样电容)。相比之下,零中频输入是表现良好的50 Ω(或100 Ω)电阻,其进入基带放大器的求和节点;放大器提供增益,消除采样节点并将其与射频信号隔离,减少所提供增益要求的射频驱动。这对线性射频部分的功耗具有深远的影响,因为它通过消除第三射频增益级而将总射频功耗降低25%到50%,有利于零中频架构,而且基带所需的待机电流低于射频放大。

除了线性功耗之外,还有与数字化相关的功耗。使用零中频转换器时,只需对所需带宽进行数字化。使用射频采样时,不仅宽射频带宽需要数字化,而且采样速率远远超过奈奎斯特要求。与带宽和采样速率相关的功耗都很高。确切的功耗取决于工艺,但采用相同的工艺实现时,对于典型的单频段应用,射频转换器的功耗比基带转换器高出大约125%。即使射频转换器可以对两个频段进行数字化,功耗仍然要高出40%。

表1. 不同架构中的增益分布

镜像和杂散信号

这些方案还有次要权衡因素。例如,零中频会引入LO泄漏和I/Q不匹配镜像项,而射频采样会因为转换器架构内的不匹配而引入交织杂散,以及转换器中的射频谐波和采样相关的抖动项。好消息是,无论架构如何,大多数镜像和杂散信号都可以通过各种背景算法得到解决。

这两种架构具有截然不同的频率规划,这会影响处理混叠的方式以及必须应用多少射频(外部)滤波。除了架构杂散信号之外,所有无线电都会产生射频谐波并受到混叠影响。如果所需信号自然地位于第一奈奎斯特区之外,则射频采样无线电可利用混叠对所需信号进行下变频。然而,问题一般出在干扰信号的响应上,因为混叠之后,它可能会意外落在所需信号之上。这些信号必须通过细致的频率规划、高抑制度的射频滤波或足够高的采样速率(此时无混叠)来消除。每种措施都有利弊,需要慎重权衡。

零中频架构将信号转换为基带(接近DC)。虽然肯定会产生射频谐波,但其在所有情况下都远离基带,并被典型零中频输入结构(下文会提到)的低通响应充分滤波。类似地,所使用基带采样器的相对较高采样速率和同样的输入结构也会环境混叠。

零中频滤波器要求

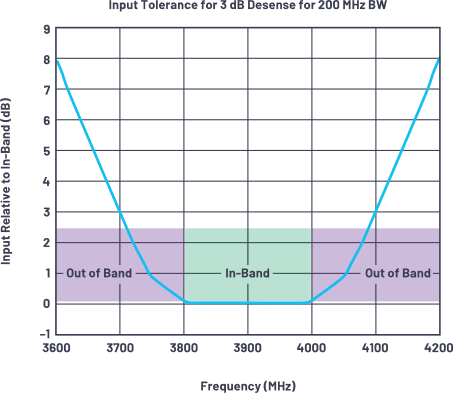

零中频架构的一个很容易被忽视的特性是,基带输入放大器通常构造为一个有源低通滤波器,其作为集成模拟滤波器运行,这大大减轻了模拟滤波器的负担。结合片内抽取滤波,它还能用作可编程通道滤波器,消除比奈奎斯特相关信号更近的信号。此外,零中频接收机内的采样器件通常包括反馈,可提供额外的带外抑制。实际上,这意味着无线电的带外区域比带内区域具有更大的满量程范围。正如AN-1354文章中所述以及图3中的简化图所示,零中频无线电本质上对带外信号具有良好的容忍度。图3中的纵轴表示相对于带内的会导致灵敏度下降3 dB的输入功率水平,它表明带内信号本身对带外信号具有容忍度,这是其他架构所没有的。

图3. 片内零中频滤波影响的示例

由于这种内置滤波,主要问题变成对射频前端(即LNA)的保护。对于FDD和某些TDD,典型配置是在第一级和第二级LNA之间使用一个SAW滤波器。有些TDD应用将SAW滤波器放在第二级之后,但第二级在大输入条件下是可旁路的,如图1所示。通常,SAW滤波器会提供大约25 dB的带外抑制,这里假设如此。除了SAW滤波器外,LNA的天线侧还需要一个与发射机共用的腔体滤波器。

典型的LNA可能具有–12 dBm的输入1 dB压缩点。如果带外或共存要求为16 dBm,则必须将这些干扰信号滤波到比LNA的输入1 dB压缩点低约10 dB(或更多)的程度。抑制最低值为38 dB (+16 – –12 + 10)。加上SAW滤波器,零中频的输入端呈现的总带外抑制为63 dB。假设射频增益不滚降,并且算上到内核无线电输入的总滤波抑制,最大带外信号水平将为–20 dBm。这远低于典型的满量程,而且还会被前面说明过的片内滤波进一步衰减。与图3相比,该输入电平不会导致杂散信号或灵敏度下降。

射频采样滤波器要求

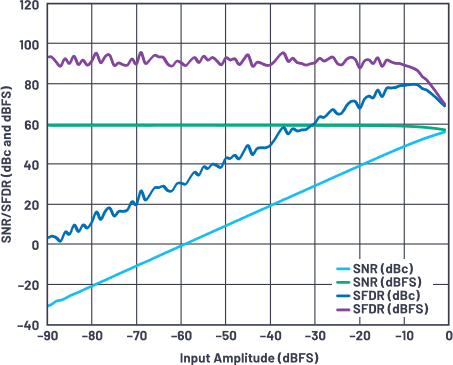

使用需要直接关注滤波的射频转换器架构时,有两个问题需要注意。首先,无论输入电平如何,任何信号都可能产生不需要的杂散信号,杂散信号可能占用与目标信号相同的频率。与交织相关的杂散通过算法处理,但架构杂散是另一个问题,因为这种杂散可能无法预测。对于许多较旧的射频转换器,这是对无线电性能的持续挑战。幸运的是,许多新型转换器包含某种形式的背景扰动,可以缓解这些问题并呈现相对干净的SFDR扫描,如图4所示。

图4. 带扰动的转换器示例

表2. 架构之间的工程权衡

在该SFDR与输入电平的关系曲线中,值得注意的是,由于转换器中的压摆率限制,前15 dB显示出恶化,这通常会产生很强的第二和第三谐波,必须予以消减。一旦射频输入低于此电平,谐波和架构杂散通常就不再是问题(请检查转换器性能以验证)。对于1 dBm的满量程,可以预期,当进入转换器的带外信号被抑制到-14 dBm以下时,杂散信号将显著减少。对于50 dB的转换增益,如表2所示,这相当于天线的-64 dBm。如果输入可能为16 dBm,则对于无混叠情况,射频滤波需要为80 dB或更多。假设SAW滤波器提供25 dB,那么腔体滤波器需要提供55 dB才能充分保护射频ADC,避免因带外信号而产生非线性,并且保护第一级LNA的输入,防止其被带外信号驱动成非线性状态。此例代表一个表现良好的转换器,但应仔细检查所选择的转换器的SFDR与输入电平的关系,以确定是否需要更多滤波。

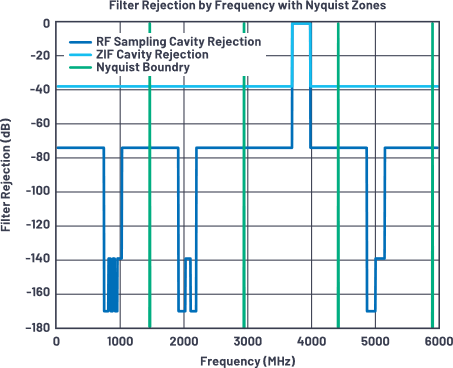

基于当前商用芯片的射频转换器架构还有一个值得担忧的问题,那就是混叠保护。当前射频转换器基于工作速率在3 GSP到6 GSP之间的内核。在这些较低速率下,若不使用高抑制度的滤波来减轻混叠的影响,就不可能避免混叠项。只有采样速率达到两位数的GHz,此问题才会减轻。

为了考虑混叠对滤波器要求的影响,一种简化办法是考虑对单个源元件的保护,避免混叠16 dBm的共站要求。目标是将干扰信号抑制到一定程度,使其混叠到所需的RB也不会影响性能;应对其充分滤波,防止发生任何负面影响。在大约0 dB SNR时,基于G-FR1-A1-4信号的广域参考通道的信号电平将为每RB -118.6dBm。因此,必须通过滤波将滋扰信号降低10 dB至15 dB,或约-130 dBm,以防止影响性能。这样,总抑制需求约为150 dB,其中腔体滤波器需要提供大约125 dB,SAW滤波器提供其余的滤波。

滤波器总结

图5显示了射频采样和零中频的腔体滤波器要求。由于射频采样架构具有两个独立的要求,因此限制最严的要求占据主导地位,可实现的滤波器只需满足最严格或125 dB的抑制以覆盖整个频段。虽然这种滤波很容易获得,但不利的一面是滤波器尺寸很大。相比之下,零中频架构仅需要40 dB的抑制,使用一个4腔体滤波器就能实现这种性能,因此重量和尺寸显著减小。

图5. 腔体滤波器要求

结论

总之,零中频和射频采样架构都能提供出色的能力。然而,如果目标是优化成本、重量和尺寸,那么零中频架构在多个方面胜出。从功耗角度看,集成了大部分模拟增益的零中频架构具有令人信服的节电效果。同样,当考虑滤波的影响时,零中频也有显著降低滤波要求的潜力。虽然滤波器的成本差异可能很小,但根据所需腔体的数量,这些滤波器的尺寸和重量减少应会超过50%。